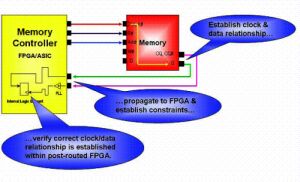

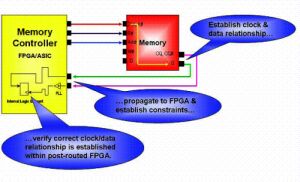

FPGA的設計與高速接口技術可以幫助你滿足今天的市場要求,,但也提出了一些有趣的設計挑戰(zhàn)。為了確保存儲器接口的數據傳輸準確,,在超過200兆赫茲以上,進行時序分析將發(fā)揮更突出的作用,以識別和解決系統運行的問題,。在這些頻率內,,最重要的是創(chuàng)建和控制時序空余,留下最小的空余,,以確保數據采集和演示窗口的準確,。更快的邊緣速率同時也放大物理設計的影響,造成信號完整性問題,,對此則需要更多的沉降時間及縮小時序空余,。

FPGA器件現在還包括某些先進的功能,如支持帶有I/O單元接口的雙通道數據(DDR)和板上鎖相環(huán)(PLL)網絡進行精確時鐘控制等等,。這些在FPGA技術中的高級功能均提供先進的接口模塊,,從而有助于減少界面設計,再加上TimingDesigner軟件的獨特能力,,在最短的時序中提供最準確,、有力的解決方案。本文主要探討了DDR型存儲器接口設計中必要的時鐘偏移及數據采集的時序空余,。

DDR/QDR存儲器接口的設計問題

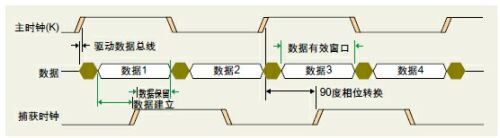

DDR或四倍數據速率(QDR)存儲設備可以提供和接受兩倍于器件時鐘頻率的源同步數據,,這意味著數據在時鐘的上升緣和下降緣傳輸。此外,,需要捕捉時鐘偏移和進行適當地調整,,以確保適當的時鐘與數據關系。

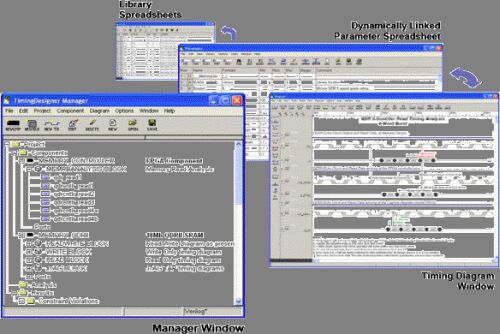

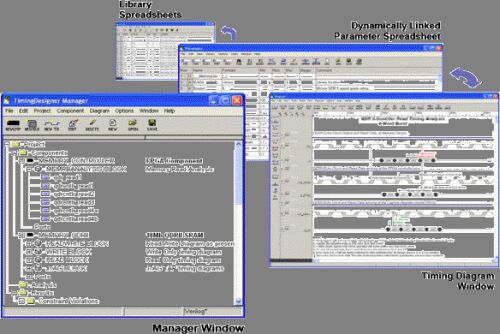

圖1:TimingDesigner軟件便于捕獲設計特點的圖形界面窗口,。

如前所述,,現在一些FPGA裝置包括DDR接口的I/O單元和板上的PLL網絡。這意味著,,你必須有一個方式來控制模塊的準確和可靠,。為了說明這一點,讓我們來讀取QDR II SRAM源同步接口的設計要求看看實例,。

FPGA的設計與高速接口技術可以幫助你滿足今天的市場要求,,但也提出了一些有趣的設計挑戰(zhàn)。為了確保存儲器接口的數據傳輸準確,,在超過200兆赫茲以上,,進行時序分析將發(fā)揮更突出的作用,以識別和解決系統運行的問題,。在這些頻率內,,最重要的是創(chuàng)建和控制時序空余,留下最小的空余,,以確保數據采集和演示窗口的準確,。更快的邊緣速率同時也放大物理設計的影響,造成信號完整性問題,對此則需要更多的沉降時間及縮小時序空余,。

FPGA器件現在還包括某些先進的功能,,如支持帶有I/O單元接口的雙通道數據(DDR)和板上鎖相環(huán)(PLL)網絡進行精確時鐘控制等等。這些在FPGA技術中的高級功能均提供先進的接口模塊,,從而有助于減少界面設計,,再加上TimingDesigner軟件的獨特能力,在最短的時序中提供最準確,、有力的解決方案,。本文主要探討了DDR型存儲器接口設計中必要的時鐘偏移及數據采集的時序空余。

DDR/QDR存儲器接口的設計問題

DDR或四倍數據速率(QDR)存儲設備可以提供和接受兩倍于器件時鐘頻率的源同步數據,,這意味著數據在時鐘的上升緣和下降緣傳輸,。此外,需要捕捉時鐘偏移和進行適當地調整,,以確保適當的時鐘與數據關系,。

圖1:TimingDesigner軟件便于捕獲設計特點的圖形界面窗口。

如前所述,,現在一些FPGA裝置包括DDR接口的I/O單元和板上的PLL網絡,。這意味著,你必須有一個方式來控制模塊的準確和可靠,。為了說明這一點,,讓我們來讀取QDR II SRAM源同步接口的設計要求看看實例。

在同步存儲器系統例如QDR SRAM中,,數據是與時鐘同步的,,所以存儲器數據的相位必須旋轉90度。這種相位旋轉通常在有效數據窗口中進行時鐘中心調整,,這是QDR實現準確數據采集的一個重要設計特點(見圖2),。如果要改變時鐘中心,我們可以通過對板上FPGA的PLL網絡進行簡單的延時時鐘信號來達到,。

圖2:中心對齊的時鐘/數據關系,。

獲取數據

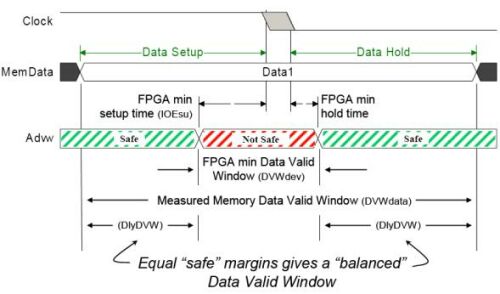

延遲時鐘信號可以實現中心對齊以避免各種溫度變化和其他類似的設計影響,可能會對時鐘或數據方面帶來一些影響,,但不會很大,,但違背了接收存儲器的建立或保持時序的要求。在理論上,,對于大部分器件,,中心對齊的時鐘邊緣將最大限度地建立和保持時序,留出足夠的安全空余,。然而,,除非建立的需求合適于保持的需求,,時鐘信號的中心對齊將提供更多的時序空余。

理想的解決辦法是為器件的建立和保持提供一個最大的安全空余,,可以通過轉化平衡空余,,為二者都提供相同的安全空余。為了平衡空余,,我們?yōu)榻邮掌骷_定最低的有效數據窗口,在實際有效數據窗口的中心窗內可以給我們的存儲器提供設計參數,。

利用接收器件最小的建立和保持時間,,我們可以利用下面的公式確定最小的“安全”的有效數據窗口:

最小創(chuàng)建時間+最低保持時間=最低有效數據窗口

如圖3所示,在存儲器器件中可以看出,,實際結果是在有效數據窗口中間,。為了確保獲取數據,總線必須在接收器最小的有效數據窗口外的“安全”區(qū)域內進行轉換,。根據時鐘與數據的關系,,信號設計在任一區(qū)域內,在獲取數據時,,我們確保盡可能多的安全空余,。

圖3:平衡實際有效數據窗口中的最小有效數據窗口。

實現適當的時鐘偏移

源同步時鐘的相位偏移將有效地改變存儲控制器接收寄存器的最小有效數據窗口,,因此將形成平衡有效數據窗口,。時鐘偏移調整是FPGA裝置中PLL器件的一個組成部分。要確定偏移的值,,我們必須考慮到影響信號的布線延遲和任何外部延遲,。

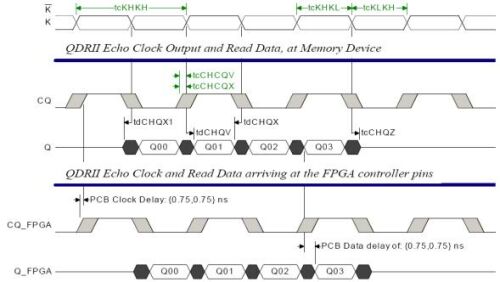

首先,我們使用TimingDesigner軟件通過存儲器數據表為QDR SRAM創(chuàng)造一個圖表(圖4),。我們利用此圖確定存儲器與有效數據窗口中的時鐘和數據信號時序的關系,。目的是精確定義存儲器的信號關系,并在PCB到FPGA的設計中傳遞這種關系,。

圖4:QDR存儲器讀取時序圖MT54W1MH18J,。

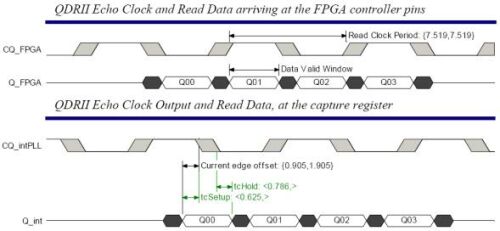

從圖4可以看出在FPGA的管腳上,PCB傳播延遲與時鐘(CQ_FPGA)和數據(Q_FPGA)信號間的關系,。在TimingDesigner軟件的動態(tài)鏈接參數表中使用單獨的變量可以輕松地獲得PCB板的延時及延遲值對相關的信號的影響?,F在,我們可以在適當的FPGA裝置中,,為獲取時鐘而得到內部布線延遲和確定正確的相位偏移,。

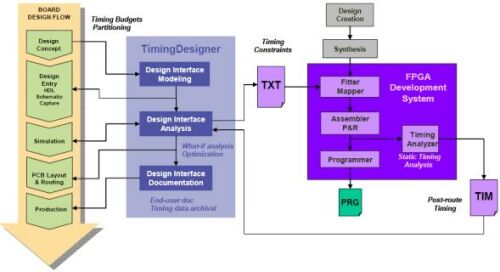

FPGA設計要素

大多數的FPGA利用約束驅動進行布局和布線。時序約束為關鍵信號提供時序信息,。TimingDesigner軟件提供獨特的時序參考圖如測量和計算變量結果,,從行內文字到文件都支持廠商特定的約束語法,。例如,在一個FPGA約束布線中,,對符合其動態(tài)文字窗口的語法要求中,,可以通過時序圖中為特定信號計算延遲誤差。然后,,我們可以將這些語法通過一個文本文件導入到FPGA的開發(fā)系統中,,或者我們可以直接將數值復制到FPGA的約束編輯器中。

對于高速存儲器接口設計,,數據存儲器被放置在FPGA裝置I/O單元的附近,,以盡量減少布線延時的影響。該I/O單元只有一個布線路徑為輸入數據信號,,因此在數據總線的每一部分都存在數據路徑延遲,。FPGA的PLL也被用來進行適當的時鐘控制,并通常有幾種可能的從輸入焊盤到捕捉寄存器的路徑,。制造商通過控制特定的屬性,,使PLL的特點包括相位偏移,相乘,,或相除等因素,,無論是原始示例的設計代碼或約束都可以帶入模塊。因此,,時鐘和數據路徑的布線和延誤必須確定,,以實現適當的時鐘相位偏移。

圖5:TimingDesigner軟件為FPGA設計流程提供直觀的界面,。

在FPGA的最初布局和布線完成后,,時序報告提供數據總線中每個時序的詳細延時信息。如果有必要,,可為FPGA開發(fā)系統的關鍵信號設定延時路徑,,TimingDesigner軟件可以提取相關信息和利用圖表更新。在這個設計實例中,,我們需要輸入數據總線和相關時鐘信號的時序報告,。

1.導入布線后的時序到TimingDesigner軟件中

導入FPGA的時序報告信息,我們需要規(guī)劃最壞的情況從而確定在圖表(Q_FPGA)中相關的波形圖,。信號設計規(guī)范定義在同一個時序圖表中不能帶有同名的波形圖,。通過規(guī)劃端口, TimingDesigner軟件可以過濾時序報告并提取有用的信息,。這些規(guī)劃被存儲在圖表文件內并可預先解決的布局和布線問題,。

2.提供可視化的捕捉寄存器

從導入時序報告文件開始, TimingDesigner軟件為關鍵信號延時創(chuàng)建變量,,并在電子數據表中規(guī)劃和分配這些信號端口,。變量過去是用來在時序圖中更新時鐘與數據關系?,F在,可確定在FPGA器件內捕捉寄存器中的邊緣關系,。

內部寄存器建立和保持是從時序報告和相關的約束中提取所需的時序,。下一步,在時序圖表中添加另外兩個信號和偏移時序報告中的布線延時,;在捕捉寄存器中添加數據和時鐘,,然后建立和保持FPGA器件適用的約束。用時鐘邊緣和有效數據窗口邊緣的補償確定必要的相位偏移,,來平衡設計中有效的數據窗口,。

3.平衡有效數據窗口

我們可以使用下列公式來確定PLL時鐘信號產生的相位偏移:

1、從設計的實際有效數據窗口減少FPGA裝置I/O部分的最小有效數據窗口,,然后結果除于2,實際結果為這2個有效數據窗口的差額(DlyDVW),。(參考圖3)

DlyDVW = (DVWdata - DVWdev) / 2

2,、I/O寄存器數據建立時間加上DlyDVW值,就確定了相對時鐘邊緣的有效數據窗口(DlyRelSU),。

DlyRelSU = DlyDVW + IOEsu

3,、最后,從相對建立時間(上面第2步得到的數值),,減去時鐘信號與捕捉寄存器的有效數據窗口(從時序圖測量)之間的補償,。

Clk_offset = DlyRelSU - EdgeOffset

利用上述公式,我們可以確定FPGA開發(fā)系統中PLL的相位偏移量,,并執(zhí)行到下一步的布局和布線,。

4.驗證結果

再次導入做過以上修改的布線后時序文件,TimingDesigner軟件會自動更新需要的數值,,并更正及重新定位I/O單元的時鐘信號CQ_intPLL,。如圖6所示。依靠改變PLL,,確切的平衡建立和保持空余將是不可能的,。對于這些情況下,應該在FPGA裝置的PLL中獲取平衡增量以解決這個問題,。

圖6:在改變時鐘和平衡建立及保持空余后,,獲取數據分析的時序圖表。

本文小結

高速設計往往有嚴格的規(guī)范和嚴謹的發(fā)布時間表,,所以需要一個交互式的時序規(guī)劃和分析工具,,來獲得快速和完整的時序空余,以分析并解決可能影響到最終設計成功的因素,。本文說明了如何利用TimingDesigner軟件對FPGA設計流程進行準確地捕捉和交換時序信息,,以幫助在整個設計過程中管理時序空余,,并提供可視化的界面驗證設計,并預測設計性能,。今天的FPGA器件產品都帶有多功能的時鐘配置和豐富的I/O資源,,并且?guī)в懈邤祿鬏斈芰Γ琓imingDesigner軟件為高速存儲器如DDR & QDR SRAM提供精確的關鍵路徑時序分析功能,。