0 引言

VHDL超高速集成電路硬件描述語(yǔ)言是隨著集成電路系統(tǒng)化和高度集成化逐步發(fā)展起來(lái)的,是一種用于數(shù)字系統(tǒng)設(shè)計(jì)、測(cè)試,面向多領(lǐng)域、多層次的IEEE標(biāo)準(zhǔn)硬件描述語(yǔ)言。它從20世紀(jì)70年代作為電路設(shè)計(jì)工具誕生于美國(guó)國(guó)防部至今,已經(jīng)成為十分流行的硬件描述工具,并且為大多數(shù)EDA工具所支持。隨著電子技術(shù)的不斷進(jìn)步,數(shù)字系統(tǒng)的設(shè)計(jì)正朝著高速度、大容量、小體積的方向發(fā)展。傳統(tǒng)的自底而上的模式已不能滿(mǎn)足芯片和系統(tǒng)的設(shè)計(jì)要求。為了提高設(shè)計(jì)效率,能夠簡(jiǎn)化設(shè)計(jì)流程,大幅降低設(shè)計(jì)難度的VHDL設(shè)計(jì)方法受到廣泛關(guān)注。VHDL與其他傳統(tǒng)集成電路描述語(yǔ)言相比,具有明顯優(yōu)勢(shì):

(1)功能強(qiáng)大,描述力強(qiáng)。可用于門(mén)級(jí)、電路級(jí)甚至系統(tǒng)級(jí)的描述、仿真和設(shè)計(jì)。

(2)可移植性好。對(duì)于設(shè)計(jì)和仿真工具及不同的平臺(tái)均可采用相同的描述。

(3)研制周期短,成本低。

(4)可以延長(zhǎng)設(shè)計(jì)的生命周期。

(5)具有電路仿真與驗(yàn)證功能,用戶(hù)甚至不必編寫(xiě)相量測(cè)試即可進(jìn)行源代碼級(jí)調(diào)試。設(shè)計(jì)者能夠跳過(guò)電路實(shí)驗(yàn),直接對(duì)各種方案進(jìn)行比較和選擇,使設(shè)計(jì)效率得以提高。

(6)對(duì)設(shè)計(jì)的描述具有相對(duì)獨(dú)立性。

(7)語(yǔ)言標(biāo)準(zhǔn)、規(guī)范,易于共享和復(fù)用。

目前,VHDL滲透了電子技術(shù)及其相關(guān)的各個(gè)工業(yè)領(lǐng)域,在工業(yè)設(shè)計(jì)中發(fā)揮著日益重要的作用。在世界范圍內(nèi),關(guān)于VHDL在多個(gè)領(lǐng)域尤其在芯片,系統(tǒng)設(shè)計(jì)方面的應(yīng)用研究已經(jīng)取得眾多矚目成果。

而將VHDL與醫(yī)學(xué)相結(jié)合,勢(shì)必成為電子自動(dòng)化設(shè)計(jì)(EDA)一個(gè)全新的研究方向,本文主要研究將EDA通過(guò)VHDL應(yīng)用于醫(yī)學(xué),以對(duì)脈搏的測(cè)量為例,以實(shí)現(xiàn)數(shù)字系統(tǒng)對(duì)人體多種生理活動(dòng)及生理反應(yīng)的直觀精確測(cè)量。

1 實(shí)驗(yàn)設(shè)計(jì)

1.1 EDA技術(shù)在醫(yī)學(xué)教學(xué)中脈搏測(cè)量中的應(yīng)用探討

在臨床診斷,護(hù)理學(xué)等中介紹脈搏的測(cè)量時(shí)認(rèn)為脈搏很容易在手腕掌面外側(cè)跳動(dòng)的橈動(dòng)脈上摸到,也可測(cè)量頸部的頸動(dòng)脈或腹股溝的股動(dòng)脈。其測(cè)量方法是病員手臂放于舒適位置,用食指,中指,無(wú)名指的指腹端按壓在橈動(dòng)脈表面,一般病員默數(shù)半分鐘。將所測(cè)的脈率乘以2便是一分鐘的脈數(shù),異常病人測(cè)一分鐘。成年人的脈搏在安靜狀態(tài)下每分鐘是60~80次。如少于60次是心動(dòng)過(guò)緩。但訓(xùn)練有素的運(yùn)動(dòng)員,脈搏有時(shí)也在60次以下,這正是心臟健康有力的表現(xiàn)。如超過(guò)100次是心動(dòng)過(guò)速。體力活動(dòng)或情緒激動(dòng)時(shí),脈搏可暫時(shí)增快,發(fā)燒時(shí)脈搏也增快。一般是體溫每升高1℃,脈搏就增加10~20次。此法只能粗略計(jì)算脈搏跳動(dòng)。如將VHDL語(yǔ)言應(yīng)用其中,便可以通過(guò)EDA實(shí)驗(yàn)箱中的七段數(shù)碼管直觀準(zhǔn)確地看到一分鐘的計(jì)數(shù)結(jié)果,并與之前通過(guò)醫(yī)學(xué)教材講授方法測(cè)出結(jié)果相比對(duì),從而判定測(cè)量的正確與否。

1.2 設(shè)計(jì)思路

將脈搏信號(hào)通過(guò)脈搏傳感器采集進(jìn)入計(jì)算機(jī),而后作為輸入信號(hào),而此信號(hào)作為脈沖信號(hào),即如時(shí)鐘信號(hào)一般,當(dāng)輸入時(shí)計(jì)數(shù)器開(kāi)始計(jì)數(shù),如下面設(shè)計(jì)一個(gè)十進(jìn)制計(jì)數(shù)器的VHDL描述便可用來(lái)對(duì)所采集的脈搏信號(hào)計(jì)數(shù)。

1.3 VHDL設(shè)計(jì)流程

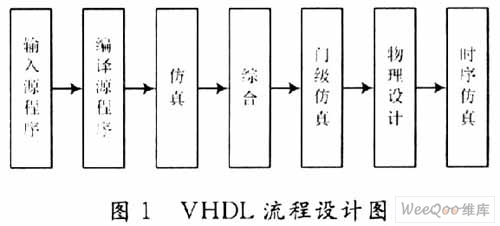

VHDL流程設(shè)計(jì)如圖1所示。

0 引言

VHDL超高速集成電路硬件描述語(yǔ)言是隨著集成電路系統(tǒng)化和高度集成化逐步發(fā)展起來(lái)的,是一種用于數(shù)字系統(tǒng)設(shè)計(jì)、測(cè)試,面向多領(lǐng)域、多層次的IEEE標(biāo)準(zhǔn)硬件描述語(yǔ)言。它從20世紀(jì)70年代作為電路設(shè)計(jì)工具誕生于美國(guó)國(guó)防部至今,已經(jīng)成為十分流行的硬件描述工具,并且為大多數(shù)EDA工具所支持。隨著電子技術(shù)的不斷進(jìn)步,數(shù)字系統(tǒng)的設(shè)計(jì)正朝著高速度、大容量、小體積的方向發(fā)展。傳統(tǒng)的自底而上的模式已不能滿(mǎn)足芯片和系統(tǒng)的設(shè)計(jì)要求。為了提高設(shè)計(jì)效率,能夠簡(jiǎn)化設(shè)計(jì)流程,大幅降低設(shè)計(jì)難度的VHDL設(shè)計(jì)方法受到廣泛關(guān)注。VHDL與其他傳統(tǒng)集成電路描述語(yǔ)言相比,具有明顯優(yōu)勢(shì):

(1)功能強(qiáng)大,描述力強(qiáng)。可用于門(mén)級(jí)、電路級(jí)甚至系統(tǒng)級(jí)的描述、仿真和設(shè)計(jì)。

(2)可移植性好。對(duì)于設(shè)計(jì)和仿真工具及不同的平臺(tái)均可采用相同的描述。

(3)研制周期短,成本低。

(4)可以延長(zhǎng)設(shè)計(jì)的生命周期。

(5)具有電路仿真與驗(yàn)證功能,用戶(hù)甚至不必編寫(xiě)相量測(cè)試即可進(jìn)行源代碼級(jí)調(diào)試。設(shè)計(jì)者能夠跳過(guò)電路實(shí)驗(yàn),直接對(duì)各種方案進(jìn)行比較和選擇,使設(shè)計(jì)效率得以提高。

(6)對(duì)設(shè)計(jì)的描述具有相對(duì)獨(dú)立性。

(7)語(yǔ)言標(biāo)準(zhǔn)、規(guī)范,易于共享和復(fù)用。

目前,VHDL滲透了電子技術(shù)及其相關(guān)的各個(gè)工業(yè)領(lǐng)域,在工業(yè)設(shè)計(jì)中發(fā)揮著日益重要的作用。在世界范圍內(nèi),關(guān)于VHDL在多個(gè)領(lǐng)域尤其在芯片,系統(tǒng)設(shè)計(jì)方面的應(yīng)用研究已經(jīng)取得眾多矚目成果。

而將VHDL與醫(yī)學(xué)相結(jié)合,勢(shì)必成為電子自動(dòng)化設(shè)計(jì)(EDA)一個(gè)全新的研究方向,本文主要研究將EDA通過(guò)VHDL應(yīng)用于醫(yī)學(xué),以對(duì)脈搏的測(cè)量為例,以實(shí)現(xiàn)數(shù)字系統(tǒng)對(duì)人體多種生理活動(dòng)及生理反應(yīng)的直觀精確測(cè)量。

1 實(shí)驗(yàn)設(shè)計(jì)

1.1 EDA技術(shù)在醫(yī)學(xué)教學(xué)中脈搏測(cè)量中的應(yīng)用探討

在臨床診斷,護(hù)理學(xué)等中介紹脈搏的測(cè)量時(shí)認(rèn)為脈搏很容易在手腕掌面外側(cè)跳動(dòng)的橈動(dòng)脈上摸到,也可測(cè)量頸部的頸動(dòng)脈或腹股溝的股動(dòng)脈。其測(cè)量方法是病員手臂放于舒適位置,用食指,中指,無(wú)名指的指腹端按壓在橈動(dòng)脈表面,一般病員默數(shù)半分鐘。將所測(cè)的脈率乘以2便是一分鐘的脈數(shù),異常病人測(cè)一分鐘。成年人的脈搏在安靜狀態(tài)下每分鐘是60~80次。如少于60次是心動(dòng)過(guò)緩。但訓(xùn)練有素的運(yùn)動(dòng)員,脈搏有時(shí)也在60次以下,這正是心臟健康有力的表現(xiàn)。如超過(guò)100次是心動(dòng)過(guò)速。體力活動(dòng)或情緒激動(dòng)時(shí),脈搏可暫時(shí)增快,發(fā)燒時(shí)脈搏也增快。一般是體溫每升高1℃,脈搏就增加10~20次。此法只能粗略計(jì)算脈搏跳動(dòng)。如將VHDL語(yǔ)言應(yīng)用其中,便可以通過(guò)EDA實(shí)驗(yàn)箱中的七段數(shù)碼管直觀準(zhǔn)確地看到一分鐘的計(jì)數(shù)結(jié)果,并與之前通過(guò)醫(yī)學(xué)教材講授方法測(cè)出結(jié)果相比對(duì),從而判定測(cè)量的正確與否。

1.2 設(shè)計(jì)思路

將脈搏信號(hào)通過(guò)脈搏傳感器采集進(jìn)入計(jì)算機(jī),而后作為輸入信號(hào),而此信號(hào)作為脈沖信號(hào),即如時(shí)鐘信號(hào)一般,當(dāng)輸入時(shí)計(jì)數(shù)器開(kāi)始計(jì)數(shù),如下面設(shè)計(jì)一個(gè)十進(jìn)制計(jì)數(shù)器的VHDL描述便可用來(lái)對(duì)所采集的脈搏信號(hào)計(jì)數(shù)。

1.3 VHDL設(shè)計(jì)流程

VHDL流程設(shè)計(jì)如圖1所示。

現(xiàn)在,計(jì)算機(jī)輔助工程軟件的供應(yīng)商已把日益通用的硬件描述語(yǔ)言VHDL作為其CAD或EDA軟件輸入與輸出的標(biāo)準(zhǔn),其中ALTEKA公司提供的綜合工具M(jìn)ax+PlusⅡ,具有全面的邏輯設(shè)計(jì)能力,從編輯、綜合、布線到仿真、下載都十分方便。

2 設(shè)計(jì)方案與結(jié)果分析

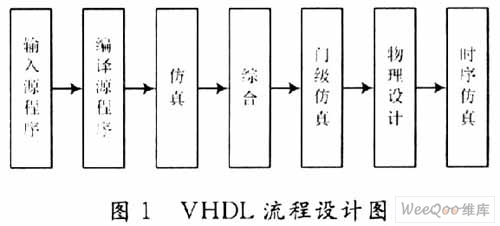

VHDL語(yǔ)言設(shè)計(jì)十進(jìn)制計(jì)數(shù)器的源程序:

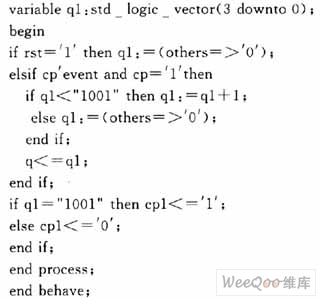

在程序輸入完成后,經(jīng)Max+PlusⅡ中的Compiler編譯通過(guò)后,可用Stimulator進(jìn)行仿真,查看仿真結(jié)果,如圖2所示。

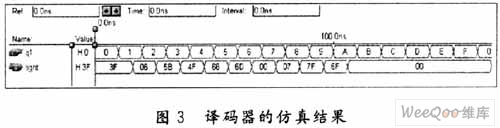

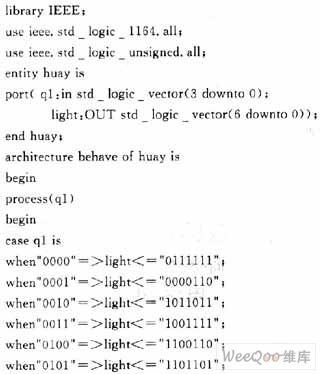

也可以加入七段顯示譯碼器的VHDL設(shè)計(jì)來(lái)通過(guò)實(shí)驗(yàn)箱的七段數(shù)碼管掃描顯示計(jì)數(shù)結(jié)果仿真結(jié)果如圖3所示。

代碼如下:

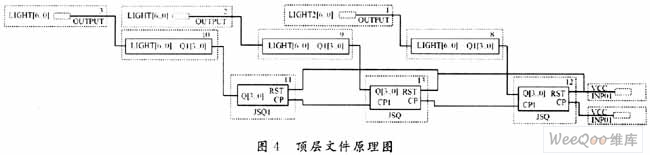

最終實(shí)現(xiàn)的頂層文件原理圖如圖4所示。

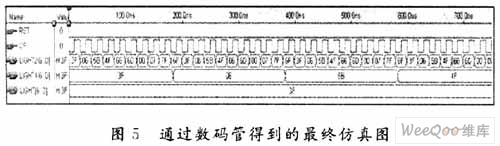

頂層文件設(shè)計(jì)如圖4所示,通過(guò)該文件可以實(shí)現(xiàn)譯碼,下載到EDA實(shí)驗(yàn)箱時(shí),便可于實(shí)驗(yàn)箱的數(shù)碼管上讀出相應(yīng)的脈搏數(shù),如圖5所示。

VHDL語(yǔ)言與醫(yī)學(xué)內(nèi)容的結(jié)合,除了應(yīng)用于脈搏的測(cè)量,還可應(yīng)用于心跳及呼吸等的測(cè)量,以及受人體對(duì)聲、光刺激后的生理反應(yīng)時(shí)間的測(cè)定等。電子自動(dòng)化設(shè)計(jì)(EDA)及其相關(guān)技術(shù),在醫(yī)學(xué)領(lǐng)域具有巨大的應(yīng)用前景,有待進(jìn)一步的研究和發(fā)掘。

3 結(jié)語(yǔ)

VHDL是一種隨著電子技術(shù)的不斷發(fā)展,為滿(mǎn)足電路系統(tǒng)化和高度集成化要求而發(fā)展起來(lái)的一種新型硬件描述語(yǔ)言。VHDL具有廣泛的應(yīng)用范圍,在芯片及電路系統(tǒng)設(shè)計(jì)等方面發(fā)揮著日益重要的作用。以VHDL為核心的EDA技術(shù)應(yīng)用于醫(yī)學(xué),能直觀準(zhǔn)確的測(cè)量人體的脈搏心跳,呼吸等生理活動(dòng),以及受到外界刺激的生理反應(yīng)等,在醫(yī)學(xué)領(lǐng)域存在廣闊的發(fā)展空間,隨著進(jìn)一步的探索和實(shí)踐,必將對(duì)醫(yī)學(xué)的發(fā)展起到極大的推動(dòng)作用。