摘要:在某虛擬仿真實驗平臺系統(tǒng)中,需要收發(fā)批量GJB289A總線數(shù)據(jù),并且按不同算法對數(shù)據(jù)進(jìn)行實時處理。為此,設(shè)計了PCI總線智能 GJB289A仿真卡。采用FPGA實現(xiàn)GJB289A接口邏輯,設(shè)計了GJB289A總線模擬收發(fā)器,替換了國外芯片,降低了系統(tǒng)成本。采用DSP的 PCI接口在線加栽程序的方式,在線更新數(shù)據(jù)處理算法,并按照相應(yīng)算法對GJB289A總線數(shù)據(jù)進(jìn)行快速處理,提高了仿真系統(tǒng)的靈活性和實時性。目前,該仿真卡在虛擬仿真實驗平臺系統(tǒng)中成功使用,工作穩(wěn)定。

關(guān)鍵詞:DSP;PCI;GJB289A;在線加載

虛擬仿真系統(tǒng)模擬GJB289A總線設(shè)備,需要收發(fā)大量的GJB289A總線數(shù)據(jù)。傳統(tǒng)的處理方式是通過GJB289A總線PCI通訊卡將接收到的數(shù)據(jù)傳輸?shù)缴衔粰C(jī),由上位機(jī)程序?qū)?shù)據(jù)進(jìn)行處理,然后上位機(jī)再將處理結(jié)果通過PCI卡傳輸?shù)紾JB289A總線上,這種方式影響虛擬仿真系統(tǒng)仿真效率,系統(tǒng)實時性不好。此外,傳統(tǒng)的GJB289A總線仿真卡處理器程序固定,不能滿足不同處理算法的需要。PCI總線智能GJB289A仿真卡實時處理GJB289A 總線數(shù)據(jù),無需將數(shù)據(jù)轉(zhuǎn)移到上位機(jī),提高數(shù)據(jù)處理速度,增強(qiáng)了系統(tǒng)實時性。用戶能夠根據(jù)需要,在線加載DSP程序,更新數(shù)據(jù)處理算法,以適應(yīng)不同處理算法的需要。增強(qiáng)了仿真卡的靈活性。

1 主要功能及指標(biāo)

PCI總線智能GJB289A仿真卡主要具備以下功能及指標(biāo):

CPU主頻:600 MHz,處理速度為9 600 MIPS;

緩存空間:SDRAM空間為16 MB;

PCI接口:總線寬度32 b、速率33 MHz;

GJB289A接口:雙冗余模擬收發(fā),具備RT/BC/MT,傳輸速率為1 Mb/s;

在線加載DSP程序。

2 硬件設(shè)計

由分析設(shè)計要求,在此提出基于TMS320DM642為核心的硬件結(jié)構(gòu)設(shè)計:包括DSP及外圍電路設(shè)計、GJB289A接口邏輯設(shè)計、GJB289A總線模擬收發(fā)器設(shè)計。

2.1 DSP及外圍電路設(shè)計

TI公司的TMS320DM642是一款主頻為600 MHz,32位定點的高性能DSP,片內(nèi)集成PCI2.2協(xié)議模塊,支持主/從模式的DMA數(shù)據(jù)傳輸。相較于采用專用PCI接口芯片或者FPGA等方式實現(xiàn),開發(fā)方式簡單,成本低。

DM642通過EMIFA與SDRAM和FLASH芯片相連,其中2片64 Mb的SDRAM,作為仿真卡的數(shù)據(jù)緩存空間,F(xiàn)LASH作為程序空間。通過設(shè)置Boot模

式選擇程序從PCI接口還是EMIFA接口加載。當(dāng)從PCI接口加載時,用戶可以動態(tài)加載DSP程序,當(dāng)從EMIFA接口加載時,用戶可以將固化好的程序?qū)懭隖LASH中,由Bootloader引導(dǎo)程序的自啟動。

2.2 GJB289A接口設(shè)計

GJB289A-97總線是國內(nèi)在研究為人熟知的MILSTD-1553B總線的基礎(chǔ)上制定出來的國家軍用標(biāo)準(zhǔn),全稱“數(shù)字式時分制指令/響應(yīng)型多路傳輸數(shù)據(jù)總線”,由于其具有極高的可靠性,因而在航空、航天、軍事等領(lǐng)域的電子聯(lián)網(wǎng)系統(tǒng)中得到廣泛應(yīng)用。目前GJB289A協(xié)議模塊較多由國外的高級 1553B協(xié)議處理芯片BU61580實現(xiàn)。在此GJB289A接口協(xié)議模塊由FPGA邏輯實現(xiàn),代替原有的協(xié)議芯片,節(jié)約了系統(tǒng)成本,增加了設(shè)計的靈活性。

FPGA邏輯包括曼徹斯特編解碼單元、協(xié)議處理模塊、數(shù)據(jù)緩沖FIFO、寄存器控制等。邏輯框圖如圖1所示。發(fā)送數(shù)據(jù)時將已有的并行數(shù)據(jù)在系統(tǒng)的控制下,經(jīng)過并/串轉(zhuǎn)換,轉(zhuǎn)換為并行的曼徹斯特編碼,依次以符合1553B協(xié)議的消息的方式發(fā)出。在BC或者RT模式下接收數(shù)據(jù)時,模擬收發(fā)器接收曼徹斯特Ⅱ編碼的串行數(shù)據(jù),通過曼徹斯特解碼器實現(xiàn)同步時鐘的提取,同步頭檢出,數(shù)據(jù)檢出,曼徹斯特Ⅱ碼錯誤檢出,奇偶校驗,位/字計數(shù)以及數(shù)據(jù)的串/并轉(zhuǎn)換功能。

2.3 模擬收發(fā)器設(shè)計

模擬發(fā)送器是將FPGA輸出的TTL電平信號轉(zhuǎn)換為滿足協(xié)議要求電氣特性的信號傳輸?shù)诫娎|上,并提供一定的功率使發(fā)送信號順利被接受方正確接收。模擬接收器是將在總線電纜上雙極性電平的信號轉(zhuǎn)換為可以直接接入FPGA的TTL電平信號,且信號的失真應(yīng)控制在一定的范圍之內(nèi)以使得通信過程正確。目前GJB289A總線模擬收發(fā)器較多由國外的HI-1573總線驅(qū)動芯片實現(xiàn),在此設(shè)計了模擬收發(fā)器電路,可以代替1573芯片。模擬發(fā)送部分電路如圖2所示,由FPGA直接生成的TTL電平信號從電路的左端輸入,輸入的信號為單極性的曼徹斯特Ⅱ型編碼,信號差分輸出。圖中的兩個PNP型三極管工作在開關(guān)狀態(tài),R1為基極偏置電阻,R2為集電極負(fù)載,二極管起保護(hù)作用。右端的隔離變壓器將信號放大輸入到總線電纜。總線驅(qū)動器的接收部分電路如圖3所示,總線電纜上的信號從右端的隔離變壓器輸入,通過隔離變壓器電平轉(zhuǎn)換后到達(dá)高速比較器,信號高于門檻電壓時比較器輸出高電平;信號低于門檻電壓時比較器輸出低電平。最終變?yōu)閮陕稵TL電平的差分信號輸入FPGA中做進(jìn)一步處理。

TI公司TMS320C6000系列DSP程序主要的加載方式:一種是由EMIF接口引導(dǎo)程序加載,程序代碼、數(shù)據(jù)存放在外擴(kuò)的FLASH中,這種方式加載的DSP程序是固定的,不能支持在線更新;另一種是由PCI接口引導(dǎo),主機(jī)通過PCI接口可以訪問DSP片內(nèi)片外存儲單元,將程序代碼寫入DSP片內(nèi) RAM區(qū),復(fù)位DSP時,程序即開始從地址O執(zhí)行。這種方式可以在線加載DSP程序,更新處理算法,滿足系統(tǒng)設(shè)計要求,所以本系統(tǒng)采用PCI接口加載方式。

3 DSP程序在線加載方法

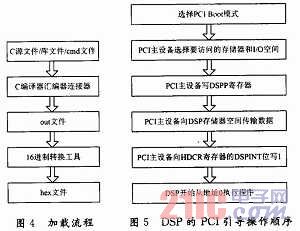

用戶在主程序框架內(nèi)添加算法函數(shù),再通過上位機(jī)軟件,自動調(diào)用TI公司C編譯器c16x.exe、匯編器asm6x.exe和連接器link6x.exe 殼程序,將C代碼編譯連接生成可執(zhí)行的out文件。主機(jī)PCI接口的加載方式,需要將可執(zhí)行的目標(biāo)代碼.out文件轉(zhuǎn)換為十六進(jìn)制.hex文件,再寫入到 DSP的內(nèi)部RAM空間。具體加載流程如圖4所示。

在調(diào)用16進(jìn)制轉(zhuǎn)換工具時,需要指定調(diào)用16進(jìn)制轉(zhuǎn)換工具的命令行選項和文件名,為此創(chuàng)建一個批處理文件,內(nèi)容如下:

通過上述方法將out文件轉(zhuǎn)換成hex文件,上位機(jī)程序讀取hex文件內(nèi)容為文本形式的ASCII,每8個字符為一組存入數(shù)組中。TIC6000系列DSP的PCI加載引導(dǎo)操作順序:首先通過地址總線的A21、A22引腳配置選擇PCI Boot模式。上位機(jī)通過驅(qū)動程序設(shè)置要訪問的存儲器、I/O空間和DSPP寄存器。將存有hex內(nèi)容的數(shù)組寫入到DSP的內(nèi)部RAM區(qū)。然后向HDCR寄存器的DSPINT位寫1,DSP開始從地址O開始。如圖5所示。

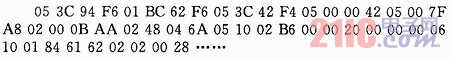

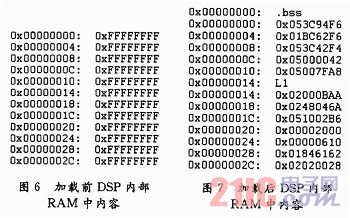

下面為演示實例,運(yùn)行上位機(jī)軟件,調(diào)用驅(qū)動程序函數(shù)庫,對PCI仿真卡進(jìn)行初始化設(shè)置,初始化完成后將hex內(nèi)容寫入DSP存儲空間,加載前,DSP內(nèi)部RAM內(nèi)容,通過調(diào)用16進(jìn)制轉(zhuǎn)換工具,將DSP程序可執(zhí)行目標(biāo)文件out轉(zhuǎn)換為hex文件,其內(nèi)容為:

加載前后DSP內(nèi)部RAM內(nèi)容如圖6、圖7所示。

從實例可以看出,經(jīng)過上述加載方式,完成了DSP程序的在線加載,更新了DSP程序,滿足了不同數(shù)據(jù)處理算法的需要。

4 結(jié)語

介紹了一種基于DM642的PCI總線GJB289A智能仿真卡的設(shè)計方法,采用高速DSP DM642作為主控制器,實現(xiàn)了對GJB289A總線數(shù)據(jù)的快速處理;在FPGA中實現(xiàn)GIB289A總線協(xié)議,設(shè)計了模擬收發(fā)器電路,替換國外芯片,減少了對國外芯片的依賴性,并節(jié)約了成本。在軟件方面,采用PCI總線在線加載技術(shù),實時更新DSP數(shù)據(jù)處理算法,能夠適應(yīng)不同處理算法的需要。目前在虛擬仿真實驗平臺系統(tǒng)的應(yīng)用,表明該仿真卡設(shè)計正確,工作穩(wěn)定可靠。