引言

新型恩智浦ARM Cortex-M3微控制器首次采用的SPI閃存接口技術(shù)(SPIFI),它可以幫助設(shè)計(jì)人員以小尺寸、低成本的串行閃存替代大尺寸、高成本的并行閃存。利用SPIFI (讀音與spiffy諧音,意為“出色、整潔、漂亮”等——譯注),外部串行閃存可以映射到微控制器內(nèi)存中,達(dá)到片上內(nèi)存讀取效果。新技術(shù)可以解決傳統(tǒng)嵌入式系統(tǒng)外部閃存選型難題,為設(shè)計(jì)人員在保持系統(tǒng)性能的同時(shí)縮小尺寸及降低成本提供了一條新途徑。

目前恩智浦開發(fā)出一種新型外設(shè)接口技術(shù),該技術(shù)在基于ARM Cortex-M3內(nèi)核的最新LPC1800微控制器上已得到成功應(yīng)用。嵌入式系統(tǒng)設(shè)計(jì)人員利用該技術(shù)可將串行閃存取代并行閃存,縮小封裝尺寸,降低系統(tǒng)成本。這種稱為SPI閃存接口(SPIFI)的技術(shù)目前已申請專利,通過該技術(shù)可將外部串行閃存映射到微控制器內(nèi)存,實(shí)現(xiàn)片上內(nèi)存讀取效果。SPIFI為設(shè)計(jì)人員提供了一種創(chuàng)新解決方案,在保持系統(tǒng)性能的同時(shí)達(dá)到簡化配置、縮小封裝體積、減少板載空間占用和節(jié)約系統(tǒng)成本的目的。

外部閃存的作用

采用32位微控制器(MCU)的嵌入式應(yīng)用目前越來越復(fù)雜,需要完成多媒體、照片和其他各種數(shù)據(jù)密集型內(nèi)容的管理任務(wù)。特別是人機(jī)接口系統(tǒng),用戶現(xiàn)在都希望有圖形顯示,通過窗口、圖片、動畫、聲音和其他多媒體方式實(shí)現(xiàn)人機(jī)對話。此外,隨著市場的國際化,產(chǎn)品需要滿足多國語言要求,支持各種字母和字符。所有這些都對系統(tǒng)存儲資源提出了更高要求。

大部分32位微控制器都配有片上閃存,用于支持各種數(shù)據(jù)密集型功能,但是這種內(nèi)存容量有限,通常無法滿足整體應(yīng)用要求。片上閃存通常不足1Mb,雖然能夠解決主要應(yīng)用代碼存儲,卻無法滿足其他應(yīng)用資料的保存要求,比如:查找表單、圖像、照片、聲音文件、多國語言等。為此,設(shè)計(jì)人員通常要使用外部閃存。

與片上閃存相比,外部閃存成本要低很多,而且通常都有8Mb以上的現(xiàn)貨。使用外部閃存可以增加系統(tǒng)靈活性,系統(tǒng)運(yùn)行時(shí)能夠更新升級軟件。

并行閃存與串行閃存的艱難選擇

對于外部閃存選型(串行和并行),設(shè)計(jì)人員通常要綜合*估,折衷考慮。并行閃存的速度通常比串行閃存快,但需要使用更多管腳、PCB布線和板載空間。

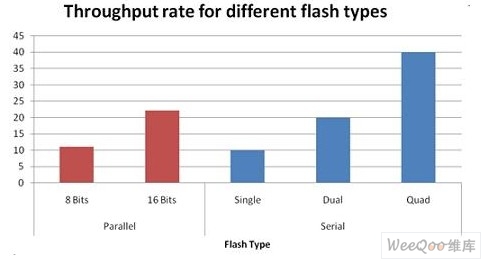

圖1給出了串行和并行閃存典型的數(shù)據(jù)傳輸速率。對于并行閃存,圖中假定無緩沖,固定存取時(shí)間為90ns。基于上述條件,16位并行閃存的最大傳輸速率22Mb/s。對于串行閃存,最大時(shí)鐘頻率80MHz的每位傳輸速率為80Mb/s,四通道串行閃存最大傳輸速率為40Mb/s。雖然該計(jì)算忽略了控制位,但四通道SPI閃存支持burST位,而SPIFI接口支持該功能,因此SPIFI接口可以達(dá)到上述傳輸速率。

圖1:串行和并行閃存的典型傳輸速率。

如圖1所示,典型的16位并行閃存每秒傳輸速率為20Mb。對于使用32位微控制器和32位外部閃存通信總線的系統(tǒng)(如恩智浦產(chǎn)品),設(shè)計(jì)人員可以選擇使用兩個(gè)16位并行閃存達(dá)到40Mb/s的傳輸速率。但是,增加速度的同時(shí)也會增加成本。這種配置使用兩個(gè)獨(dú)立的并行閃存,每個(gè)閃存有數(shù)十個(gè)封裝管腳,無論是封裝尺寸、管腳數(shù)量,還是PCB空間占用,都會遠(yuǎn)遠(yuǎn)超出設(shè)計(jì)人員的承受范圍。

串行閃存通常使用簡單的四針串行外設(shè)接口(SPI),從空間占用、功耗和成本等因素考慮是并行閃存的理想替代產(chǎn)品,但是傳輸速率非常低。通過圖1我們可以看到典型SPI閃存50MHz的傳輸速率僅為5Mb/s,而采用兩個(gè)16位并行閃存配置系統(tǒng)的傳輸速率是其8倍。另一個(gè)問題就是大多數(shù)微控制器SPI接口都與MCU外設(shè)矩陣連接,處理器訪問數(shù)據(jù)前必須先由驅(qū)動器代碼接收到內(nèi)容并保存在板載RAM中。由于每次讀取串行閃存都要通過SPI軟件層,因此速度無法提高。對于采用標(biāo)準(zhǔn)SPI接口的外部閃存應(yīng)用,速度可能無法滿足要求。

新型四通道SPI閃存采用改進(jìn)的6針SPI配置,數(shù)據(jù)傳輸速率遠(yuǎn)高于傳統(tǒng)的SPI接口。如圖1所示,四通道SPI每秒最大傳輸速率可達(dá)40Mb,與兩個(gè)16位并行閃存速度相當(dāng)。由于減少了管腳數(shù)量和封裝尺寸,與并行方案相比,四通道SPI串行閃存可有效降低成本。雖然四通道SPI閃存完全可替代嵌入式系統(tǒng)中的并行閃存,但目前32位微控制器設(shè)計(jì)并不支持四通道SPI閃存的最大傳輸速率。這主要是因?yàn)樗耐ǖ繱PI接口與傳統(tǒng)的SPI接口連接方式相同,直接連接了微控制器外設(shè)矩陣。

解決外部閃存選型難題

恩智浦新開發(fā)的SPI閃存接口(SPIFI)可以徹底解決并行/串行閃存的選型困擾。已申請專利的SPIFI外設(shè)可以將低成本SPI和新型四通道SPI閃存映像到ARM Cortex-M3內(nèi)存中。與外部并行閃存方案相比,使用SPI外部閃存的MCU性能損失非常小。由于外部SPI閃存完整的內(nèi)存空間可以映像到MCU內(nèi)存中,微控制器對外部閃存直接訪問,無需使用軟件API或庫。

例如,使用四通道SPI閃存,SPIFI外設(shè)傳輸速率可達(dá)40Mb/s。設(shè)計(jì)人員可以選擇更便宜的SPI閃存器件,在保證性能的基礎(chǔ)上縮小腳位尺寸,簡化配置。由于系統(tǒng)無需針對外部并行閃存使用龐大的接口設(shè)計(jì),設(shè)計(jì)人員還可以選擇體積更小、成本更低的微控制器。嵌入式系統(tǒng)采用SPIFI外設(shè)可以提高內(nèi)存資源利用率,縮小尺寸,提高效率,降低系統(tǒng)總成本。

SPIFI外設(shè)是恩智浦LPC1800系列ARM Cortex-M3微控制器率先采用的一種專用技術(shù)。此外,即將面市的新產(chǎn)品還包括低成本Cortex-M0系列和Cortex M4數(shù)字符串行控制器(DSC)。

SPIFI支持目前市場上大部分串行閃存器件(含四通道讀/寫產(chǎn)品),配置編程非常簡便,采用4/6引腳設(shè)計(jì)(取決于串行閃存類型),支持小型寄存器組,優(yōu)化內(nèi)存事務(wù),其軟件指令可降低CPU開銷,提高內(nèi)存數(shù)據(jù)交換效率。

SPIFI工作原理

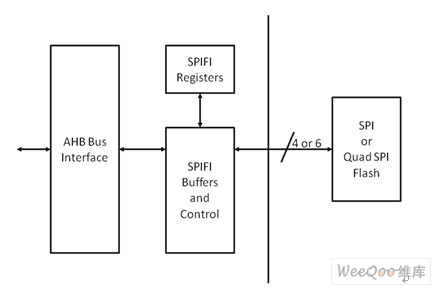

圖2給出了SPIFI外設(shè)的功能框圖。SPIFI功能塊與微控制器應(yīng)用的高速總線(AHB)矩陣連接,后者主要用于處理器內(nèi)核和片上內(nèi)存。SPIFI將外部SPI閃存內(nèi)容映射到微控制器內(nèi)存中。當(dāng)片上ROM啟動代碼激活SPIFI接口后,外部SPI內(nèi)存與核心處理單元上的片上內(nèi)存功能完全相似。

圖2:SPIFI外設(shè)功能框圖。

初始化序列

SPFI接口的所有驅(qū)動程序全部保存在ROM中。對于讀取操作,只需一個(gè)例程調(diào)用指令即可啟動SPIFI外設(shè)。初始化序列結(jié)束后,整個(gè)SPI閃存可以象正常內(nèi)存一樣由處理器和/或DMA通道按字節(jié)、半字、整字訪問。擦除和編程通過簡單的API指令訪問ROM命令調(diào)用即可,因此,使用外部SPI閃存與片上內(nèi)存幾乎沒有差別。

從SPIFI啟動

對于需要微控制器從外部串行閃存啟動的系統(tǒng),恩智浦LPC1800微控制器已配置了SPIFI啟動功能。啟動源的選擇有兩種方法:第一種是使用微控制器引腳確定啟動源的接口;第二種由用戶在非易失性內(nèi)存中編程選擇啟動接口。使用非易失性內(nèi)存編程可保留引腳的雙重功能。

物理接口

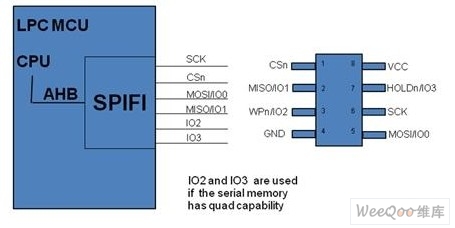

圖3給出了SPIFI外設(shè)的物理接口。本示例對于傳統(tǒng)SPI閃存采用了標(biāo)準(zhǔn)的4引腳配置,如果是四信道SPI閃存,還需要增加兩個(gè)引腳以支持四信道功能。

圖3:SPIFI外設(shè)物理接口。

不同的串行閃存廠商和產(chǎn)品需要不同的命令和命令格式。SPIFI外設(shè)為此提供了足夠的支持,可兼容大部分SPI閃存及衍生產(chǎn)品,確保今后產(chǎn)品的兼容性。

小寄存器組

SPIFI外設(shè)小寄存器組既保證了接口的功能又簡化了操作,通過8個(gè)寄存器控制SPIFI功能,連接外部SPI閃存,保存和檢索數(shù)據(jù)以及監(jiān)控操作。由于設(shè)置、編程、擦除等工作均由集成的ROM API處理,因此外部SPI內(nèi)存操作只需要幾個(gè)簡單的調(diào)用命令。總體來看,SPIFI外設(shè)配置簡單,應(yīng)用方便。

軟件命令

當(dāng)軟件讀取內(nèi)存映射的串行閃存內(nèi)容時(shí),外部閃存可以識別并接受微控制器軟件發(fā)送的和SPIFI外設(shè)自動發(fā)送的命令。這些命令可分為操作代碼、地址、中間和數(shù)據(jù)等字段,其中。地址、中間和數(shù)據(jù)字段為可選字段,這主要取決于操作代碼。部分閃存支持“讀”命令解釋操作代碼模式,以提高系統(tǒng)性能。根據(jù)操作代碼不同,數(shù)據(jù)字段可進(jìn)一步分為輸入和輸出數(shù)據(jù)字段。所有發(fā)送到外部SPI閃存的命令都可以通過調(diào)用ROM API指令進(jìn)行處理。SPIFI ROM API驅(qū)動器允許通過簡單的加載命令訪問外部SPI閃存內(nèi)容,保證應(yīng)用操作代碼延續(xù)其緊湊和易寫的特點(diǎn)。

獨(dú)立于CPU的運(yùn)行

SPIFI軟件可讀取外部閃存數(shù)據(jù),并將其寫入RAM或外設(shè),無需CPU支持。比如,對于集成LCD控制器的微控制器,此功能可以提高系統(tǒng)性能,節(jié)約功耗。外部閃存可以保存圖像并通過LCD控制器讀取。由于LCD控制器大多數(shù)按地址順序讀取數(shù)據(jù),SPIFI外設(shè)可根據(jù)需要預(yù)先獲取地址,無需等待。整個(gè)操作無需CPU參與,也不用將圖像加載到片上RAM,而由LCD控制器直接獲取。因此,系統(tǒng)對微控制器片上RAM的容量要求不高,或者可將現(xiàn)有RAM釋放出來用于完成其他任務(wù)。由于LCD控制器直接獲取圖像,LCD顯示屏圖像刷新速度更快,簡單的開關(guān)窗口等操作顯得更加平滑流暢。另外,為降低功耗,系統(tǒng)還可以使用低時(shí)鐘速率運(yùn)行,不會對顯示性能有太大影響。

直接執(zhí)行代碼

從軟件的角度看,微控制器可以直接執(zhí)行外部SPI閃存中的代碼。直接執(zhí)行代碼有利于在線升級或者更新片上閃存的出廠功能。外部閃存可以存放通過驗(yàn)證的升級代碼。例如,如果系統(tǒng)功能地址保存在片上閃存的表單中,通過外部閃存的例程地址即可對該表單重新編程。或者,如果包含原始例程起始信息的內(nèi)存頁保存在片上閃存中,通過外部分支長跳轉(zhuǎn)到外部閃存的新例程即可更新內(nèi)存頁。對于上述兩例,由于SPIFI外設(shè)可以實(shí)現(xiàn)外部閃存代碼直接執(zhí)行,因此新代碼無需加載到片上RAM。

通過外部閃存執(zhí)行代碼的速度遠(yuǎn)不及片上內(nèi)存。SPIFI外設(shè)設(shè)計(jì)并非針對需要峰值性能的實(shí)時(shí)運(yùn)行功能,但是對于執(zhí)行非關(guān)鍵代碼序列,SPIFI具有很大的吸引力。

寫/執(zhí)行并行操作功能

SPIFI支持寫功能和執(zhí)行功能同時(shí)進(jìn)行,換句話說,即使處理器正在執(zhí)行片上閃存代碼,也可以快速方便地對外部閃存進(jìn)行編程和擦除。由于SPIFI外設(shè)可以獨(dú)立運(yùn)行,不受CPU影響,因此在外部串行閃存編程的同時(shí),系統(tǒng)可以繼續(xù)執(zhí)行相關(guān)任務(wù)。

由于系統(tǒng)在執(zhí)行關(guān)鍵應(yīng)用代碼的同時(shí)可以對外部閃存進(jìn)行寫操作,因此該功能可用于在線軟件更新。例如,智能電表即使在更新軟件時(shí)也需要不間斷工作。利用SPIFI,公用工程公司可以配置系統(tǒng),向外部閃存寫入任何代碼,無需中斷智能電表的計(jì)量工作,最后再將新代碼集成到系統(tǒng)中。同樣,對于使用USB端口的系統(tǒng),新代碼可以先保存在便攜式USB驅(qū)動器中,再傳輸?shù)酵獠块W存,無需中斷重要操作。

本文小結(jié)

恩智浦LPC1800 ARM Cortex-M3微控制器首次采用的SPI閃存接口技術(shù)可以將外部閃存映射到微控制器內(nèi)存中,實(shí)現(xiàn)片上內(nèi)存功能。此項(xiàng)技術(shù)為設(shè)計(jì)人員帶來更多的外置閃存選擇機(jī)會,同時(shí)降低系統(tǒng)成本,縮小封裝尺寸。

SPIFI外設(shè)為設(shè)計(jì)人員提供了一種新的解決方案,可以利用低成本串行閃存替代昂貴的并行閃存,在縮小尺寸的同時(shí)仍能保證系統(tǒng)性能。串行閃存的低成本、小尺寸和簡化配置等眾多優(yōu)勢從此得以應(yīng)用,而對系統(tǒng)性能的影響非常小。利用SPIFI,設(shè)計(jì)人員還可以選擇無并行接口的微控制器,以小型低成本設(shè)計(jì)實(shí)現(xiàn)所需性能。

恩智浦計(jì)劃將SPIFI技術(shù)推廣到其他Cortex-M產(chǎn)品上,包括低端Cortex-M0和即將上市的Cortex-M4數(shù)字信號控制器(DSC)。