摘要:海洋儀器在后期數(shù)據(jù)分析處理時(shí)數(shù)據(jù)存儲(chǔ)電路是不可或缺的。針對(duì)海洋儀器對(duì)數(shù)據(jù)存儲(chǔ)大容量非易失的要求,結(jié)合實(shí)際工作經(jīng)驗(yàn),給出幾種擴(kuò)展海量存儲(chǔ)器的方案和實(shí)際電路。這些方案是以C8051F340為主控制器,充分利用C8051F340片上集成的I2C,SPI和I/O接口資源擴(kuò)展大容量存儲(chǔ)器,相比于傳統(tǒng)的存儲(chǔ)電路,省去了譯碼和鎖存電路,同時(shí)簡(jiǎn)化了軟件編程。經(jīng)實(shí)際應(yīng)用,這些存儲(chǔ)電路工作穩(wěn)定、功耗低,適用于中低速,需存儲(chǔ)大量數(shù)據(jù)的儀器儀表。

關(guān)鍵詞:C8051F340;I2C;SPI;I/O;非易失;大容量

在海洋儀器工作過(guò)程中,觀測(cè)的周期比較長(zhǎng),累積的數(shù)據(jù)量往往比較大,要求使用大容量存儲(chǔ)器。而且由于海洋環(huán)境惡劣,很多時(shí)候電池耗盡,儀器尚未回收,為了保證數(shù)據(jù)安全,必須采用掉電非易失存儲(chǔ)器。EEPROM和Flash閃存,既有ROM的特點(diǎn)非易失性,又有比較高的存取速度,而且易于擦除和重寫(xiě),功耗很小,集成度高,是比較好的選擇。但早期的存儲(chǔ)電路通常比較復(fù)雜,因?yàn)槠浯鎯?chǔ)器容量小,接口單一,為了擴(kuò)大容量需要外加擴(kuò)展地址線的譯碼和鎖存電路。隨著電子技術(shù)的發(fā)展,各種大容量存儲(chǔ)器層出不窮。這些存儲(chǔ)器在內(nèi)部結(jié)構(gòu)、實(shí)現(xiàn)技術(shù)、物理外觀和工作電壓等方面有較大差異,而在硬件接口上常見(jiàn)為I2C接口、 SPI接口和并行接口。

以Microehip公司生產(chǎn)的C8051F340為主控器,提出基于多種硬件接口的大容量存儲(chǔ)設(shè)計(jì)方案,可方便移植到與51兼容的其他單片機(jī)系統(tǒng)。

1 C8051F340特性及硬件接口

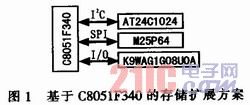

C8051F340是Sihcon公司生產(chǎn)的混合信號(hào)片上系統(tǒng)型單片機(jī)。它的內(nèi)核具有標(biāo)準(zhǔn)8052所有外設(shè),包括2個(gè)全雙工UART、1個(gè)增強(qiáng)型SPI端口,1個(gè)SMBUS端口,40個(gè)I/O引腳,4 352字節(jié)的內(nèi)部RAM,128字節(jié)特殊功能寄存器等。C8051F340片上豐富的硬件資源,使其方便擴(kuò)展不同的接口存儲(chǔ)器。圖1是基于C8051F340的硬件接口(I2C,SPI,GPIO)實(shí)現(xiàn)的3種大容量存儲(chǔ)器擴(kuò)展方案的示意圖。

2 I2C總線擴(kuò)展EEPROM存儲(chǔ)器

2.1 I2C總線

在并行總線系統(tǒng),CPU要完成與外部RAM或ROM的交換數(shù)據(jù),通常需要有3組總線(地址、數(shù)據(jù)、控制總線),采用如此多的并行總線可使控制速度快,與存儲(chǔ)器交換數(shù)據(jù)方法簡(jiǎn)單。但是,在繪制電路板時(shí),這些總線將耗費(fèi)很大空間。而I2C存儲(chǔ)器克服了這個(gè)缺點(diǎn),它僅需要數(shù)據(jù)線SDA和時(shí)鐘線SDL 2條總線即可。數(shù)據(jù)交換速率要求在ms級(jí)的場(chǎng)合,I2C存儲(chǔ)器可以取代并行存儲(chǔ)器。

2.2 AT24C1024及與C8051F340的軟硬件設(shè)計(jì)

AT24C1024是l Mb支持I2C數(shù)據(jù)傳送協(xié)議的串行CMOS EEPROM,其內(nèi)部結(jié)構(gòu)為512頁(yè),每頁(yè)為256字節(jié),可用電擦除;它具有2種寫(xiě)入方式,一種是字節(jié)寫(xiě)入方式;另一種是頁(yè)寫(xiě)入方式。允許在一個(gè)寫(xiě)周期內(nèi)同時(shí)對(duì)1個(gè)字節(jié)到l頁(yè)的若干字節(jié)的編程寫(xiě)入,l頁(yè)的大小取決于片內(nèi)頁(yè)寄存器的大小。AT24C1024具有256字節(jié)數(shù)據(jù)的頁(yè)面寫(xiě)能力。

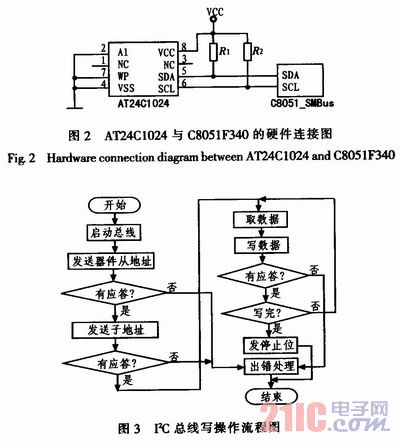

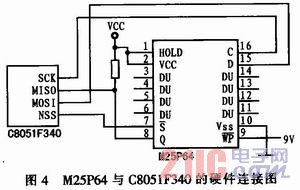

C8051F340片上集成SMBus端口。SMBus完全符合系統(tǒng)管理總線規(guī)范1.1版,并與I2C串行總線兼容。連接在I2C總線上的器件,SCL和 SDA應(yīng)該為漏極開(kāi)路或集電極開(kāi)路輸出,當(dāng)總線空閑時(shí),這2條線都被拉到高電平。所以,在配置C8051F340端口時(shí),把SDA、SCL配置為漏極開(kāi)路輸出。為了使開(kāi)漏極電路輸出“l”時(shí)SDA和SCL應(yīng)是高電平而不是高阻態(tài),這就需要加上拉電阻。圖2為AT24C1024與C805lF340的硬件連接圖。對(duì)AT24C1024的操作編程,與一般I2C類似,遵循I2C通信協(xié)議。以寫(xiě)操作為例,其流程圖如圖3所示。讀操作與此類似。

2.3 應(yīng)用舉例

此電路用于小型的海洋溫度計(jì),在采樣率為1/6 Hz、采樣精度16位的情況下,可連續(xù)存儲(chǔ)109 h左右。小型溫度計(jì)以體積小,重量輕等特點(diǎn)使其方便在海上進(jìn)行多點(diǎn)多深度布設(shè),用于測(cè)試水下溫度場(chǎng)的一天連續(xù)變化。但是AT24C1024存取速率較低,僅適合于低速存取的場(chǎng)合。在某些系統(tǒng)中還用于存儲(chǔ)系統(tǒng)配置參數(shù)和保存系統(tǒng)工作日志。

3 SHI接口擴(kuò)展M25P64

3.1 SPI總線

串行外圍接口SPI總線可分為3線和4線工作方式,支持在同一總線上掛接多個(gè)主器件和從器件。SPI收發(fā)獨(dú)立,可同步進(jìn)行,通信速率比較高。

3.2 M25P64及與C8051F340的軟硬件設(shè)計(jì)

M25P64是低功耗、大容量串行Flash存儲(chǔ)器其存儲(chǔ)空間為64 MB,由32 768個(gè)頁(yè)面組成,每個(gè)頁(yè)面為256字節(jié)。支持頁(yè)編程(256字節(jié)),扇區(qū)擦除(512 KB)和塊擦除(64MB)。最高時(shí)鐘頻率50 MHz;可循環(huán)使用100 000次;保存數(shù)據(jù)年限超過(guò)20年;該存儲(chǔ)器工作于3/4線串行總線方式,可擴(kuò)展更大容量的存儲(chǔ)空間。

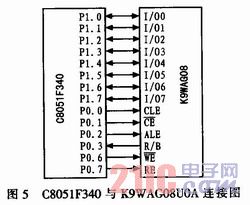

對(duì)M25P32的讀寫(xiě)可以直接將M25P64與C8051F340的GPIO口連接,采用GPIO口模擬SPI接口時(shí)序的方法。使用C8051F340的片上SPI控制接口,將引腳C與單片機(jī)輸出時(shí)鐘對(duì)接,數(shù)據(jù)輸出Q與MISO對(duì)接,數(shù)據(jù)輸入D與MOSI對(duì)接,片選信號(hào)與NSS對(duì)接,如圖4所示。

C805lF340上電后首先對(duì)硬件接口進(jìn)行初始化,把端口設(shè)置為SPI特殊功能。C8051F340通過(guò)讀寫(xiě)SPI數(shù)據(jù)寄存器(SPIDATO)實(shí)現(xiàn)在 SPI通信線上的數(shù)據(jù)收發(fā)。因此,對(duì)M25P64的讀寫(xiě)和擦除可歸結(jié)為,按照M25P64數(shù)據(jù)資料上的命令表,往SPIDAT0里寫(xiě)入命令和數(shù)據(jù),程序流程的控制

通過(guò)判斷從SPIDAT0讀出的狀態(tài)寄存器位。

3.3 應(yīng)用實(shí)例

此存儲(chǔ)電路中M25P64占用的I/O口線較少。M25P64相比于AT24C1024附加了片選信號(hào),并且數(shù)據(jù)輸入和輸出線分開(kāi),使存儲(chǔ)電路的抗干擾性有所提高,降低了軟件設(shè)計(jì)難度。M25P64在硬件實(shí)現(xiàn)上基于移位寄存器,所以通信速率較高,達(dá)到微秒級(jí)。此存儲(chǔ)電路已成功應(yīng)用于開(kāi)發(fā)的湍流觀測(cè)儀器樣機(jī)。

4 GPIO口擴(kuò)展K9WAG08UOA

C8051F340上未被交叉開(kāi)關(guān)分配的端口引腳和未被模擬外設(shè)使用的端口引腳都可以作為通用I/O。在設(shè)計(jì)C8051F340,若不把選定的引腳配置為特殊功能,它就默認(rèn)為通用I/O,利用這些引腳來(lái)擴(kuò)展K9WAG08UOA。

4.1 K9WAG08UOA的特性

K9WAG08UOA是NAND-Flash架構(gòu)的Flash,單電源2.70~3.60 V供電,內(nèi)部存儲(chǔ)空間為(1 G+32 M)x8 B,數(shù)據(jù)寄存器為(2 K+64)x8 B,可進(jìn)行任意字節(jié)單元的讀操作(最長(zhǎng)25μs),(128 K+4 K)B的塊擦除和(2 K+64)B的頁(yè)編程(200μs典型時(shí)間)。容量上可堪比一般的SD卡和U盤(pán),讀寫(xiě)速度也很快。

4.2 K9WAG08UOA與C8051F340的硬件連接

C8051F340與K9WAG08UOA的連接方法如圖5所示。K9WAG08UOA的命令、數(shù)據(jù)、地址均通過(guò)8根I/O線傳輸,31位地址分5次寫(xiě)入地址寄存器,其內(nèi)部譯碼確定塊號(hào)、塊內(nèi)頁(yè)號(hào)、頁(yè)內(nèi)字節(jié)號(hào)后尋址相應(yīng)的單元,比相同容量的并行存儲(chǔ)器節(jié)省了23根地址線。地址線的減少簡(jiǎn)化了電路設(shè)計(jì),同時(shí)也提高了編程的復(fù)雜程度。指令、地址從I/O寫(xiě)入時(shí),把拉低,配合CLE和ALE信號(hào)線實(shí)現(xiàn)I/O口上指令和地址復(fù)用。

4.3 軟件編程

K9WAG08UOA的編程比通常的串、并行存儲(chǔ)器復(fù)雜。實(shí)際應(yīng)用中將頁(yè)編程子程序、塊擦除子程序、讀操作字程序編寫(xiě)成子程序,在需要時(shí)進(jìn)行調(diào)用。由圖5 看出,C8051F340對(duì)K9WAG08UOA的讀寫(xiě)操作均通過(guò)通用I/O進(jìn)行。C805lF340對(duì)I/O端口的操作通過(guò)訪問(wèn)對(duì)應(yīng)的端口數(shù)據(jù)寄存器。向端口寫(xiě)入時(shí),數(shù)據(jù)被鎖存到端口數(shù)據(jù)寄存器中,以保持引腳上的輸出數(shù)據(jù)值不變;讀端口數(shù)據(jù)寄存器將返回端口輸入引腳的邏輯狀態(tài)。具體舉例來(lái)說(shuō),比如P0=0x80,表示Ox80被鎖存到端口數(shù)據(jù)寄存器中,把CE引腳拉低,引腳產(chǎn)生一個(gè)上升沿,數(shù)據(jù)就被寫(xiě)入K9WAG 08UOA中的數(shù)據(jù)/命令寄存器。Ox8O為命令還是數(shù)據(jù)取決于CLE和ALE的狀態(tài),CLE為高,ALE為低,表示Ox80為命令字段;CLE為低,ALE為高,表示Ox80為數(shù)據(jù)。下面對(duì)K9WAG08UOA的頁(yè)編程、頁(yè)讀、塊擦除做詳細(xì)的說(shuō)明。

4.3.1 頁(yè)編程

K9WAG08UOA的頁(yè)編程是以頁(yè)為單位的,它允許在一個(gè)頁(yè)編程周期里寫(xiě)入1~2 112字節(jié)的數(shù)據(jù)。數(shù)據(jù)被加載到數(shù)據(jù)寄存器,然后調(diào)用內(nèi)部寫(xiě)入過(guò)程寫(xiě)入正確的單元。在寫(xiě)入之前必須擦除,否則出錯(cuò)。頁(yè)編程的步驟為:1)寫(xiě)入串行輸入指令0x80;2)分5次寫(xiě)入編程首地址;3)寫(xiě)人數(shù)據(jù),一次最多2 112字節(jié);4)最后寫(xiě)入頁(yè)編程指令0x1O。啟動(dòng)內(nèi)部編程操作。為了反饋寫(xiě)入操作是否成功,K9WAG08UOA的內(nèi)部狀態(tài)寄存器記錄了寫(xiě)入狀態(tài),通過(guò)查詢寄存器狀態(tài)位O,判斷寫(xiě)入是否成功。

4.3.2 頁(yè)讀操作

K9WAG08UOA讀頁(yè)面的操作過(guò)程為寫(xiě)入0x00到命令寄存器,然后輸入5個(gè)字節(jié)的地址,再寫(xiě)入命令Ox30啟動(dòng)頁(yè)讀操作。選中頁(yè)面的2 112個(gè)字節(jié)的數(shù)據(jù)不是立即輸出到I/0口,而先被復(fù)制到K9WAG08UOA的數(shù)據(jù)寄存器。通過(guò)檢測(cè)R/B引腳狀態(tài)來(lái)判斷復(fù)制操作是否完成。一旦R/B 為高電平后,表示復(fù)制完成。微處理器器控制RE不斷的高低變化,數(shù)據(jù)寄存器中的數(shù)據(jù)將按照在芯片中的地址排列依次鎖存輸出到I/O口,此時(shí)讀取I/O口電平即可。

4.3.3 塊擦除

K9WACO8UOA的擦除操作以塊為單位進(jìn)行。首先寫(xiě)入擦除指令Ox60,然后分3次寫(xiě)入行地址。載入行地址后執(zhí)行擦除確認(rèn)指令0xd0來(lái)初始化內(nèi)部擦除操作。通過(guò)狀態(tài)引腳R/B了解擦除的進(jìn)度,R/B為高電平表示內(nèi)部擦除完成。通過(guò)檢測(cè)狀態(tài)位(I/O0)來(lái)檢查擦除操作是否發(fā)生錯(cuò)誤。

4.4 應(yīng)用舉例

本設(shè)計(jì)的單片機(jī)P1口與K9WAGO8UOA直接連接,其他控制引腳與PO口的引腳連接。為防止存儲(chǔ)器誤操作,在單片機(jī)復(fù)位后要進(jìn)行初始化設(shè)置。 K9WAGO8UOA最大的優(yōu)點(diǎn)是容量大,低功耗。海洋潛標(biāo)在水下工作的時(shí)間通常為3個(gè)月以上,累計(jì)的數(shù)據(jù)量通常上百兆,K9WAG08UOA能夠勝

任這樣的容量要求。在實(shí)驗(yàn)室水池進(jìn)行多次長(zhǎng)時(shí)間測(cè)試,K9WAG08UOA記錄的數(shù)據(jù)可靠。

5 結(jié)束語(yǔ)

利用C805lF340豐富的接口資源,可以方便地?cái)U(kuò)展大容量的存儲(chǔ)器。本文介紹的3種存儲(chǔ)器擴(kuò)展方案采用不同的硬件連接方式,但都具有非易失、低功耗的特點(diǎn),又各有特點(diǎn),可以根據(jù)系統(tǒng)開(kāi)發(fā)的具體需求,進(jìn)行選擇使用。通過(guò)實(shí)踐,總結(jié)以下經(jīng)驗(yàn):1)提高系統(tǒng)存取效率,加入FIFO緩存。數(shù)據(jù)按時(shí)間順序?qū)懭?FIFO,大到一定容量后再由處理器以塊形式讀出。這樣可以避免MCU頻繁進(jìn)入中斷,提高處理器的工作效率。2)在控制印刷電路板面積及布線復(fù)雜度上,使用I2C接口最為簡(jiǎn)潔,SPI接口次之。3)讀寫(xiě)速度上,并口Flash最快,適應(yīng)于微秒級(jí)存取;SPI接口次之,提高時(shí)鐘頻率也可達(dá)到微秒級(jí);I2C接口最慢,適合毫秒級(jí)的訪問(wèn)。4)容量上,NAND架構(gòu)閃存(K9WAG08UOA)的存儲(chǔ)單元采用串行結(jié)構(gòu),一頁(yè)包含若干字節(jié),若干頁(yè)組成儲(chǔ)存塊,這種結(jié)構(gòu)最大的優(yōu)點(diǎn)是使得容量可以做得很大。因此,在容量和存儲(chǔ)密度上,NAND閃存比其他結(jié)構(gòu)的存儲(chǔ)器大。僅從容量考慮時(shí),優(yōu)先選擇NAND架構(gòu)的閃存。