過(guò)去十年中,高速數(shù)字總線已經(jīng)獲得了令人矚目的發(fā)展,它們不僅比以往更快,而且還正在改變系統(tǒng)定時(shí)數(shù)據(jù)的方式。為提高數(shù)據(jù)吞吐量,新興的同步數(shù)字總線可以通過(guò)一套定時(shí)機(jī)制在每個(gè)時(shí)鐘周期內(nèi)多次發(fā)送數(shù)據(jù)。本文將對(duì)源同步定時(shí)如何優(yōu)化高速接口時(shí)序裕量進(jìn)行討論。

時(shí)序預(yù)算是對(duì)系統(tǒng)正常工作所需時(shí)序參數(shù)或時(shí)序要求的計(jì)算。為了使同步系統(tǒng)正常工作,其時(shí)序需求必須在一個(gè)時(shí)鐘周期內(nèi)滿足。對(duì)時(shí)序的預(yù)算涉及到許多因素,包括對(duì)保持時(shí)間和最大工作頻率的要求。通過(guò)時(shí)序預(yù)算,可以發(fā)現(xiàn)傳統(tǒng)定時(shí)方法的局限性。

圖1顯示了一個(gè)標(biāo)準(zhǔn)定時(shí)系統(tǒng)。在該圖中,一個(gè)存儲(chǔ)器控 制器與一個(gè)SRAM連接。SRAM和存儲(chǔ)器控制器都從同一個(gè)時(shí)鐘源接收時(shí)鐘信號(hào)。假設(shè)這里有意使時(shí)鐘信號(hào)電路與電路延遲相匹配,相關(guān)時(shí)序參數(shù)如下(圖 2):存儲(chǔ)器控制器tSU(建立時(shí)間)、存儲(chǔ)器控制器tH(保持時(shí)間)、主板電路tPD(傳輸延遲)、SRAM tCO(時(shí)鐘到輸出的延遲)、SRAM tDOH(輸出數(shù)據(jù)的保持時(shí)間)、時(shí)鐘發(fā)生器tSKEW(時(shí)鐘偏移)、時(shí)鐘發(fā)生器tJIT(周期抖動(dòng))以及時(shí)鐘發(fā)生器tCYC(周期時(shí)間)。

如果考慮最壞情況下的輸入建立時(shí)間、時(shí)鐘到輸出的延遲、傳輸延遲、時(shí)鐘偏移和時(shí)鐘抖動(dòng),通過(guò)計(jì)算最高頻率就可以得到系統(tǒng)的最小周期時(shí)間。最高頻率計(jì)算如下:

tCO(max, SRAM) + tPD(max) + tSU(max, CTRL) + tSKEW(max, CLK) + tJIT(max, CLK) < tCYC

通過(guò)計(jì)算保持時(shí)間可發(fā)現(xiàn)系統(tǒng)輸出數(shù)據(jù)太快,影響了系統(tǒng)接收器件的輸入保持時(shí)間。這樣,最壞情況將發(fā)生在數(shù)據(jù)最早輸出的時(shí)候。計(jì)算公式如下:

tCO(min, SRAM) + tPD(min) - tSKEW(min, CLK) - tJIT(min, CLK) > tH(max, CTRL)

現(xiàn) 在讓我們假設(shè)SRAM和存儲(chǔ)器控制器的時(shí)序參數(shù)值 為:tSU=0.5ns;tH=0.4ns;tCO=0.45ns;tDOH*=-0.45ns;tSKEW=±0.2ns;tJIT=±0.2ns。在 這種情況下,我們將使用帶有雙倍數(shù)據(jù)速率(DDR)接口的高速SRAM,SRAM在每個(gè)時(shí)鐘的上升沿和下降沿驅(qū)動(dòng)數(shù)據(jù)。

*tDOH < 0意味著在下一個(gè)時(shí)鐘上升沿/下降沿前數(shù)據(jù)已變得無(wú)效。所需的最小保持時(shí)間計(jì)算如下:

tDOH + tPD - tSKEW - tJIT > tH

-0.45 ns + tPD - 0.2 ns - 0.2 ns > 0.4 ns

-0.85ns + tPD > 0.4 ns

tPD > 1.25 ns

假設(shè)FR4電路板上走線的傳輸延遲為160ps/英寸。SRAM到存儲(chǔ)器控制器的走線長(zhǎng)度至少有7.82 in。tPD取1.2ns,最大工作頻率可計(jì)算如下。因?yàn)镾RAM有一個(gè)DDR接口,所以時(shí)序預(yù)算是基于半個(gè)時(shí)鐘周期:

tCO + tPD + tSU + tSKEW + tJIT < tCYC/2

0.45ns+1.25ns+0.5ns+0.2ns+0.2ns

2.6ns

5.2ns

192MHz>fCYC

在FR4電路板上走線的長(zhǎng)度為7.82英寸和典型時(shí)序參數(shù)的前提下,可滿足工作頻率可高達(dá)192MHz時(shí)的時(shí)序預(yù)算要求。對(duì)于那些板空間有限的系統(tǒng),7.82英寸的最小走向長(zhǎng)度約束就成了系統(tǒng)難以滿足的一個(gè)要求。

如 果無(wú)法增加走線延遲,那么通過(guò)使用延遲鎖定環(huán)/鎖相環(huán)(DLL/PLL)對(duì)時(shí)鐘信號(hào)進(jìn)行移相以更早地捕獲數(shù)據(jù),存儲(chǔ)器控制器可以滿足保持時(shí)間的要求(圖 3)。存儲(chǔ)器控制器將必須用系統(tǒng)時(shí)鐘信號(hào)來(lái)重新同步捕獲的數(shù)據(jù)。使用這個(gè)方法將會(huì)引入額外的PLL/DLL抖動(dòng),這會(huì)降低系統(tǒng)的最大工作頻率。有了這個(gè)附 加的PLL延遲后,所需的最小保持時(shí)間就變?yōu)椋?/p>

tDOH + tPD(trace) + tPLL/DLL_DELAY - tSKEW - tJIT > tH

tCO + tPD + tSU + tSKEW + tJIT + tJIT_PLL/DLL < tCYC/2

其中,tJIT_PLL/DLL是由PLL引入的延遲。即使使用最快的SRAM和ASIC/FPGA,時(shí)鐘偏移、時(shí)鐘抖動(dòng)和電路傳輸延遲也會(huì)很明顯地限制系統(tǒng)性能。

如 前所述,如果使用FR4電路板,走線延遲約為160ps/英寸。鑒于很高頻率下數(shù)據(jù)有效窗口已變?yōu)?ns(例如對(duì)250MHz的DDR器件而言)甚至更 小,這個(gè)數(shù)字是非常重要的。時(shí)鐘信號(hào)之間的偏移也會(huì)顯著減小時(shí)序裕量。我們將會(huì)看到源同步時(shí)鐘可以明顯減少傳輸延遲、偏移和抖動(dòng),使時(shí)序收斂更容易達(dá)到。

源同步定時(shí)的優(yōu)點(diǎn)

在 典型的源同步處理中,與每個(gè)數(shù)據(jù)字相關(guān)聯(lián)的時(shí)鐘上升沿被發(fā)送出來(lái)(DDR存儲(chǔ)器每個(gè)時(shí)鐘周期可能有多個(gè)數(shù)據(jù)),接收器件使用這個(gè)時(shí)鐘上升沿來(lái)鎖存數(shù)據(jù),然 后再將數(shù)據(jù)與主時(shí)鐘或公用時(shí)鐘同步。由同一個(gè)器件對(duì)時(shí)鐘信號(hào)和數(shù)據(jù)/控制信號(hào)進(jìn)行同步后傳送,實(shí)際上就消除了主板電路信號(hào)相對(duì)時(shí)鐘信號(hào)的傳輸延遲。

但是采用源同步定時(shí)就需要考慮不同的主板布線。在一個(gè)帶有獨(dú)立時(shí)鐘發(fā)生器的系統(tǒng)中,該時(shí)鐘發(fā)生器為多個(gè)器件提供時(shí)鐘信號(hào),首要的問(wèn)題是電路長(zhǎng)度的設(shè)計(jì)應(yīng)使所有的時(shí)鐘沿同時(shí)到達(dá)器件,這可能需要延長(zhǎng)連接時(shí)鐘發(fā)生器旁邊器件的走線長(zhǎng)度。

采用源同步的方法,主要的問(wèn)題是通過(guò)匹配輸出時(shí)鐘和數(shù)據(jù)信號(hào)的走線長(zhǎng)度來(lái)保持時(shí)鐘和數(shù)據(jù)之間的相位對(duì)準(zhǔn)。如果走線正確匹配,相對(duì)時(shí)鐘信號(hào)的數(shù)據(jù)傳輸延遲就不復(fù)存在了。

有很多種方法可以實(shí)現(xiàn)源同步定時(shí):

1)源同步時(shí)鐘信號(hào)的上升沿對(duì)準(zhǔn)到數(shù)據(jù)有效窗口的起始點(diǎn)。諸如QDR-II/DDR-II SRAM這樣的大多數(shù)DDR存儲(chǔ)器采用了這種方法,存儲(chǔ)器將時(shí)鐘信號(hào)和數(shù)據(jù)都發(fā)送到接收器。本文中將以它們作為例子進(jìn)行討論。

2)QDR-II產(chǎn)生一對(duì)輸出時(shí)鐘信號(hào)CQ和/CQ,理想情況下它們之間的相位差為180°,接收器利用這兩個(gè)時(shí)鐘信號(hào)的上升沿來(lái)鎖存數(shù)據(jù)。

在兩個(gè)存儲(chǔ)器中,接收器都必須將此時(shí)鐘信號(hào)延遲以滿足其捕獲數(shù)據(jù)所需要的建立和保持時(shí)間。此延遲可以通過(guò)片上延遲模塊來(lái)實(shí)現(xiàn),具體可以在接收端使用PLL或DLL,或采用板上走線延遲的方法。

這兩種方法因具有頻率轉(zhuǎn)移能力而在FPGA設(shè)計(jì)中受到青睞。為在更高頻率上使用同樣的設(shè)計(jì),可以修改FPGA代碼以改變由PLL/DLL引入的延遲。另外,ASIC總是運(yùn)行在一個(gè)特定的頻率,ASIC通常會(huì)選用板上走線延遲的方法。

也有一些源同步時(shí)鐘實(shí)現(xiàn)方案,在源端將其源同步時(shí)鐘信號(hào)延遲,在數(shù)據(jù)有效窗口的中心對(duì)齊。在這種情況下,用戶可以直接實(shí)現(xiàn)源同步時(shí)鐘信號(hào)來(lái)鎖存接收器的數(shù)據(jù)(假設(shè)時(shí)鐘和數(shù)據(jù)之間的走線匹配)。

抖動(dòng)的影響

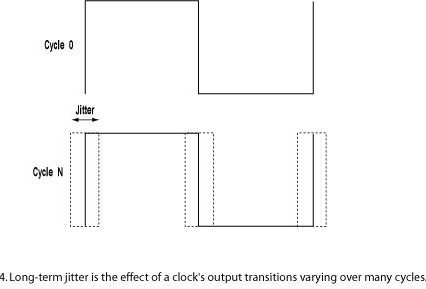

抖 動(dòng)可以被定義為時(shí)鐘位轉(zhuǎn)換與理想時(shí)序偏離,時(shí)鐘位轉(zhuǎn)換可能超前或滯后,這里有多種不同類型的抖動(dòng)。周期間抖動(dòng)是時(shí)鐘輸出位轉(zhuǎn)換中與前一個(gè)周期相應(yīng)位置的偏 離(參見(jiàn)圖2)。周期抖動(dòng)用來(lái)衡量時(shí)鐘輸出位轉(zhuǎn)換與理想時(shí)序的最大偏離。長(zhǎng)期抖動(dòng)用來(lái)衡量在多個(gè)周期的時(shí)鐘輸出位轉(zhuǎn)換中與理想時(shí)序的最大偏離,這里的“多 個(gè)周期”的具體數(shù)目取決于具體的應(yīng)用和工作頻率(圖4)。

根據(jù)具體的應(yīng)用,在時(shí)序預(yù)算中應(yīng)考慮其中一種或所有三種類型的抖動(dòng)。在同步定時(shí)環(huán)境中,產(chǎn)生輸入時(shí)鐘的時(shí)鐘源或PLL/DLL一般會(huì)引起抖動(dòng)變化。在時(shí)序預(yù)算中考慮了抖動(dòng)因素后,抖動(dòng)(tJIT)就會(huì)顯著地縮小時(shí)序裕量,特別在高頻率下。

但是,如果在接收端時(shí)鐘和數(shù)據(jù)存在相同的抖動(dòng),就可以從時(shí)序預(yù)算中除去抖動(dòng)成分(tJIT)。采用源同步時(shí)鐘的情況下也是如此,這是時(shí)鐘信號(hào)和數(shù)據(jù)由同一個(gè) 發(fā)射器件驅(qū)動(dòng)并一直保持對(duì)準(zhǔn)。將時(shí)鐘設(shè)計(jì)得像其中一個(gè)輸出時(shí),通常就會(huì)產(chǎn)生這樣的效果。雖然仍必須考慮時(shí)鐘和數(shù)據(jù)管腳之間時(shí)鐘到輸出的時(shí)間變化,但這個(gè)參 數(shù)一般都在±100ps左右。

在某些應(yīng)用中,源同步時(shí)鐘被延遲1個(gè)周期以上以鎖存數(shù)據(jù)。這種情況下,時(shí)序預(yù)算中要考慮長(zhǎng)期抖動(dòng),這將使時(shí)序裕量減小。這種抖動(dòng)也被稱為N周期抖動(dòng),N是相對(duì)于數(shù)據(jù)信號(hào),源同步時(shí)鐘信號(hào)被延遲的周期數(shù)。當(dāng)然,一般不建議將源同步時(shí)鐘信號(hào)延遲一個(gè)周期以上。

時(shí)序預(yù)算的計(jì)算

從下面的例子中可以看出,從時(shí)序預(yù)算中消除傳輸延遲可以大大改善系統(tǒng)時(shí)序裕量。圖5給出了采用源同步時(shí)鐘的SRAM的例子。

讓我們按下面步聚計(jì)算時(shí)序預(yù)算。按照設(shè)計(jì),SRAM輸出時(shí)鐘信號(hào)的上升沿與數(shù)據(jù)有效窗口的起始邊對(duì)準(zhǔn)。我們假設(shè)存儲(chǔ)器控制器通過(guò)PLL/DLL片上延遲時(shí)鐘延遲以滿足建立和保持時(shí)間。SRAM和存儲(chǔ)器控制器采用相同的時(shí)序參數(shù)。

假設(shè)時(shí)鐘和數(shù)據(jù)走線長(zhǎng)度匹配,計(jì)算時(shí)序預(yù)算時(shí)就可以忽略電路傳輸延遲tPD。另外,時(shí)鐘與數(shù)據(jù)具有同樣的偏移和抖動(dòng)(不包括管腳之間±100 ps的偏移),因此無(wú)需再考慮時(shí)鐘發(fā)生器抖動(dòng)和偏移(tSKEW, tJIT)。

在這個(gè)系統(tǒng)中,需要考慮的另外一個(gè)參數(shù)是SRAM的tJIT:相對(duì)于數(shù)據(jù)的SRAM輸出源同步時(shí)鐘抖動(dòng)。這可能是由管腳間時(shí)鐘到輸出的時(shí)間變化而引起的。

在 這個(gè)例子中,我們假設(shè)時(shí)鐘和數(shù)據(jù)走線匹配地很好。如果由于電路設(shè)計(jì)而導(dǎo)致走線長(zhǎng)度出現(xiàn)差異,就必須考慮時(shí)鐘和數(shù)據(jù)信號(hào)走線長(zhǎng)度的差異。如果時(shí)鐘信號(hào)的走線 是有意延長(zhǎng)以延遲時(shí)鐘信號(hào)(將時(shí)鐘信號(hào)與數(shù)據(jù)有效窗口中心對(duì)準(zhǔn)),就不用考慮此參數(shù)。假設(shè)SRAM源同步時(shí)鐘抖動(dòng)為tJIT=±0.2ns,我們可以像表 中列出的那樣逐步計(jì)算最小周期時(shí)間(參見(jiàn)表)。要獲得非負(fù)值裕量,應(yīng)滿足如下條件:

tM>0

tCYC/2-2.2ns>0

tCYC/2>2.2ns

tCYC>4.4ns

fCYC<227MHz

本例采用源同步時(shí)鐘信號(hào),滿足建立和保持時(shí)間要求,對(duì)數(shù)據(jù)信號(hào)走線長(zhǎng)度也沒(méi)有什么約束。計(jì)算得到的最大工作頻率是277MHz,比傳統(tǒng)時(shí)鐘同步方法提高了35MHz。注意本例中主要的頻率限制因素是控制器的建立和保持時(shí)間。

使用源同步時(shí)鐘的最優(yōu)方法

為最好地利用源同步時(shí)鐘,設(shè)計(jì)工程師應(yīng)注意以下要點(diǎn):

不 要使源同步時(shí)鐘的延遲時(shí)間超過(guò)一個(gè)周期。源同步時(shí)鐘的上升沿與其所驅(qū)動(dòng)的數(shù)據(jù)信號(hào)是嚴(yán)格匹配的,所以時(shí)鐘和數(shù)據(jù)信號(hào)應(yīng)具有同樣的抖動(dòng)并互相抵消。如果將源 同步時(shí)鐘信號(hào)的上升沿延遲到下一個(gè)周期以鎖存數(shù)據(jù),那么就必須考慮另外一個(gè)抖動(dòng)成分,即N周期抖動(dòng),N是相對(duì)于數(shù)據(jù)信號(hào),時(shí)鐘信號(hào)被延遲的周期數(shù)。圖6和 圖7中給出了使用源同步時(shí)鐘的推薦方法和不推薦方法。這些例子采用QDR-II源同步時(shí)鐘(CQ和/CQ)。

注意:如果有兩個(gè)源同步時(shí)鐘,最好兩個(gè)都用到。