摘 要: 介紹了DVB-T" title="DVB-T">DVB-T解調(diào)器的整體結(jié)構(gòu),并設(shè)計(jì)了一種多模塊間進(jìn)行數(shù)據(jù)傳輸?shù)臋C(jī)制,同時(shí)還設(shè)計(jì)了前FFT同步系統(tǒng),其中包括了基帶變換、粗符號(hào)同步和分?jǐn)?shù)頻率同步。

關(guān)鍵詞: DVB-T 同步 多路" title="多路">多路交叉開(kāi)關(guān)

在無(wú)線信道中存在著多徑衰落,嚴(yán)重影響了數(shù)據(jù)傳輸速率的提高。而正交頻分復(fù)用(OFDM)技術(shù)具有很好的抗多徑能力,因此歐洲的DVB-T標(biāo)準(zhǔn)采用了OFDM技術(shù)進(jìn)行高質(zhì)量的視頻傳輸。這項(xiàng)標(biāo)準(zhǔn)已經(jīng)被世界上很多國(guó)家采納為自己的地面數(shù)字電視傳輸標(biāo)準(zhǔn)。

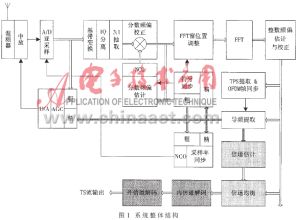

1 系統(tǒng)整體結(jié)構(gòu)

系統(tǒng)設(shè)計(jì)的輸入中頻信號(hào),直接對(duì)中頻信號(hào)進(jìn)行亞采樣。系統(tǒng)分為前FFT同步、FFT、后FFT同步與TPS解調(diào)、信道均衡與校正、信道解碼五個(gè)模塊。如圖1所示。經(jīng)過(guò)前FFT同步模塊,數(shù)據(jù)被變換為速率為9.14MS/s的復(fù)數(shù)基帶信號(hào),同時(shí)去掉保護(hù)間隔;經(jīng)FFT變換后數(shù)據(jù)被變換到頻域;后FFT同步模塊在頻域中完成整數(shù)頻偏的估計(jì)與校正、精符號(hào)偏移與采樣率偏移的估計(jì)、TPS解調(diào)與導(dǎo)頻提取;然后信道估計(jì)" title="信道估計(jì)">信道估計(jì)與均衡模塊利用提取的導(dǎo)頻進(jìn)行CPE估計(jì)與校正、信道估計(jì)與均衡;接下來(lái)在信道解碼模塊中完成星座解映射、解符號(hào)交織、解比特交織、Viterbi譯碼、解卷積交織、RS譯碼、解能量擴(kuò)散,最后輸出TS流數(shù)據(jù)。

2 數(shù)據(jù)傳輸

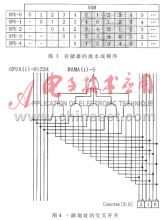

解調(diào)器中包括5個(gè)大的模塊,這5個(gè)模塊之間存在大量的數(shù)據(jù)交換。為了提高數(shù)據(jù)傳輸?shù)男什⒔档痛鎯?chǔ)單元的消耗,筆者采用了如圖2所示的以一個(gè)多路交叉開(kāi)關(guān)" title="交叉開(kāi)關(guān)">交叉開(kāi)關(guān)為核心的數(shù)據(jù)傳輸模塊來(lái)完成這5個(gè)模塊之間的數(shù)據(jù)交換。

OPU-i表示5個(gè)模塊,稱(chēng)為運(yùn)算單元,而RAM-i表示5個(gè)RAM塊,5個(gè)運(yùn)算單元以流水線的方式交替使用這5個(gè)RAM塊,流水線節(jié)拍如圖3所示。OPU-0主要完成基帶變換,F(xiàn)FT前同步;OPU-1主要完成FFT變換;OPU-2主要完成FFT后同步;OPU-3主要完成信道估計(jì)與均衡;OPU-4主要完成信道解碼。其中一路地址的交叉開(kāi)關(guān)如圖4所示。

可以看出1 bit地址信號(hào)的交叉開(kāi)關(guān)需要5個(gè)四輸入與門(mén)和1個(gè)五輸入或門(mén),總共按照32 bit數(shù)據(jù)(雙向)和12 bit地址計(jì)算,則需要380個(gè)四輸入與門(mén)和76個(gè)五輸入或門(mén),而且沒(méi)有一路信號(hào)只經(jīng)過(guò)兩級(jí)門(mén)延遲。因此從實(shí)現(xiàn)規(guī)模和信號(hào)延遲上看,這個(gè)多路交叉開(kāi)關(guān)都是容易實(shí)現(xiàn)的。這個(gè)模塊在Altera Stratix1S25 FPGA上驗(yàn)證,其存取速度可以達(dá)到100MHz以上。

2.1 基帶變換模塊

本系統(tǒng)設(shè)計(jì)的中頻輸入頻率為36.5714MHz,亞采樣速率為:27.42855MHz,設(shè)ω0=9.14285MHz,低通濾波器的通帶歸一化截止頻率為0.277488966788,阻帶歸一化截止頻率為0.3891776998784。通帶內(nèi)平坦度要求小于0.002dB,阻帶抑制要求大于60dB,這個(gè)低通濾波器用一個(gè)74階的FIR低通濾波器實(shí)現(xiàn)。基帶變換模塊結(jié)構(gòu)如圖5,其中NCO為數(shù)控振蕩器,與一個(gè)復(fù)數(shù)乘法器" title="乘法器">乘法器一起完成基帶變換、IQ分離和分?jǐn)?shù)頻偏校正的功能,結(jié)構(gòu)如圖6所示。

復(fù)數(shù)乘法器采用Cordic算法實(shí)現(xiàn)[1],相位累加器根據(jù)輸入的振蕩頻率調(diào)整相位累加的步長(zhǎng),其輸出為本地載波的相位。Cordic乘法器的一個(gè)乘數(shù)為采樣數(shù)據(jù),另一個(gè)乘數(shù)就是本地載波的相位,其兩個(gè)輸出分別為輸入數(shù)據(jù)與cos和sin相乘的結(jié)果。乘法器的輸出進(jìn)入上面所描述的74階FIR低通,然后直接進(jìn)行3倍抽取從而獲得速率為9.14MS/s的數(shù)字基帶信號(hào)。

2.2 粗符號(hào)同步

粗符號(hào)同步模塊包括粗符號(hào)同步估計(jì)、FFT窗位置調(diào)整、分?jǐn)?shù)頻率偏移估計(jì)。

2.2.1 粗符號(hào)同步估計(jì)

粗符號(hào)同步和分?jǐn)?shù)頻偏采用基于TGI的聯(lián)合估計(jì)算法[2],它利用TGI相關(guān)進(jìn)行同步估計(jì)。具體算法參見(jiàn)參考文獻(xiàn),實(shí)現(xiàn)結(jié)構(gòu)如圖7所示。其中N_FFT=2048;N_TGI是保護(hù)間隔的長(zhǎng)度,可以為N_FFT的1/32、1/16、1/8、1/4四個(gè)值。

在相關(guān)結(jié)果取絕對(duì)值后有一個(gè)峰值搜索和鎖定環(huán)路,峰值搜索是為了尋找到粗符號(hào)同步位置,但是由于這個(gè)算法直接估計(jì)出的粗符號(hào)同步位置會(huì)有10個(gè)樣點(diǎn)左右的抖動(dòng),這個(gè)抖動(dòng)會(huì)影響后FFT同步的估計(jì),因此這里引入一個(gè)鎖定環(huán)路來(lái)穩(wěn)定這個(gè)抖動(dòng)。峰值搜索對(duì)過(guò)門(mén)限的信號(hào)峰值進(jìn)行搜索。

2.2.2 FFT窗位置調(diào)整

FFT窗位置調(diào)整模塊結(jié)構(gòu)圖如圖8所示。利用粗符號(hào)同步信號(hào)同步地將數(shù)據(jù)寫(xiě)入深度為N_FFT+N_TGI的FIFO,精符號(hào)同步調(diào)整控制模塊產(chǎn)生輸出數(shù)據(jù)的選通信號(hào),以去掉TGI,實(shí)際是利用一個(gè)向下計(jì)數(shù)器,計(jì)數(shù)初始值由精符號(hào)同步估計(jì)出的精符號(hào)同步誤差決定,計(jì)數(shù)器的啟動(dòng)由粗符號(hào)同步信號(hào)控制,當(dāng)計(jì)數(shù)器下溢時(shí)停止計(jì)數(shù),并產(chǎn)生輸出使能信號(hào)。N_SYM=N_FFT+N_TGI。

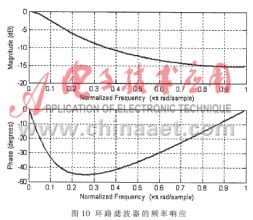

2.2.3 分?jǐn)?shù)頻偏鎖定環(huán)路

圖9為分?jǐn)?shù)頻偏鎖定環(huán)路,其中FD為頻率檢測(cè)器,按照?qǐng)D7描述的算法進(jìn)行分?jǐn)?shù)頻率偏移的估計(jì)。LF為環(huán)路濾波器,其傳輸函數(shù)為:![]() ,其中K1=0.02,K2=-0.7,其頻率響應(yīng)如圖10所示。

,其中K1=0.02,K2=-0.7,其頻率響應(yīng)如圖10所示。

ACC為累加器。NCO即圖 5中所描述的數(shù)控振蕩器。

參考文獻(xiàn)

1 李 滔,韓秋月. 基于流水線Cordic算法的三角函數(shù)發(fā)生器.電子技術(shù)應(yīng)用,1999;25(6)

2 A Comparison of Time and Frequency Synchronization Algo-rithms for European DVB-T System. J.Echavarri, IEEE, 1999

3 張厥盛.鎖相技術(shù).西安:西安電子科技大學(xué)出版社,1994

4 Digital Video Broadcasting (DVB); Framing structure. channel coding and modulation for digital terrestrial television. ETSI, 2001.1