O 引言

Flash是一種非易失存儲器,它在掉電條件下仍然能夠長期保持數據。由于它具有容量大、速度快、功耗低、抗震性能好等優(yōu)點,近幾年在U盤、SD卡、SSD硬盤等各種移動存儲設備中得到了廣泛的應用。本文給出了一款性能優(yōu)異、成本低廉可用于SD卡的NAND flash控制芯片的設計方法。(本方法也同樣適用于其他存儲設備。文中集中探討了一種高效管理物理塊的算法,包括邏輯物理地址映射以及spare區(qū)的定義,另外,還有雙緩沖器優(yōu)化讀寫的方法等。

1 Flash簡介

1.1 SLC flash與MLC flash的比較

從架構上,flash可以分為SLC(Single-Level-Cell) flash和MLC(Multi-Level-Cell)flash兩種。和SLC Flash相比較,MLC flash的優(yōu)點是面積小、成本低:缺點是出錯率高,壽命短(SLC的每個block能夠擦寫100,000次,而MLC能夠擦寫10,000次)。由于MLC flash具有成本低的優(yōu)勢,而其出錯率高的缺陷又可以通過ECC(Error Correction Code)糾錯來有效解決,壽命短的問題也可以通過磨損均衡來彌補,因此,MLC flash的應用更加廣泛,但在一些高端應用仍然會使SLCflash。本設計就是針對MLC flash,但是,本方法對SLC flash也能夠處理。

1.2 NAND flash結構

不同廠商不同型號的flash的結構都大同小異,圖l所示是三星K9G8G08UOA型號的flash結構圖,圖l中的1個flash芯片包含4096個物理塊(block),每個物理塊含有128個頁(page),每個頁包含2112(2048+64)字節(jié)其中多出的64字節(jié)用于存放糾錯碼及其他信息用。

1.3 NAND flash的特點

Flash可支持讀(Read)操作、寫(Program)操作和擦除(Erase)操作。其中讀操作和寫操作的基本單位是頁,擦除操作的基本單位是塊。對flash的寫入操作只能在尚未寫入的空閑頁上進行,并且只能按照從低地址頁到高地址頁的順序進行操作,而不能寫了高地址頁之后,再寫低地址頁。如果想要修改某個已經寫過的頁,只能先對整個物理塊進行擦除,然后才能正確寫入。

2 Flash管理算法

2.1 邏輯物理地址映射

由于flash具有上述特點,因此,如果不采用邏輯物理地址映射,將會存在兩個問題:其一是Flash中難免會有壞塊,因而某些地址空間將是不可用的;其二,F(xiàn)lash讀寫的基本單位是頁,擦除的基本單位是塊,故在同一個頁的兩次寫之間,就必須要進行一次擦除操作,而擦除會擦除掉整個塊,這樣,為了避免其他頁的數據丟失,就得先把這些頁中的數據暫存到其他地方備份起來,之后再和新數據一起重新寫回到該塊中,因此,整個過程會比較復雜,而且會造成速度降低。這樣,一般都需要對flash加入邏輯物理地址映射管理算法,該算法的邏輯地址和物理地址的對應關系是變動的。

2.2 兩級地址映射

為了減少更新數據時原有數據的搬移,提高寫操作的速度,本文提出了采用兩級地址映射的機制,也就是在塊級別邏輯物理地址映射的基礎上引入頁級別上的邏輯物理地址映射。一個邏輯塊對應一個或兩個物理塊(稱為母塊和子塊),邏輯塊中的邏輯頁對應一或兩個物理塊中的某個面。圖2所示是其地址解析示意圖。

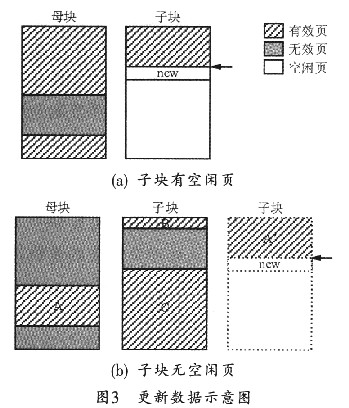

在讀寫時,首先應將邏輯地址分為邏輯塊地址和邏輯頁地址,再根據塊映射表將邏輯塊地址映射到物理塊地址,然后讀取母塊和子塊中的sDare區(qū),并據此建立頁映射表,再根據邏輯頁地址映射到物理頁地址,從而完成從邏輯地址到物理地址的轉換。其數據更新示意圖如圖3所示。

當需要更新數據時,寫入的策略可分為兩種情況。首先,當子塊仍然有空閑頁時,可直接將數據寫到子塊中的下一個空閑頁中,并在spare區(qū)中記錄該塊對應的子塊、該物理塊對應的邏輯塊以及該物理頁對應的邏輯頁,這樣,當重新上電時,就可以建立邏輯物理映射關系。其次,當母塊和子塊都寫滿時,需要從空塊池中取出一個新的子塊。如果允許一個邏輯塊對應三個或更多的物理塊,一方面管理起來比較復雜,另外也會造成空物理塊緊缺,因此,可以考慮將母塊或者子塊釋放掉,這樣,母塊或者子塊中原有的有效數據就需要搬移到新子塊中并將該母塊或子塊擦除再釋放到空塊池。出于速度的考慮,選擇母塊和子塊有效頁數較少的塊進行數據轉移并釋放。

實踐證明,這樣操作對寫文件速度有明顯提高,特別是寫小文件時,其速度提升可達9.2倍。

2.3 SPARE區(qū)和ECC校驗

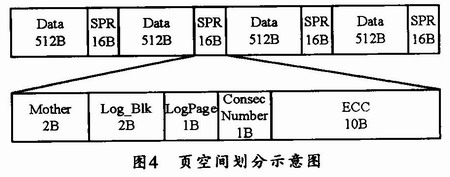

Flash中每個頁里的每個字節(jié)都是沒有任何差別的,物理上并沒有data區(qū)和spare區(qū)的區(qū)別,具體怎樣劃分data區(qū)和spare區(qū),可由用戶自己決定。本設計采用的劃分辦法如圖4所示,這樣,每個扇區(qū)和一個spare區(qū)相連,故可方便連續(xù)讀出,并進行校驗糾錯。

圖4中同時給出了Spare的區(qū)定義,其中兩字節(jié)用于標識本物理塊所對應的母塊;兩字節(jié)用于標識本物理塊對應的邏輯塊;一字節(jié)用于標識本物理頁對應的邏輯頁,一字節(jié)用于標識連續(xù)邏輯頁數(表示上面連續(xù)邏輯頁的個數,此域可以輔助加快建立頁映射表的時間),余下的10字節(jié)用于存放ECC,這樣可以達到4字節(jié)錯誤的糾錯能力。一般情況下,前面的4個字節(jié)是建立塊地址映射表的關鍵,其次,后面兩個字節(jié)則是建立頁地址映射表的關鍵。

2.4 頁映射表建立時間的優(yōu)化

因為建立頁映射表需要讀取母塊和子塊中各物理頁spare區(qū)以判定該物理頁對應的邏輯頁,而每個物理頁的讀取都要花費大約50μs的時間。因此,如果對每個物理頁都讀取,建立頁映射表就會比較費時。為了加快建立頁映射表的速度,一般只希望能讀取一個物理頁,而免于讀取其他若干頁,以便加快建表速度。因為很多時候都是連續(xù)寫,而連續(xù)的幾個物理頁在邏輯上也是連續(xù)的,因此可以考慮在spare區(qū)加入連續(xù)邏輯頁號,這樣,重新建表時,就可根據連續(xù)頁號知道連續(xù)幾個物理頁對應的邏輯頁,從而加快建表的速度。對于最佳情形,有時只需要讀一個頁就可以建立整個邏輯塊的頁映射表。圖5所示是一種加快建表的示意圖。

2.5 分區(qū)

不同的flash,塊數是不同的,其塊映射表需要的RAM空間也不一樣。對于當前主流flash,有的具有8192個塊,如果對整個flash建表,需要的RAM空間將多達32KB,這樣芯片成本就會比較高。一個可行的解決辦法是對flash分區(qū),比如1024個塊為一個分區(qū),每次只對一個分區(qū)進行建表,這樣,RAM空間就可以降低到4KB。這樣,隨著將來flash容量的增加,塊數即使再多,也能夠用同樣的方法處理,而不用增大RAM。

3 結束語

本文介紹了一種針對MLC flash的優(yōu)異管理算法及軟件實現(xiàn)方法,并且已在SD卡上大規(guī)模商用。該算法只需簡單配置就能支持市場上的各種flash,而且也兼容各種SD設備。同時RAM空間需求小,成本低,壽命長,兼容性好,擴展性強,flash空間利用率高,具有很高的商用價值。