O 引言

目前市面上有多種數(shù)據(jù)采集卡,但其應(yīng)用都具有一定的局限性,不可能完全滿足用戶的需求。本文介紹的數(shù)據(jù)采集卡可應(yīng)用于某視頻圖像采集系統(tǒng)中,數(shù)據(jù)源發(fā)送多路同步串行數(shù)據(jù),然后經(jīng)過數(shù)據(jù)采集卡傳入上位機(jī)用以進(jìn)行后續(xù)分析。上位機(jī)向外寫控制字并轉(zhuǎn)換后以異步串行方式輸出。用以控制視頻圖像的采集。本系統(tǒng)將PCI接口邏輯和其他用戶邏輯集成于一片F(xiàn)PGA中,因而大大節(jié)省了資源,便于進(jìn)行串口擴(kuò)展及其他功能的添加,性能良好,用途廣泛。

1 PCI總線

PCI總線是一種高性能的局部總線,具有32位可升級(jí)到64位的、獨(dú)立于CPU的總線結(jié)構(gòu)。工作頻率為33/66 MHz,最高傳送速度可達(dá)132 MB/s(32位、33 MHz)或528 MB/s(64位、66 MHz)。

PCI總線定義了Memory(存儲(chǔ)器)空間、I/O(輸入/輸出)空間和配置空間3種地址空間,并具有兩種工作模式:其中主模式下的PCI設(shè)備具有總線控制權(quán),可以實(shí)現(xiàn)DMA傳輸;而被主設(shè)備控制進(jìn)行通信的稱為從模式(TARGET)。

1.1 PCI總線的配置空間

所有的PCI設(shè)備都必須實(shí)現(xiàn)配置空間,該空間分為首部區(qū)和設(shè)備有關(guān)區(qū)。首部區(qū)中的強(qiáng)制性寄存器有:供應(yīng)商代碼(Vendor ID)寄存器用于標(biāo)明設(shè)備制造商),設(shè)備代碼(Device ID)寄存器(用于指明特定的設(shè)備,它由供應(yīng)商分配),版本識(shí)別(Revision ID)寄存器,首部類型(He-ader Type)寄存器和類別寄存器(Class Code)。以上五個(gè)寄存器均可用于PCI總線上設(shè)備的識(shí)別。另外,首部區(qū)中還有兩種必須實(shí)現(xiàn)的寄存器:其中命令寄存器用于存放PCI命令,而設(shè)備狀態(tài)寄存器則用于記錄PCI的狀態(tài)信息。

操作系統(tǒng)在啟動(dòng)時(shí)應(yīng)判斷系統(tǒng)中有多少存儲(chǔ)器、以及I/O設(shè)備需要多少地址空間,然后建立統(tǒng)一的地址映射關(guān)系,這時(shí)的PCI設(shè)備需要用到基地址寄存器。另外,若要實(shí)現(xiàn)中斷,還必須設(shè)置中斷引腳(Interrupt Pin)寄存器和中斷線(Interrupt Line)寄存器。

1.2 PCI總線的中斷機(jī)制

PCI總線的硬件中斷方式分為邊沿觸發(fā)和電平觸發(fā),PCI設(shè)備為低電平觸發(fā)(level-sensitive)。PCI總線上有4條中斷請(qǐng)求信號(hào)線:INTA #、INTB#、INTC#、INTD#,中斷引腳寄存器的值01H~04H分別對(duì)應(yīng)4條中斷線,單功能PCI設(shè)備只能使用INTA#。此外,使用了中斷引腳的設(shè)備還必須實(shí)現(xiàn)中斷線寄存器。POST例程(加電自檢測(cè)程序)在進(jìn)行系統(tǒng)初始化和配置時(shí)還要將中斷線信息寫入該寄存器。PCI總線中斷是可以共享的,這一方面解決了中斷資源緊張的問題,但另一方面也會(huì)給PCI中斷的實(shí)現(xiàn)帶來麻煩。

2 系統(tǒng)硬件實(shí)現(xiàn)

2.1 PCI配置寄存器的設(shè)置

Altera公司的PCI編譯器(PCI Compiler)提供有使用Altera器件實(shí)現(xiàn)PCI接口設(shè)計(jì)的完全解決方案。其中包括4種PCI接口兆核函數(shù)(PCI IP)及相關(guān)測(cè)試平臺(tái)。

通過PCI編譯器的IP工具臺(tái)或直接編輯生成的兆核函數(shù)頭文件可以設(shè)置并修改PCI的配置空間信息,本系統(tǒng)的主要配置信息如下:

2.2 PCI T32兆核函數(shù)的內(nèi)部結(jié)構(gòu)及外圍信號(hào)

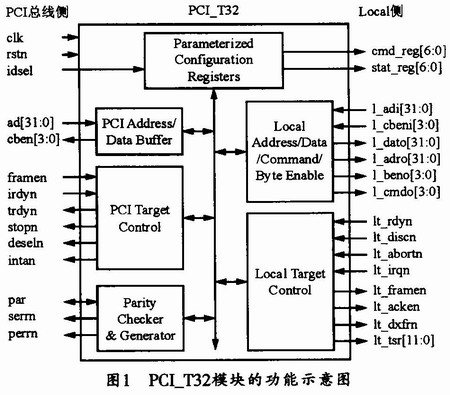

PCI Compiler提供的四種PCI IP包括PCI_M64/32、64/32位的主模式接口和PCI_T64/32、64/32位的從模式接口。本系統(tǒng)通過PCI接口與PC機(jī)傳輸32位數(shù)據(jù),并由上位機(jī)應(yīng)用程序控制系統(tǒng)工作。故該系統(tǒng)工作于32位從模式,即本系統(tǒng)的PCI接口使用PCI_T32模塊來實(shí)現(xiàn),該模塊的內(nèi)部功能及外圍信號(hào)如圖1所示。

參數(shù)配置寄存器(Parameterizde Configuration Registers)是符合PCI規(guī)范的所有配置的寄存器,可用于識(shí)別設(shè)備、控制PCI總線功能、提供PCI總線狀態(tài)等,PCI側(cè)從模式控制模塊(PCI Target Control)用于控制PCI_T32與PCI總線的各種操作,而用戶側(cè)從模式控制模塊(Local Target Control)則用于控制PCI_T32與用戶邏輯的各種操作。

PCI_T32上PCI總線一側(cè)的信號(hào)是符合PCI協(xié)議的標(biāo)準(zhǔn)信號(hào),該信號(hào)Local側(cè)的信號(hào)為Altera PCI IP特有的與用戶邏輯接口的信號(hào),起著關(guān)鍵作用。其中:

l_adi[31:0]為地址/數(shù)據(jù)輸入信號(hào);

l_dato[31:0]為數(shù)據(jù)輸出信號(hào);

l_adro [31:0]為地址輸出信號(hào),讀操作時(shí),可將PCI側(cè)地址/數(shù)據(jù)信號(hào)AD[31:0]上的第一個(gè)有效周期(即地址期)的數(shù)據(jù)輸出;

l_emdo[3:0]為命令輸出信號(hào),其位定義及時(shí)序符合PCI規(guī)范,其為0010時(shí)為I/O讀操作,為0011時(shí)為I/O寫操作、為0110時(shí)為內(nèi)存讀操作。為0111時(shí)為內(nèi)存寫操作,為1010時(shí)為配置空間讀,為1011時(shí)為配置空間寫,用戶對(duì)這組信號(hào)進(jìn)行譯碼可知其當(dāng)前PCI總線上設(shè)備的操作情況;

l_irqn為用戶中斷請(qǐng)求信號(hào),由于PCI總線為低電平中斷,所以,用戶邏輯若要發(fā)出PCI中斷請(qǐng)求,就必須將低脈沖送入l_irqn。實(shí)驗(yàn)證明,低脈沖持續(xù)時(shí)間須在4~8μs之間,持續(xù)時(shí)間過短會(huì)出現(xiàn)丟失中斷現(xiàn)象,而時(shí)間過長時(shí),操作系統(tǒng)又會(huì)重復(fù)響應(yīng)同一個(gè)中斷請(qǐng)求;

l_tsr[11:0]可用于控制local目標(biāo)設(shè)備狀態(tài)寄存器,其中D0~D5位分別對(duì)應(yīng)BAR0~BAR5,哪位有效代表哪個(gè)BAR被選中;

l_dxfrn為輸出信號(hào),表示local目標(biāo)設(shè)備數(shù)據(jù)傳輸成功。

2.3 FAGA邏輯設(shè)計(jì)

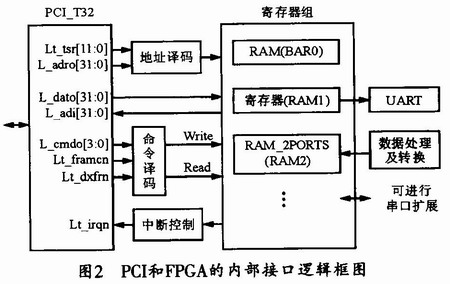

一個(gè)數(shù)據(jù)采集系統(tǒng)若要穩(wěn)定可靠地采集數(shù)據(jù),都需要設(shè)置合適的數(shù)據(jù)緩沖區(qū),本系統(tǒng)的數(shù)據(jù)緩沖區(qū)由FPGA內(nèi)部IP核實(shí)現(xiàn)。圖2所示為FPGA內(nèi)部的PCI接口及數(shù)據(jù)緩沖區(qū)框圖。

同步串行通信對(duì)時(shí)鐘的同步要求非常嚴(yán)格,設(shè)計(jì)時(shí)應(yīng)該注意收/發(fā)兩方必須使用同一時(shí)鐘來控制數(shù)據(jù)的傳輸。另外,PCI_T32內(nèi)存讀寫分為單周期模式和突發(fā)模式。突發(fā)模式即在給出首地址后主設(shè)備連續(xù)讀寫多個(gè)數(shù)據(jù),這在FPGA中需要用戶端地址每周期自動(dòng)增1的操作。

3 系統(tǒng)軟件開發(fā)

3.1 驅(qū)動(dòng)程序

PCI設(shè)備的硬件資源由Windows操作系統(tǒng)根據(jù)PC機(jī)中所有設(shè)備對(duì)資源的占有來統(tǒng)一分配。為了保證系統(tǒng)的安全和穩(wěn)定性,在Windows2000及其后的微軟操作系統(tǒng)中,運(yùn)行在ring3層的用戶應(yīng)用程序無法直接訪問硬件,而必須通過運(yùn)行于ring0層的設(shè)備驅(qū)動(dòng)程序來訪問。設(shè)備驅(qū)動(dòng)不僅要實(shí)現(xiàn)對(duì)硬件的操作,還要為用戶應(yīng)用程序提供專用的API函數(shù)庫,以方便用戶實(shí)現(xiàn)對(duì)硬件的操作訪問。

Windows XP操作系統(tǒng)下的驅(qū)動(dòng)程序一般是基于WDM(Windows Driver Model)模型開發(fā)的。該模型中的上層應(yīng)用程序通過調(diào)用Win32 API函數(shù)發(fā)出對(duì)設(shè)備的訪問請(qǐng)求,I/O管理器則根據(jù)這個(gè)請(qǐng)求構(gòu)造合適的IRP(I/O Request Packet,I/O請(qǐng)求包),并將其傳給設(shè)備驅(qū)動(dòng)程序,接著由驅(qū)動(dòng)程序直接訪問硬件完成IRP處理,最后由I/O管理器把數(shù)據(jù)和結(jié)構(gòu)返回給應(yīng)用程序。

WDM驅(qū)動(dòng)比較常用的有以下三種方法:

第一種是直接使用Windows DDK(Device

Driver Kit,驅(qū)動(dòng)程序開發(fā)包)開發(fā)的驅(qū)動(dòng)程序面向Windows內(nèi)核,該方法工作穩(wěn)定,效率更高。但必須精通Windows內(nèi)部體系結(jié)構(gòu)及設(shè)備驅(qū)動(dòng)程序的體系結(jié)構(gòu)等,因此開發(fā)難度較大。

第二種是使用DriverStudio。此工具軟件已經(jīng)做了很多基礎(chǔ)性工作,也進(jìn)行了一些封裝。

第三種是使用WinDriver,使用該方法時(shí),開發(fā)者只需要在用戶模式下編寫程序來調(diào)用它提供的通用驅(qū)動(dòng)即可。其中Drvier Wizard可以進(jìn)行硬件診斷和自動(dòng)代碼生成。另外還可以將對(duì)速度要求較高的模塊插入內(nèi)核運(yùn)行來獲取更好的性能。本系統(tǒng)即采用WinDriver開發(fā)方法。

3.2 WinDriver中的重要函數(shù)

利用WinDriver開發(fā)驅(qū)動(dòng)程序通常有兩種方法:第一種是利用Driver Wizard生成的代碼進(jìn)行修改;第二種是直接利用WinDriver提供的API函數(shù)來編寫自己的程序。本系統(tǒng)即采用這種方法,開發(fā)時(shí)首先要注意包含所有相關(guān)的頭文件。其基本驅(qū)動(dòng)程序的結(jié)構(gòu)及API函數(shù)如下:

3.3 中斷實(shí)現(xiàn)

PCI總線的通信方式有查詢和中斷兩種方式。查詢方式實(shí)現(xiàn)簡(jiǎn)單,但是難以適應(yīng)實(shí)時(shí)性要求較高的場(chǎng)合,而且上位機(jī)軟件資源占用率過大;中斷方式則可克服以上缺點(diǎn),可以實(shí)現(xiàn)數(shù)據(jù)的實(shí)時(shí)傳輸。本系統(tǒng)將數(shù)據(jù)經(jīng)過處理后存入RAM,存滿一幀數(shù)據(jù),硬件便發(fā)出中斷請(qǐng)求信號(hào),上位機(jī)響應(yīng)中斷請(qǐng)求后,即可讀取一幀數(shù)據(jù)。

要實(shí)現(xiàn)中斷機(jī)制,就要建立一個(gè)獨(dú)立的中斷響應(yīng)線程,并在主函數(shù)中完成中斷的使能、屏蔽及中斷線程的啟動(dòng)。另外,使用WinDriver處理電平中斷時(shí),還必須建立傳輸命令(INTCSR)來應(yīng)答中斷。

其中斷處理過程分為四步:

第一步,調(diào)用WDC_IntEnable(),此函數(shù)的功能是分配并初始化WC_INTERRUPT結(jié)構(gòu)體,自動(dòng)創(chuàng)建中斷處理線程,同時(shí)在其中包含WD_Int-Wait()函數(shù),作用是使線程休眠直至有中斷發(fā)生。另外,還可以調(diào)用底層API函數(shù)InterruptEnable()或WD_Enable(),但此時(shí)需要由用戶自己創(chuàng)建中斷線程;

第二步是中斷線程無限循環(huán)以等待中斷發(fā)生。中斷發(fā)生時(shí),WinDriver在內(nèi)核中執(zhí)行傳輸命令,當(dāng)操作返回到用戶模式時(shí),驅(qū)動(dòng)的用戶模式中斷處理例程將被調(diào)用;之后,中斷處理例程返回,但中斷等待循環(huán)繼續(xù);最后在不再使用中斷時(shí),調(diào)用’WDC_IntDisable()、底層API函數(shù)Inter-mptDisable()或WD_IntDisable()來關(guān)閉中斷。

3.4 驅(qū)動(dòng)的分發(fā)及安裝

驅(qū)動(dòng)的分發(fā)是指在目標(biāo)機(jī)上不用安裝WinDriver開發(fā)包即可應(yīng)用其開發(fā)的設(shè)備驅(qū)動(dòng)。需要準(zhǔn)備的分發(fā)包應(yīng)包括windrvr6.sys、windrvr-6.inf、wd921.cat、waapi921.dll、difxapi.dll、自己的INF(Information File)等文件,而且即使是自己開發(fā)內(nèi)核驅(qū)動(dòng)。也應(yīng)包含在內(nèi)。

Windows操作系統(tǒng)依靠INF文件來得到即插即用設(shè)備的驅(qū)動(dòng)程序信息。WinDriver會(huì)自動(dòng)檢測(cè)PC機(jī)上的即插即用設(shè)備。并為相應(yīng)硬件生成I-NF文件,而且只需稍作修改即可。INF文件可引導(dǎo)系統(tǒng)找到硬件所需要的驅(qū)動(dòng)程序,由WinDriver生成的INF文件中列出了默認(rèn)的拷貝文件win-drvr6.sys。設(shè)備驅(qū)動(dòng)可通過工作于內(nèi)核模式的windrvr6.sys訪問硬件。之后在目標(biāo)機(jī)上裝入驅(qū)動(dòng)分發(fā)包及INF文件,即可通過應(yīng)用程序控制PCI設(shè)備。

4 結(jié)束語

該數(shù)據(jù)傳輸系統(tǒng)的PCI接口邏輯和數(shù)據(jù)傳輸、處理、緩存等用戶邏輯可集成于一片F(xiàn)PGA中。因而可極大的提高資源利用率,并可滿足大量數(shù)據(jù)高速傳輸?shù)囊蟆I衔粰C(jī)應(yīng)用程序采用中斷方式讀取數(shù)據(jù)可大大提高系統(tǒng)的性能。目前,經(jīng)多次試驗(yàn),該系統(tǒng)已完全可以滿足工程需要。