引言

Reed-Solomon碼首先是由Reed和Solomon兩人于1960年提出來的,,簡稱為RS碼,。這是一類具有很強糾錯能力的多進制BCH碼,既能糾正隨機錯誤,,也能糾正突發(fā)錯誤,,也是一類典型的代數(shù)幾何碼。RS碼一直以來都是國際通信領域研究的熱點之一,。

本文以戰(zhàn)術軍用通信系統(tǒng)的首選碼RS(31,,15)碼為例,對生成多項式進行了優(yōu)化,,并采用查表法的原理極大地提高了編碼器運算數(shù)據(jù)的能力,,縮短了運算周期,最終利用VHDL語言編譯,,在FPGA中實現(xiàn),,得到了正確的RS編譯碼。

1 RS編碼原理

能糾正t個錯誤的RS(n,,k)碼具有如下特性:

碼長:n=2m-1符號或m(2m-1)比特,;信息碼元數(shù):k=n-2t符號或mk比特;監(jiān)督碼元數(shù):n-k=2t符號或m(n-k)比特,;最小距離:d=2t+1=n-k-1符號或m(n-k+1)比特,;最小距離為d的本原RS碼的生成多項式一般為:

![]()

令信息元多項式為:

![]()

監(jiān)督多項式為:

![]()

則碼多項式為:

式中:Q(x)是g(x)整除C(x)所得的商式。所有這些原理都與二進制循環(huán)碼一樣,,不同的僅在于運算方法,。對于二進制碼,碼多項式各項系數(shù)只能取0或1,,多項式的加減乘除是模二運算,,是定義在GF(2)域上的多項式。現(xiàn)在碼多項式各項系數(shù)可以取q=2m種不同的值,,應當是定義在GF(2m)域上的多項式,。

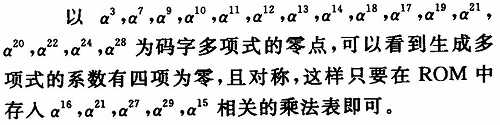

2 生成多項式的優(yōu)化

以RS(31,15)為例,,n=31,,k=15,可糾正錯誤數(shù)為t=(n-k)/2=8,;以![]() 為本原多項式,,可得到GF(25)上的元素如表1所示。

為本原多項式,,可得到GF(25)上的元素如表1所示。

一般的生成多項式為:

則碼字多項式以![]() 為零點,。

為零點,。

由于注意到:

3 RS編碼器的設計

在GF(2m)域上的加法運算實際上就是每位作異或運算,,由異或門組合而成即可。

由于優(yōu)化了生成多項式g(x),,這里只需要在ROM中存入![]() 的乘法表即可,。

的乘法表即可,。

由加法模塊和乘法模塊組成的一級模二運算電路如圖1所示,。

利用ISE9.0仿真軟件得到的運算一級模二運算的仿真圖如圖2所示。

生成的一級模二運算模塊如圖3所示,。

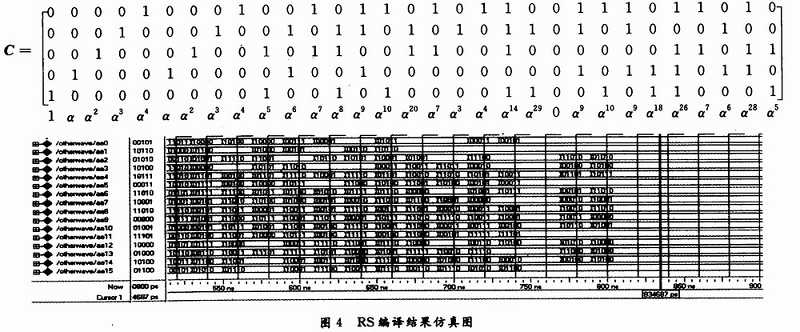

依次連接多個模二運算模塊,,進行一步步模二運算,得到余數(shù)多項式的系數(shù),,即為RS校驗碼,。圖4為當信息碼字為M時的RS編譯結果。

可看到此時:

4 FPGA實現(xiàn)

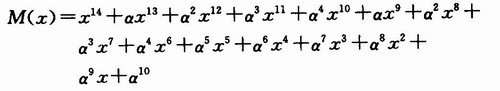

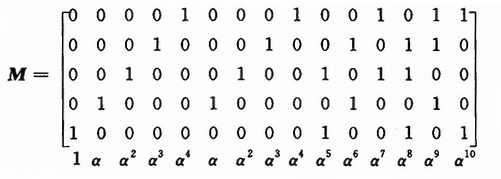

通過RS編碼后的數(shù)據(jù)為5×31的矩陣,,形如,;

將5行數(shù)據(jù)交織編碼,交織度為I=5,,得到(ao bo co do eo a1 b1 c1 d1 e1…a30 b30 c30 d30 e30)的形式,,利用示波器從串口讀出,得到波形圖如圖5所示,。

5 結語

給出的RS編碼器設計方法對生成多項式進行了優(yōu)化,,使得ROM中需要存入的乘法表大幅減少,模擬模二運算的步驟設計編碼過程,,最終燒入FPGA中,,利用示波器采集到了正確的數(shù)據(jù),證明RS編碼器編碼正確,。本文介紹的RS編碼器設計方法簡單,,占用資源少。