模數(shù)轉(zhuǎn)換器(ADC)的種類繁多,我們總是很難弄清哪種ADC才最適合既定應(yīng)用。數(shù)據(jù)手冊往往會使問題變得更加復(fù)雜,許多技術(shù)指標(biāo)指標(biāo)都以無法預(yù)料的方式影響著性能。

選擇轉(zhuǎn)換器時,工程師通常只關(guān)注分辨率、信噪比(SNR)或者諧波。這些雖然很重要,指標(biāo)但其他技術(shù)指標(biāo)同樣舉足輕重。

分辨率,可能是最易被誤解的技術(shù)指標(biāo),它表示輸出位數(shù),但不提供性能數(shù)據(jù)。部分數(shù)據(jù)手冊會列出有效位數(shù)(ENOB),它使用實際SNR測量來計算轉(zhuǎn)換器的有效性。一種更加有用的轉(zhuǎn)換器性能指標(biāo)是噪聲頻譜密度(NSD),單位為dBm/Hz或。NSD可以通過已知的采樣速率、輸入范圍、SNR和輸入阻抗計算得出(dBm/Hz)。已知這些參數(shù),便可選擇一款轉(zhuǎn)換器來匹配前端電路的模擬性能,這種選擇ADC的方法比僅僅列出分辨率更有效。

許多用戶還會考慮雜散和諧波性能,這些都與分辨率無關(guān),但轉(zhuǎn)換器設(shè)計人員一般要調(diào)整他們的設(shè)計,使諧波與分辨率相一致。

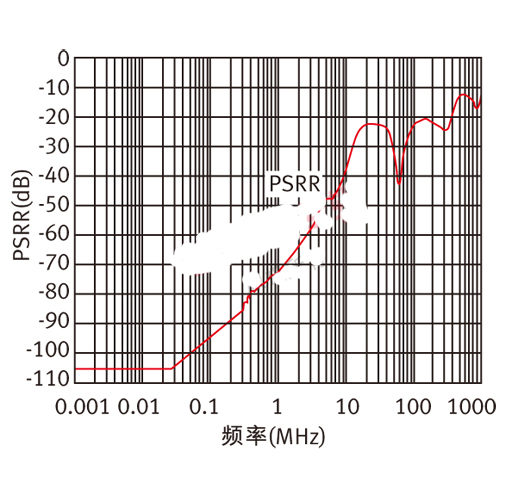

電源抑制(PSR),測量電源紋波如何與ADC輸入耦合,顯現(xiàn)在其數(shù)字輸出上。如果PSR有限,相對于輸入電平,電源線上的噪聲將僅會受到30至50 dB的抑制。

一般而言,電源上的無用信號與轉(zhuǎn)換器的輸入范圍相關(guān)。例如,如果電源上的噪聲是20mV rms ,而轉(zhuǎn)換器輸入范圍是0.7Vrms,則輸入上的噪聲是-31dBFS。如果轉(zhuǎn)換器的PSR為30dB,則相干噪聲會在輸出中顯現(xiàn)為一條-61dBFS譜線。在確定電源將需要多少濾波和去耦時,PSR尤其有用,PSR在醫(yī)療應(yīng)用或工業(yè)應(yīng)用等高噪聲環(huán)境中非常重要。

圖1:電源紋波抑制比(PSRR)vs.頻率。

共模抑制(CMR),測量共模信號存在時所引起的差模信號。許多ADC采用差分輸入來實現(xiàn)對共模信號的高抗擾度,因為差分輸入結(jié)構(gòu)本身能抑制偶數(shù)階失真產(chǎn)物。

與PSR一樣,電源紋波、接地層上產(chǎn)生的高功率信號、混頻器和RF濾波器的RF泄漏以及能夠產(chǎn)生高電場和磁場的應(yīng)用會引入共模信號,雖然許多轉(zhuǎn)換器未規(guī)定CMR,但他們通常具有50至80dB的CMR。

時鐘相關(guān)技術(shù)指標(biāo),盡管比較重要,但并不總是做出規(guī)定,而且可能難以確定。

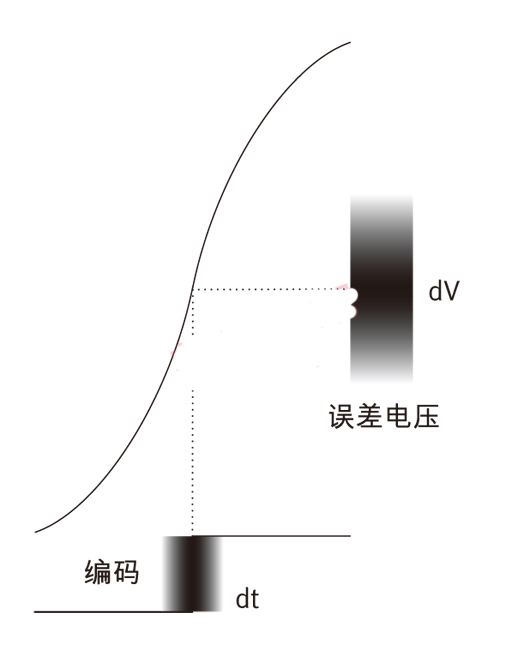

圖2:輸入時鐘與采樣噪聲的關(guān)系。

時鐘壓擺率,實現(xiàn)額定性能所需的最小壓擺率。多數(shù)轉(zhuǎn)換器在時鐘緩沖器上有足夠的增益,以確保采樣時刻界定明確,但如果壓擺率過低使得采樣時刻很不確定,將產(chǎn)生過量噪聲。如果規(guī)定最小輸入壓擺率,用戶應(yīng)滿足該要求,以確保額定噪聲性能。

孔徑抖動,ADC的內(nèi)部時鐘不確定性。ADC的噪聲性能受內(nèi)部和外部時鐘抖動限制。

在典型的數(shù)據(jù)手冊中,孔徑抖動僅限轉(zhuǎn)換器。外部孔徑抖動以均方根方式與內(nèi)部孔徑抖動相加。對于低頻應(yīng)用,抖動可能并不重要,但隨著模擬頻率的增加,由抖動引起的噪聲問題變得越來越明顯。如果不使用充足的時鐘,性能將比預(yù)期要差。

除由于時鐘抖動而增加的噪聲以外,時鐘信號中與時鐘不存在諧波關(guān)系的譜線也將顯現(xiàn)為數(shù)字化輸出的失真。因此,時鐘信號應(yīng)具有盡可能高的頻譜純度。

孔徑延遲,采樣信號的應(yīng)用與實際進行輸入信號采樣的時刻之間的時間延遲。此時間通常為納秒或更小,可能為正、為負或甚至為零。除非知道精確的采樣時刻非常重要,否則孔徑延遲并不重要。

轉(zhuǎn)換時間和轉(zhuǎn)換延遲,這是兩個密切相關(guān)的技術(shù)指標(biāo)。轉(zhuǎn)換時間一般適用于逐次逼近型轉(zhuǎn)換器(SAR),這類轉(zhuǎn)換器使用高時鐘速率處理輸入信號,輸入信號出現(xiàn)在輸出上的時間明顯晚于轉(zhuǎn)換命令,但早于下一個轉(zhuǎn)換命令。轉(zhuǎn)換命令與轉(zhuǎn)換完成之間的時間稱為轉(zhuǎn)換時間。

轉(zhuǎn)換延遲通常適用于流水線式轉(zhuǎn)換器。作為測量用于產(chǎn)生數(shù)字輸出的流水線(內(nèi)部數(shù)字級)數(shù)目的技術(shù)指標(biāo),轉(zhuǎn)換延遲通常用流水線延遲來規(guī)定。通過將此數(shù)目乘以應(yīng)用中使用的采樣周期,可計算實際轉(zhuǎn)換時間。

喚醒時間,為了降低功耗敏感型應(yīng)用的功耗,器件通常在相對不用期間關(guān)斷,這樣做確實可以節(jié)省大量功耗,但器件重新啟動時,內(nèi)部基準(zhǔn)電壓源的穩(wěn)定以及內(nèi)部時鐘的功能恢復(fù)都需要一定的時間,此時轉(zhuǎn)換的數(shù)據(jù)將不滿足技術(shù)指標(biāo)。

輸出負載,同所有數(shù)字輸出器件一樣,ADC(尤其是CMOS輸出器件)規(guī)定輸出驅(qū)動能力。出于可靠性的原因,知道輸出驅(qū)動能力比較重要,但最佳性能一般是在未達到完全驅(qū)動能力時。

在高性能應(yīng)用中,重要的是,將輸出負載降至最低,并提供適當(dāng)?shù)娜ヱ詈蛢?yōu)化布局,以盡可能降低電源上的壓降。為了避免此類問題發(fā)生,許多轉(zhuǎn)換器都提供LVDS輸出。LVDS具有對稱性,因此可以降低開關(guān)電流并提高總體性能。如果可以,應(yīng)該使用LVDS輸出以確保最佳性能。

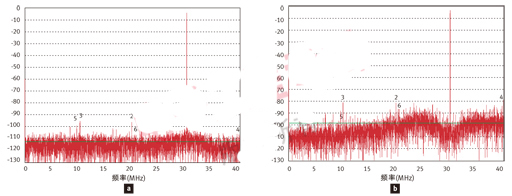

未規(guī)定標(biāo)準(zhǔn),一個至關(guān)重要的未規(guī)定項目是PCB布局。雖然可規(guī)定內(nèi)容的不多,但它會顯著影響轉(zhuǎn)換器的性能。例如,如果應(yīng)用未能采用充足的去耦電容,就會存在過多的電源噪聲。由于PSR有限,電源上的噪聲會耦合到模擬輸入中,并破壞數(shù)字輸出頻譜,如圖4所示。

圖4a. 電容與性能 圖4b. 有限電容與性能