0引言

測頻和測脈寬現(xiàn)在有多種方法。通常基于MCU的信號參數(shù)測量,由于其MCU工作頻率很低,所以能夠達(dá)到的精度也比較低,而基于AD10200和 FPGA的時域測量精度往往可達(dá)10 ns,頻率測量精度在100 kHz以內(nèi)。適應(yīng)信號的脈寬范圍在100 ns~1 ms之間;重復(fù)周期在0.05~100ms:頻率在0.1 Hz~50 MHz。

AD10200是高速采樣芯片,其中內(nèi)嵌變壓器,因此采樣電路外部不再需要變壓器,使得電路設(shè)計更為簡單;最低采樣速率為105 MSPS,具有3.3 V或者5 V CMOS兼容輸出電平,雙通道12位采樣,補碼形式輸出,每個通道功耗為0.850W。通常可應(yīng)用于雷達(dá)中頻信號接收機、相位組接收機、通信接收機、 GPS抗干擾接收機等。

StratixⅡ是Altera公司的中高端主流產(chǎn)品,該產(chǎn)品采用1.2 V、90 nm、9層信號走線,全銅SRAM工藝制造。StratixⅡ內(nèi)嵌RAM塊、DSP塊、鎖相環(huán)(PLL)和外部存儲器接口,同時,StratixⅡ也增加了全新的邏輯結(jié)構(gòu)一自適應(yīng)邏輯模塊(ALM),因而增加了動態(tài)相位對準(zhǔn)(DPA)電路和對新的外部存儲器接口的支持。AD芯片可以穩(wěn)定工作在100 MHz,F(xiàn)PGA速度可高達(dá)幾百MHz,故可保證系統(tǒng)的測量精度。

1測量原理

1.1時域測量原理

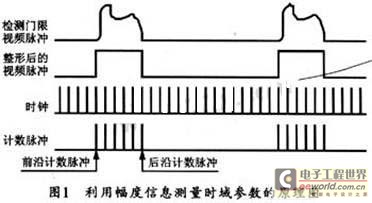

時域測量包括脈寬(PW)測量和脈沖重復(fù)周期(Pri)測量,時域測量在FPGA中可利用數(shù)字化技術(shù)實現(xiàn)。AD的兩路輸入為兩路正交中頻信號。經(jīng)過Cordic算法,即幅相解算之后獲得幅度和相位信息,其中利用幅度信息測得時域參數(shù),其原理圖如圖1所示。

當(dāng)脈沖信號進(jìn)入FPGA后,將首先進(jìn)行門限判定,以將不規(guī)則的脈沖信號進(jìn)行整形并變?yōu)橐?guī)則的脈沖信號。整形后,在脈沖信號上升沿啟動脈寬計數(shù)器和重復(fù)周期計數(shù)器,而在該脈沖信號的下降沿鎖存脈寬計數(shù)器并且在下個脈沖信號上升沿鎖存重復(fù)周期計數(shù)器;由此即可得到脈寬和重復(fù)周期的量化值N和M,然后再通過工作時鐘的計算,就可得出脈寬和重復(fù)周期。

1.2頻域參數(shù)測量

頻域參數(shù)測量可由兩路正交信號所攜帶的相位信息得到。對于輸入正交采樣I、Q兩路序列,則可通過求反正切得到角度序列 θ(n)=arctg(I(n/Q(n),但此時得到的角度序列是周期性分布在(0,2π)之間的,因此需對此角度進(jìn)行解模糊,可將角度序列解為遞增直線,然后按照如下公式進(jìn)行解模糊,并得到新的角度序列φ(n):

通過以上公式可以準(zhǔn)確計算出脈內(nèi)信號頻率,從而達(dá)到測頻的目的。

2系統(tǒng)硬件電路設(shè)計

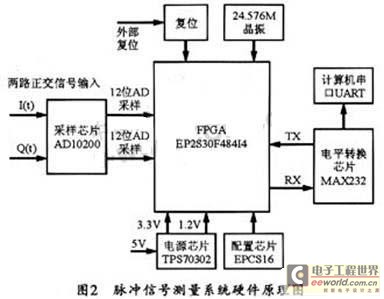

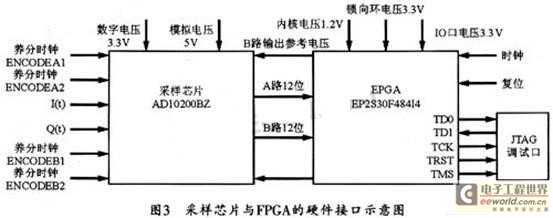

基于AD10200和FPGA芯片EP2S30F48414的脈沖信號測量系統(tǒng)的硬件電路原理如圖2所示。此系統(tǒng)的輸入信號要求為兩路正交信號,正交信號在基帶數(shù)字信號處理中經(jīng)常要用到,它可以通過多種方法來實現(xiàn),如模擬器件下變頻或者是數(shù)字正交下變頻等技術(shù)。IQ兩路正交信號的特點為幅度相仿,相位相差90度。AD采樣芯片負(fù)責(zé)將模擬信號轉(zhuǎn)換為數(shù)字信號;電源芯片用于為AD、FPGA和MAX232供電;晶振用于提供工作時鐘,選擇24.576 MHz晶振的原因是因為FPGA與計算機串口通信時還要實現(xiàn)一個模擬串口,而選用24.576 MHz可以剛好模擬出9600 bit/s的波特率,從而可減少誤碼率:外部復(fù)位可為FPGA提供外部復(fù)位信號。MAX232是一個常用的電平轉(zhuǎn)換芯片,可以將FPGA輸出的LVTTL 3.3 V電平轉(zhuǎn)換為串口電平,以便被計算機UART口所識別和接收。由以上芯片組成的系統(tǒng)工作頻率為100 MHz,可實現(xiàn)快速、高精度地脈寬和頻率測量。其中采樣芯片和FPGA的硬件連接圖如圖3所示。

3FPGA軟件設(shè)計

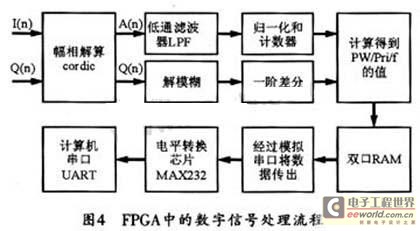

本系統(tǒng)中的時域參數(shù)測量和頻域參數(shù)測量工作由FPGA擔(dān)任,其輸入為正交信號兩路序列,輸出分別為脈寬(PW)、重復(fù)周期(Pri)和頻率(f)。FPGA中的數(shù)字信號處理流程如圖4所示。

圖中,I(n)和Q(n)為兩路正交信號序列;A (n)為幅度信息序列;為相位信息序列。

兩路正交信號I(n)和Q(n) 序列經(jīng)過幅相解算后,即可得到幅度序列和相位序列。對于幅度序列,經(jīng)過低通濾波和歸一化,可得到規(guī)則脈沖,再按時域參數(shù)測量原理得到PW和Pri;對于相位序列,按照頻率測量原理可得到頻率f;然后將PW、Pri及f值存人雙口RAM,再將所存數(shù)據(jù)通過模擬串口從FPGA的通用I/O口傳出,經(jīng)MAX232電平轉(zhuǎn)換后輸入到計算機串口中,最后通過上位機顯示出來,以實現(xiàn)人機通信。

4結(jié)束語

本系統(tǒng)的輸入信號要求為正交信號,通常可用于通信和雷達(dá)信號的后端數(shù)字信號處理。本系統(tǒng)采用相位差分算法來計算頻率,運算簡單,F(xiàn)PGA速度可以優(yōu)化到200 M本系統(tǒng)利用了采樣芯片和FPGA的高速性,從而實現(xiàn)了很高的測量精度和實時檢測的目的;由于采用模擬串口進(jìn)行傳輸,故其抗干擾性能較好。