DRM系統(tǒng)采用OFDM調(diào)制方式,引入了先進(jìn)的信源信道編碼和調(diào)制技術(shù),使得AM波段的音頻廣播質(zhì)量大大提高,在保持現(xiàn)有10kHz帶寬時(shí)接近了FM廣播的質(zhì)量。

本文首先簡單介紹DRM系統(tǒng),然后重點(diǎn)討論DRM測試接收機(jī)的設(shè)計(jì)背景、信號(hào)處理流程及硬件平臺(tái)的結(jié)構(gòu)。

1 DRM系統(tǒng)介紹

1.1 系統(tǒng)概述

DRM系統(tǒng)采用OFDM調(diào)制方式,具有多種傳輸模式,適用于多種信道和帶寬的傳輸方式,可以傳送音頻流及數(shù)據(jù)流。DRM標(biāo)準(zhǔn)同時(shí)提供了數(shù)模同播的廣播方案,可以將模擬與數(shù)字信號(hào)同時(shí)以同一載波頻率播出,有利于模擬廣播向數(shù)字廣播的平滑過渡。

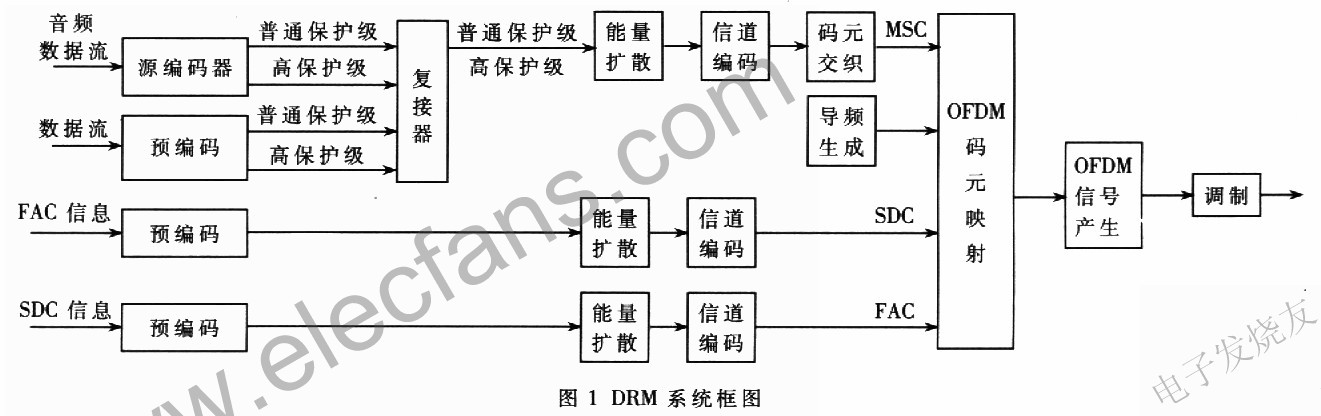

DRM系統(tǒng)框圖如圖l所示,主要由三個(gè)邏輯通道組成:主業(yè)務(wù)通道(MSC)、業(yè)務(wù)描述通道(SDC)和快速訪問通道(FAC)。

FAC通道提供信號(hào)帶寬、調(diào)制方式和交織長度等信息;SDC通道提供如何解調(diào)MSC、如何找到相同數(shù)據(jù)的其他數(shù)據(jù)源,以及在復(fù)接器中為業(yè)務(wù)提供屬性等信息;MSC通道包含音頻或數(shù)據(jù)業(yè)務(wù),通過復(fù)接器對(duì)不同保護(hù)級(jí)別的數(shù)據(jù)和音頻業(yè)務(wù)進(jìn)行復(fù)接,MSC最多可以包括四路業(yè)務(wù),任何一路都可以是音頻或數(shù)據(jù)。

1.2 信源信道編碼

DRM的信源編碼采用先進(jìn)的AACPlus等編碼技術(shù),有效地提高了信源的壓縮比。

信道編碼采用基于卷積編碼的多級(jí)編碼(MLC,Multi-Level Coding),可以分為標(biāo)準(zhǔn)映射(SM)、對(duì)稱分級(jí)映射(HMsym)和混合分級(jí)映射(HMmix)三種QAM映射類型。通過交織克服時(shí)間和頻率選擇性衰落,根據(jù)信道特性可以選擇2s的長交織或者0.4s的短交織。

1.3 導(dǎo)頻

DRM在所傳輸?shù)腛FDM碼元中插入了三種導(dǎo)頻信息,可用于接收機(jī)同步、均衡處理。其中頻率導(dǎo)頻主要用于接收機(jī)頻偏的估計(jì);時(shí)間導(dǎo)頻用于接收機(jī)幀同步的計(jì)算;增益導(dǎo)頻用于接收機(jī)信道估計(jì)。

2 DRM測試接收機(jī)設(shè)計(jì)背景

我國已經(jīng)在部分地區(qū)進(jìn)行了DRM系統(tǒng)的現(xiàn)場測試,測試效果令人滿意,這給DRM系統(tǒng)的應(yīng)用奠定了基礎(chǔ)。

目前,國內(nèi)外采用的DRM接收機(jī)大多是基于PC的DRM軟件接收機(jī),已經(jīng)比較成熟,但其應(yīng)用范圍終究受到一定限制。適于廣泛應(yīng)用的便攜式硬件DRM接收機(jī)目前還處于研制階段,尚未批量生產(chǎn)。而DRM系統(tǒng)只有在專用ASIC推出后才可以迅速降低接收機(jī)的成本,才能有利于DRM系統(tǒng)的推廣。

基于上述考慮,筆者設(shè)計(jì)了DRM硬件測試接收機(jī)。一方面是對(duì)硬件實(shí)現(xiàn)DRM接收機(jī)的一種探討,另一方面可以以此為原型機(jī),進(jìn)一步為設(shè)計(jì)擁有自主知識(shí)產(chǎn)權(quán)的DRM接收機(jī)ASIC積累經(jīng)驗(yàn)。為此,筆者將設(shè)計(jì)目標(biāo)確定為:可以驗(yàn)證DRM接收系統(tǒng)的各種算法,可以對(duì)相同模塊的不同算法進(jìn)行比較,可以對(duì)算法的硬件可行性、穩(wěn)定性及復(fù)雜度進(jìn)行評(píng)估。考慮到全數(shù)字接收機(jī)代替現(xiàn)有模擬接收機(jī)需要一個(gè)長期的過程,設(shè)計(jì)中同時(shí)考慮了數(shù)模同播的兼容性問題。

3 DRM測試接收機(jī)信號(hào)處理流程

根據(jù)數(shù)模同插的要求,在設(shè)計(jì)DRM接收機(jī)RF前端時(shí)采用了改造現(xiàn)有模擬收音機(jī)的方法。整合后的接收機(jī)既可以收聽模擬信號(hào),又可以完成數(shù)字信號(hào)的處理,這樣就可以適應(yīng)數(shù)模同播的需要。下文主要討論數(shù)字接收機(jī)的信號(hào)處理過程。

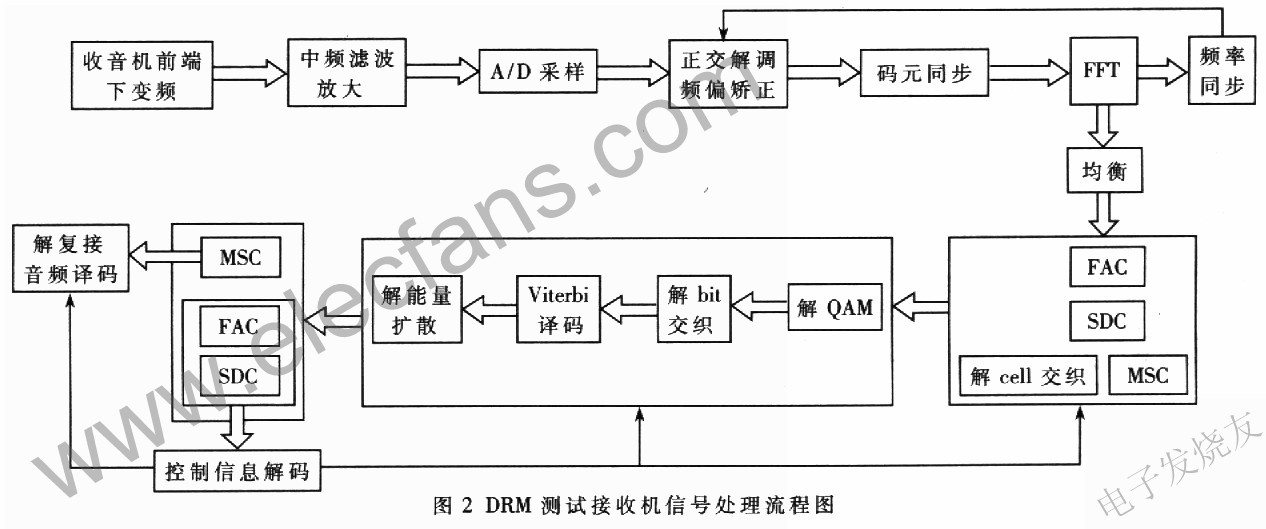

測試接收機(jī)系統(tǒng)框圖如圖2所示。接收信號(hào)通過模擬收音機(jī)前端下變頻到中頻,將中頻信號(hào)引出,經(jīng)過濾波送入AD采樣,從而獲得中頻采樣數(shù)據(jù)。

中頻采樣數(shù)據(jù)通過正交解調(diào)得到基帶數(shù)據(jù)。首先通過碼元同步找到OFDM碼元的起始位置,然后通過FFT完成OFDM信號(hào)的解調(diào),將時(shí)域數(shù)據(jù)變換到頻域,并利用頻率導(dǎo)頻信息計(jì)算并校正頻率偏差,因?yàn)镺FDM系統(tǒng)對(duì)載波頻偏非常敏感,經(jīng)過頻率校正后,頻率誤差應(yīng)小于0.01倍子載波間隔。在此基礎(chǔ)上,利用時(shí)間導(dǎo)頻信息找到DRM系統(tǒng)的傳輸幀起始碼元,此后接收機(jī)從傳輸幀起始位置開始進(jìn)行后續(xù)處理。

由于短波信道變化復(fù)雜,時(shí)域及頻域的選擇性衰落都很強(qiáng),造成丁接收信號(hào)的幅度和相位受到嚴(yán)重干擾,在解高階QAM映射時(shí)會(huì)引入較大的誤差,框圖中的均衡模塊用來解決上述問題。DRM系統(tǒng)設(shè)計(jì)了增益導(dǎo)頻,分布在時(shí)間一頻率域上,利用增益導(dǎo)頻的信息進(jìn)行信道均衡。

按圖2所示流程,從均衡后的數(shù)據(jù)中提取FAC單元并將其解碼,得到解調(diào)SDC的信息;再提取SDC單元,根據(jù)FAC的信息解碼SDC,得到SDC數(shù)據(jù)實(shí)體;最后提取MSC,根據(jù)FACSDC的信息解碼MSC。上述單元分別經(jīng)過解交織、解OAM映射、Viterbi譯碼、能量解擾等模塊的處理后,最后將MSC解復(fù)接后的數(shù)據(jù)進(jìn)行音頻譯碼或者數(shù)據(jù)解碼。

4 DRM測試接收機(jī)硬件結(jié)構(gòu)

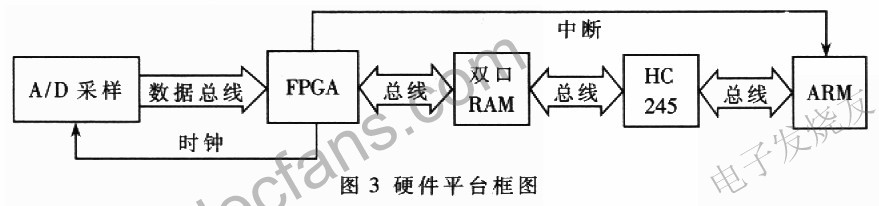

測試接收機(jī)基帶信號(hào)處理部分主要采用ARM與FPGA聯(lián)合處理的硬件平臺(tái)實(shí)現(xiàn)。ARM處理器可以在不改變硬件結(jié)構(gòu)的情況下,通過下載不同的軟件程序?qū)崿F(xiàn)不同的功能,這樣非常有利于不同算法的驗(yàn)證,而且ARM公司可以提供處理器內(nèi)核,為進(jìn)一步設(shè)計(jì)接收機(jī)ASIC奠定基礎(chǔ)。由于ARM以half-word(16 bits)為最小處理單位,所以用ARM處理器處理比特流信號(hào)會(huì)造成處理器資源的浪費(fèi),為此針對(duì)比特流信號(hào)的處理采用專用邏輯電路實(shí)現(xiàn),在測試接收機(jī)中用FPGA實(shí)現(xiàn)。這樣,兩種處理器的特性可以形成互補(bǔ),使硬件平臺(tái)設(shè)計(jì)比較合理。

4.1 模塊劃分

DRM系統(tǒng)設(shè)計(jì)了多種模式,不同模式的碼率是不同的,在正交解調(diào)后需要變碼率輸出;Viterbi譯碼器也是以比特流為處理單位;考慮到這兩個(gè)模塊的算法特點(diǎn)及數(shù)據(jù)輸出形式,將這兩個(gè)模塊放在FPGA中實(shí)現(xiàn)。

圖2中所示的其他處理模塊,特別是同步和均衡模塊是接收機(jī)的關(guān)鍵模塊,其性能好壞直接影響接收效果,并且根據(jù)今后現(xiàn)場測試的情況,其算法存在調(diào)整的可能性.因此這些模塊通過ARM實(shí)現(xiàn)。需要對(duì)算法進(jìn)行調(diào)整時(shí),只需修改軟件程序,重新載入ARM即可,硬件部分無需改動(dòng)。以實(shí)現(xiàn)測試接收機(jī)便于對(duì)各種算法的性能進(jìn)行驗(yàn)證和比較的目的。

4.2 硬件平臺(tái)結(jié)構(gòu)

測試接收機(jī)硬件平臺(tái)如圖3所示。FPGA采用XILINX公司的VirtexⅡXC2V500型芯片;ARM采用三星公司的S3C4510B型ARM7 TDMI芯片;ADC模塊采用了AD公司14-bit的AD9243。FPGA與ARM之間通過雙口RAM進(jìn)行數(shù)據(jù)交互,使用HC245芯片作為地址和數(shù)據(jù)總線的驅(qū)動(dòng)。

A/D采樣后的中頻數(shù)據(jù)送入FPGA做正交解調(diào);FPGA將解調(diào)后的數(shù)據(jù)寫入雙口RAM同時(shí)給ARM產(chǎn)生中斷信號(hào);ARM響應(yīng)外部中斷,將數(shù)據(jù)讀入、進(jìn)行后續(xù)處理。

如圖2中的流程,ARM在處理完解交織后,將處理后的數(shù)據(jù)寫入雙口RAM,同時(shí)向特定的地址寫控制字,F(xiàn)PGA檢測到控制字后,將數(shù)據(jù)讀入.進(jìn)行Viterbi譯碼。FPGA將Viterbi譯碼結(jié)果寫入雙口RAM,向ARM發(fā)出中斷信號(hào),ARM響應(yīng)中斷,將數(shù)據(jù)讀入,再進(jìn)行后續(xù)處理。

4.3 主控制程序流程圈

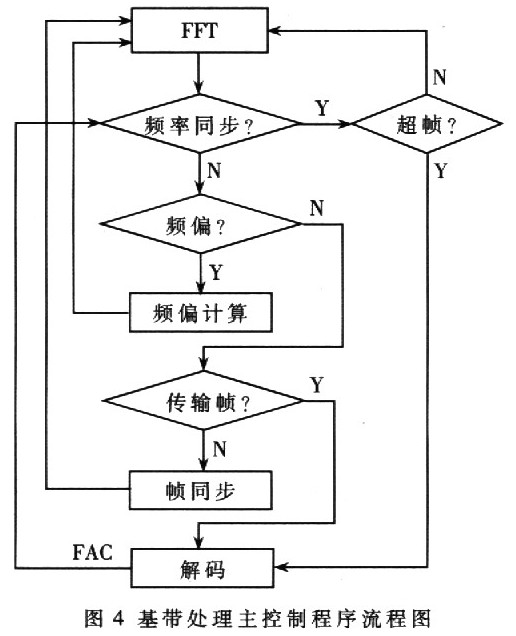

根據(jù)圖2所示的DRM信號(hào)處理時(shí)序,圖4為ARM基帶處理主控制程序流程圖,依次進(jìn)行碼元同步、整數(shù)倍頻偏估計(jì)、幀同步及后續(xù)信道解碼處理。上述過程實(shí)現(xiàn)了DRM接收機(jī)基帶信道解碼過程。

4.4 測試結(jié)果

測試信號(hào)采用模式C、10kHz帶寬的DRM信號(hào),信道采用標(biāo)準(zhǔn)中提供的2號(hào)信道模型,SNR=23dB,頻偏為2倍子載波間隔。

測試結(jié)果示于圖5中,其中圖5(a)為未經(jīng)過同步和均衡處理的數(shù)據(jù)星座圖;圖5(b)"(d)為接收信號(hào)通過硬件正交解調(diào)、同步、均衡、信道解碼等模塊后輸出數(shù)據(jù)的星座圖。從圖5中可以看出,經(jīng)過同步、均衡處理后,星座圖明顯改善,處理器有效地解出了三個(gè)通道的數(shù)據(jù)。

數(shù)字廣播產(chǎn)業(yè)有廣泛的市場前景,而擁有自主知識(shí)產(chǎn)權(quán)的接收機(jī)對(duì)民族工業(yè)具有特殊意義。本文討論的DRM測試接收機(jī)信號(hào)處理流程及硬件平臺(tái)的結(jié)構(gòu)是對(duì)硬件實(shí)現(xiàn)DRM接收機(jī)的一次有益嘗試。上述結(jié)構(gòu)、算法已經(jīng)在ARM7和FPGA的硬件平臺(tái)上聯(lián)調(diào)通過,驗(yàn)證了本文提出的信號(hào)處理流程及硬件平臺(tái)的可實(shí)現(xiàn)性,但所驗(yàn)證的主要是基帶信號(hào)處理功能,還沒有包括接收機(jī)的全部.整個(gè)測試接收機(jī)的設(shè)計(jì)工作仍然需要進(jìn)一步完善。