概述

AD7262" title="AD7262">AD7262是一款逐步逼近式(SAR)模數(shù)轉(zhuǎn)換器(A/D轉(zhuǎn)換器)。其內(nèi)部有2個跟蹤保持放大器,2個12位的同步采樣" title="同步采樣">同步采樣A/D轉(zhuǎn)換器,2個可編程的放大器以及2組比較器和2個獨(dú)立的數(shù)據(jù)輸出引腳。適用于汽車控制領(lǐng)域及要求高同步、需簡單運(yùn)算的微弱信號檢測應(yīng)用。因此,這里詳細(xì)介紹同步采樣MD轉(zhuǎn)換器AD7262原理及應(yīng)用。

2 AD7262簡介

2.1 主要特點(diǎn)

AD7262具有高速低功耗同步采樣,最高可達(dá)1 MS/s。其內(nèi)部集成的可編程放大器PGA有14種放大增益可供選擇。兩組比較器A、B和C、D用作電機(jī)控制或各種電極傳感器的運(yùn)算器。其中比較器A和B具有低功耗特點(diǎn),比較器C和D具有高速特點(diǎn)。雙通道差分輸入同時采樣和A/D轉(zhuǎn)換,輸入阻抗大于1 GΩ。單電源+5 V供電。PGA增益為2,-3 dB帶寬為1.7 MHz,信噪比SNR為73 dB;其增益為32時,信噪比為66 dB。輸入直流漏電流±0.001μA,失調(diào)漂移為2.5μV/℃。帶有串行外設(shè)接口SPI,兼容QSPI,MICROWIRE,DSP。該器件具有多種節(jié)能模式,動態(tài)匹配所需內(nèi)部模塊,具有寄存器控制和引腳驅(qū)動兩種工作方式。

2.2 引腳功能

AVcc:模擬電源輸入端,4.75~5.25 V;

CA_CBVCC/CC_CDVCC:比較器的電源輸入端,2.7~5.25 V;

CA_CB_GND/CC_CD_GND:比較器的地輸入端;

VA+/VA-,VB+/VB-:A/D轉(zhuǎn)換器A和B通道的差分模擬輸入端;

VREFA/VREFB:A/D轉(zhuǎn)換器A和B通道的基準(zhǔn)電壓輸入輸出端;

SCLK:串行時鐘,SPI通訊時鐘,也是A/D轉(zhuǎn)換過程的時鐘源;

CAL:初始化內(nèi)部失調(diào)校準(zhǔn)邏輯輸入;

PD2:節(jié)能模式選擇邏輯輸入;

PD1:節(jié)能模式選擇邏輯輸入;

PD0/DIN:節(jié)能模式選擇邏輯輸入,同時在寄存器控制模式下為數(shù)據(jù)輸入端;

CS:片選輸入端;

CA+/CA-,CB+/CB-:比較器A和B的差分輸入端;

CC+/CC-,CD+/CD-:比較器C和D的差分輸入端;

AGND:模擬地輸入端;

DGND:數(shù)字地輸入端;

COUTA~COUTD:比較器CMOS推拉輸出,使用VDRIVE時,為數(shù)字輸出端;

DOUTA/DOUTB:A/D轉(zhuǎn)換串行數(shù)據(jù)輸出端;

G0~G3:增益倍數(shù)邏輯輸入端,當(dāng)全為低電平時,為寄存器控制工作方式;

VDRIVE:邏輯電源輸入端,2.7~5.25 V;

REFSEL:基準(zhǔn)電壓選擇端,高電平使用內(nèi)部基準(zhǔn)電壓,低電平使用外部基準(zhǔn)電壓。

2.3 內(nèi)部結(jié)構(gòu)

圖1為AD7262的內(nèi)部結(jié)構(gòu)圖。兩路差分信號通過各自的PGA同步采樣放大后,進(jìn)入跟蹤保持器,此時由控制邏輯控制2個12位的逐次逼近型A/D轉(zhuǎn)換器實(shí)現(xiàn)模擬數(shù)字轉(zhuǎn)換,最后由輸出驅(qū)動器分別串行驅(qū)動輸出至DOUTA和DOUTB。

在引腳驅(qū)動方式下,G0~G3必須至少有一個高電平。外接的G0~G3決定PGA的放大倍數(shù)。PD2~PD0 3個端口電平控制其內(nèi)部比較器和12位的A/D轉(zhuǎn)換器各模塊的使用或關(guān)閉。在寄存器控制方式下,PD2,PD1,G0~G3全為低電平。PD0/DIN為數(shù)據(jù)輸入端,用于寫入相關(guān)控制寄存器,動態(tài)配置放大倍數(shù)、校準(zhǔn)和節(jié)能模式。AD7262以2的補(bǔ)碼輸出轉(zhuǎn)換結(jié)果。

2.4 自動校準(zhǔn)

自動校準(zhǔn)是AD7262的主要特點(diǎn)之一。利用CAL引腳校準(zhǔn)設(shè)備失調(diào)。設(shè)置CAL為高電平,在下一個CS下降沿完成初始化校準(zhǔn)值。失調(diào)校準(zhǔn)的完成需要一個完整的轉(zhuǎn)換周期,包括CS下降沿后的19個SCLK周期。如果需要,CAL可保持多于一個轉(zhuǎn)換周期的高電平,且此時AD7262繼續(xù)校準(zhǔn)。也可使用控制寄存器初始校準(zhǔn)值,設(shè)置控制寄存器的CAL位為1即可實(shí)現(xiàn)。注意在下一個CS下降沿,校準(zhǔn)會被初始化,AD7262的當(dāng)前轉(zhuǎn)換就失去意義。其A/D轉(zhuǎn)換器必須處于工作狀態(tài)來完成內(nèi)部校準(zhǔn)。

A/D轉(zhuǎn)換器A和B通道具有獨(dú)立的外部增益寄存器用以校準(zhǔn)信號增益。增益校準(zhǔn)寄存器有7位,改變該寄存器以補(bǔ)償增益。MSB是符號位,其他6位為存儲增益倍數(shù),用于調(diào)整模擬輸入信號的范圍,其校準(zhǔn)精度是1/4 096。

3 典型應(yīng)用

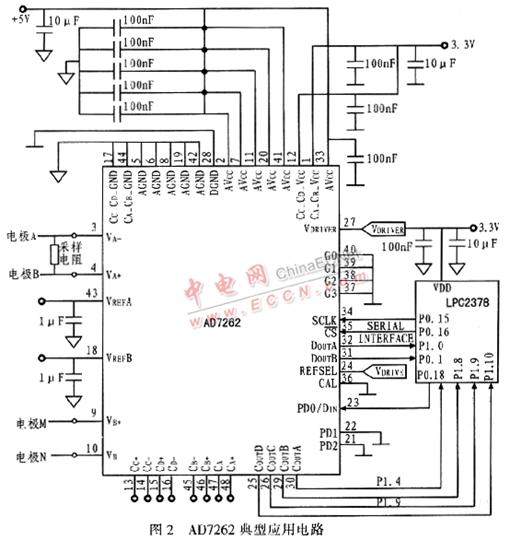

3.1 硬件設(shè)計(jì)

圖2為AD7262與ARM處理器LPC2378的典型應(yīng)用電路,實(shí)現(xiàn)直流電法勘探中電極A、B電流和電極M、N電壓的采集。采用金屬膜電阻作為采樣電阻以提高測量精度。由于A、B電極之間電壓是對大地供電的電極電壓,一般大于100 V,前端電極中都有高壓隔離電路,該采樣電阻阻值一般小于100 Ω。AD7262工作在寄存器控制方式。在LPC2378的P0.15提供的SCLK的控制時序下,通過P0.18向AD7262的控制寄存器寫入相關(guān)數(shù)據(jù)。CS進(jìn)入低電平狀態(tài)后,首先由P0.18寫入相關(guān)寄存器數(shù)據(jù),再開始采樣保持并轉(zhuǎn)換輸出。在寫入寄存器時,DOUTA和DOUTB輸出為三態(tài)。

AD7262主要通信方式為SPI四線式。由于AD7262無法控制何時通信,故只能工作在從模式下。主控制器LPC2378的P0.15提供通訊時鐘信號SCLK。CS為片選輸入。DOUTA或DOUTB為SPI的數(shù)據(jù)輸出端。SPI的數(shù)據(jù)輸入端為PD0/DIN。電路設(shè)計(jì)時,通過LPC2378向AD7262內(nèi)部寫入相關(guān)數(shù)據(jù)來實(shí)現(xiàn)各類動態(tài)配置。圖3和圖4為串行接口讀寫時序圖。串行時鐘SCLK提供轉(zhuǎn)換時鐘及AD7262轉(zhuǎn)換后傳輸信息的控制。對于片內(nèi)2個A/D轉(zhuǎn)換器,AD7262有相應(yīng)的2個輸出引腳。數(shù)據(jù)從AD7262的DOUTA和DOUTB讀取。用戶可選用其中一個輸出數(shù)據(jù)。

在CS下降沿,跟蹤保持器處于保持模式。此時,采樣、轉(zhuǎn)換同時被初始化模擬輸入。這需要至少19個SCLK周期。第19個SCLK的下降沿到來時,AD7262恢復(fù)至跟蹤模式,并設(shè)置DOUTA、DOUTB為使能。數(shù)據(jù)流由12位組成,MSB在前。轉(zhuǎn)換結(jié)果MSB在SCLK第19個周期的下降沿由微控制器在第20個時鐘SCLK的下降沿或上升沿讀取。上升沿還是下降沿取決于所使用的SCLK的頻率。如SCLK最大頻率為40 MHz時,其讀取數(shù)據(jù)時間是23 ns,則導(dǎo)致2 ns的建立時間。而這2 ns的建立時間無法與微控制器匹配。在這種情況下,就需要在時鐘SCLK的上升沿開始讀數(shù)據(jù)。這樣,轉(zhuǎn)換結(jié)果的MSB位在第19個SCLK下降沿,延遲15 ns,并在第20個周期SCLK的上升沿才被讀出。依此類推,至第30個SCLK下降沿A/D轉(zhuǎn)換器輸出LSB,在第31個SCLK上升沿讀出。反之,如果SCLK為32 MHz時,則下降沿讀數(shù)據(jù)。在設(shè)計(jì)中SPI的通信時鐘頻率(LPC2378的P0.15)小于32 MHz,所以在時鐘的下降沿由LPC2378讀寫數(shù)據(jù)。為提高系統(tǒng)的精度和穩(wěn)定性,可加入一定阻值的耦合電容。

3.2 軟件設(shè)計(jì)

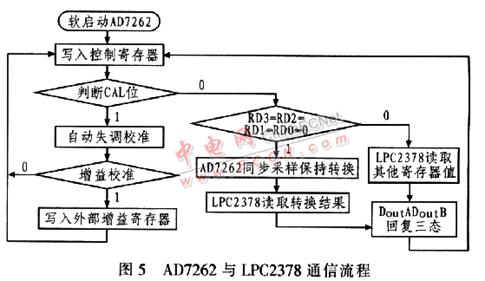

AD7262內(nèi)含6個寄存器,分別是A/D轉(zhuǎn)換器的結(jié)果寄存器、控制寄存器、A/D轉(zhuǎn)換器A和B的內(nèi)部失調(diào)寄存器、A/D轉(zhuǎn)換器A和B通道的外部增益寄存器。控制寄存器共有12位,其中,RD3~RD0是寄存器選擇位。

由于LPC2378和AD7262都兼容SPI接口,兩者的編程只需按照時序圖進(jìn)行即可。此外LPC2378還有許多其他類型接口,所以便于實(shí)現(xiàn)網(wǎng)絡(luò)化,詳細(xì)流程參見圖5。

軟件設(shè)計(jì)中需要注意:CAL引腳在CS為低電平前必須至少保持2μs高電平以確保第一個轉(zhuǎn)換周期中校準(zhǔn)的準(zhǔn)確性。如果在這段時間內(nèi),CAL出現(xiàn)低電平,將導(dǎo)致校準(zhǔn)結(jié)果不準(zhǔn)確。但如果繼續(xù)為高電平,下一個校準(zhǔn)轉(zhuǎn)換則是準(zhǔn)確的。另外在A/D轉(zhuǎn)換過程中,CAL若出現(xiàn)高電平,轉(zhuǎn)換結(jié)果也將不正確。AD7262的校準(zhǔn)是在測量過程中,A/D轉(zhuǎn)換前進(jìn)行的。在測量過程中先校準(zhǔn)再采樣保持。與編程寫寄存器,在時序上要分開。此外使用SPI接口,只有硬件復(fù)位是不夠的,還要使用軟件復(fù)位以保證讀寫數(shù)據(jù)的正確性。實(shí)際應(yīng)用中,要將數(shù)字和模擬部分地線隔離。整個軟件部分采用串口讀寫寄存器完成。

4 結(jié)束語

與其他A/D轉(zhuǎn)換器相比,AD7262除了轉(zhuǎn)換速度快、接口簡單、低功耗、控制功能較強(qiáng)的特點(diǎn)外,還具有內(nèi)嵌PGA、自動校準(zhǔn)、同步采樣等特點(diǎn),適合于不同信號強(qiáng)度級別的多種電極傳感器的信號檢測、控制和電機(jī)控制系統(tǒng)。目前,該系統(tǒng)已成功應(yīng)用于物理勘探電法實(shí)驗(yàn)儀器中,實(shí)現(xiàn)A-B和M-N的電極同步電壓測量,效果較好。