0 引言

隨著大規(guī)模集成電路的發(fā)展,單芯片方案由于成本低、體積小、功耗低等優(yōu)點(diǎn),被越來(lái)越多的電子系統(tǒng)所采用。

微弱脈沖信號(hào)檢測(cè)和識(shí)別在通信、醫(yī)療中都有廣泛應(yīng)用,將微弱脈沖信號(hào)檢測(cè)系統(tǒng)單芯片化具有現(xiàn)實(shí)的研究意義。

1 微弱脈沖檢測(cè)系統(tǒng)框架設(shè)計(jì)

本系統(tǒng)的設(shè)計(jì)目標(biāo)是用低成本CMOS工藝實(shí)現(xiàn)1ns、10mV脈沖信號(hào)的檢測(cè),并輸出FPGA可處理的數(shù)字信號(hào),用于超寬帶無(wú)線(xiàn)通信OOK接收通道,見(jiàn)圖l。

對(duì)于納秒級(jí)信號(hào)的檢測(cè),傳統(tǒng)接收機(jī)方案采用需要高速時(shí)鐘的高速ADC來(lái)實(shí)現(xiàn)模數(shù)轉(zhuǎn)換,高速時(shí)鐘產(chǎn)生電路一般應(yīng)用頻率綜合器方案,消耗較大面積和功耗,且同樣需要外接參考時(shí)鐘。

高速ADC使用時(shí)鐘的重要原因之一是為了利用正反饋來(lái)彌補(bǔ)放大器在高頻情況下的增益不足。隨著集成電路工藝的進(jìn)步,器件寄生電容越來(lái)越小,0.18μm CMOS工藝截止頻率已達(dá)40GHz,通過(guò)使用有源電感,已可以在較低功耗下實(shí)現(xiàn)較高的高頻增益。

本系統(tǒng)要求單片集成,低成本、低功耗,采用多級(jí)放大器級(jí)聯(lián)的方案來(lái)提高檢測(cè)系統(tǒng)的分辨率,并對(duì)輸出信號(hào)通過(guò)延時(shí)電路來(lái)加大脈寬,降低后續(xù)基帶部分?jǐn)?shù)字信號(hào)處理電路的壓力。

本系統(tǒng)具體框架見(jiàn)圖2所示。前一級(jí)是片外的檢波器,通過(guò)50Ω微帶線(xiàn)將信號(hào)輸入,所以本系統(tǒng)需要將輸入阻抗匹配為50Ω。本系統(tǒng)第一級(jí)為共柵型放大器,主要為系統(tǒng)實(shí)現(xiàn)輸入匹配,并提供一定的增益。第二級(jí)為一個(gè)4輸入放大器,可外置閾值電平。第三級(jí)為一個(gè)高頻放大

器,使用了有源電感,可以在較低功耗下達(dá)到較高的帶寬。第四級(jí)為差分轉(zhuǎn)單端放大器,將差分信號(hào)轉(zhuǎn)為單端,并提供一定的增益。第五級(jí)為一對(duì)反相器,提供非線(xiàn)性增益,將信號(hào)整形為數(shù)字信號(hào)。第六級(jí)為可控脈沖展寬電路,將1ns脈沖展寬為5ns。最后一級(jí)為反相器陣列組成的驅(qū)動(dòng),可以驅(qū)動(dòng)5pF電容和50Ω電阻。本系統(tǒng)同時(shí)集成了為核心電路提供電流的帶隙基準(zhǔn)電路。

2 主要電路模塊設(shè)計(jì)

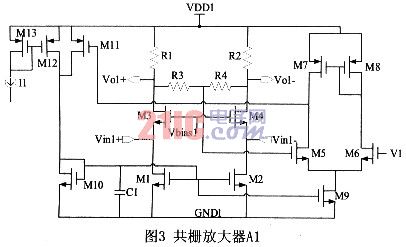

2.1 共柵型放大器A1

本檢測(cè)系統(tǒng)第一級(jí)為了較完整地接收并放大從片外50Ω微帶線(xiàn)傳來(lái)的極窄脈沖信號(hào),使用了輸入阻抗較低的共柵型放大器Al,見(jiàn)圖3。通過(guò)選取合適的寬長(zhǎng)比及偏置電流,M3、M4的跨導(dǎo)為20ms,A1的S11在1G帶寬內(nèi)小于-10。R1、R2作為A1的負(fù)載,選用較為精確的高阻poly電阻,但其在工藝制作中仍會(huì)有較大的絕對(duì)偏差。第一級(jí)中信號(hào)較為微弱,A1中使用了共模反饋電路來(lái)穩(wěn)定輸出端的直流成分,并抑制較低頻段的共模噪聲。

共模反饋電路中,M5的柵端通過(guò)R3、R4檢測(cè)輸出端的共模電平與Vref比較,將差值反饋于M11的柵端,進(jìn)而改變M3等放大器核心器件的電流,構(gòu)成了負(fù)反饋環(huán)路。V1、Il等偏置均為片內(nèi)帶隙基準(zhǔn)電路部分產(chǎn)生。

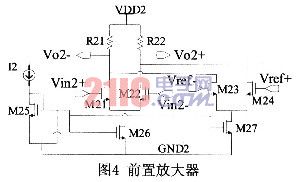

2.2 前置放大器A2

本放大器核心部分為兩對(duì)差分對(duì)管:M21、M22的柵端接差分輸入脈沖信號(hào),M23、M24的柵端分別接直流參考電壓Vref+、Vref-,輸出信號(hào)Vo2見(jiàn)式(1)。當(dāng)脈沖信號(hào)Kin大于Vref時(shí),Vo2為正,經(jīng)過(guò)后級(jí)電路模塊的放大及整形,輸出高電平(>1.79V);反之輸出低電平(<0.1V)。

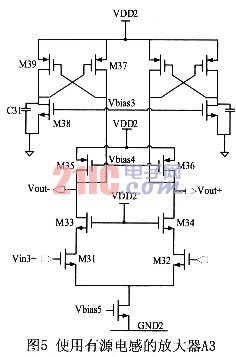

2.3 使用有源電感的放大器A3

A3的電路結(jié)構(gòu)見(jiàn)圖3。M33提高了放大器低頻增益的同時(shí),顯著增大了輸出端Vout-和輸入端共源放大管M3l的漏端之間的阻抗,阻隔了輸出端信號(hào)通過(guò)M3l的柵漏交疊電容Cgd_M31回流輸入端的通路,從而提高了放大器的穩(wěn)定性;同時(shí)降低了M31柵端到其漏端的增益AM31使M31柵端的密勒等效電容Cmil(見(jiàn)式(2))大為降低,從而提高了放大器的帶寬。

![]()

由于SMIC 0.18μm工藝寄生電容的影響,A3作為本系統(tǒng)的主放大器,還需要電感特性器件來(lái)進(jìn)一步提高其帶寬達(dá)到1GHz。

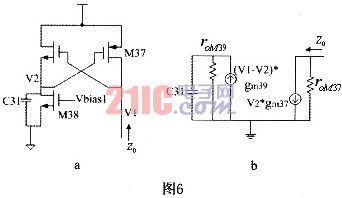

雖然片上電感的噪聲性能優(yōu)于有源電感,但占用太大面積。圖5中M37、M39、C31、M38構(gòu)成了有源電感,見(jiàn)圖6,其阻抗中有一個(gè)零點(diǎn)來(lái)拓展帶寬,見(jiàn)式(3)

2.4 差分轉(zhuǎn)單端放大器A4及脈沖整形A5

差分電路對(duì)共模干擾包括電源和地的波動(dòng)具有較高的抑制能力。本系統(tǒng)前幾級(jí)中信號(hào)較為微弱,需用差分形式傳遞。信號(hào)經(jīng)過(guò)A4放大后,對(duì)比共模干擾已足夠大,故轉(zhuǎn)變?yōu)閱味诵问揭越档凸摹?br />

當(dāng)輸入脈沖信號(hào)接近Vref時(shí),A4輸出端電壓需要進(jìn)一步整形才能變?yōu)閿?shù)字信號(hào)。A5為一對(duì)反相器,可以大大提高脈沖檢測(cè)的靈敏度。

3 結(jié)果分析

圖7為本系統(tǒng)第四級(jí)A4后的AC分析結(jié)果,增益可達(dá)62dB,3dB帶寬可達(dá)816.6MHz,1GHz時(shí)增益為57dB。圖8為本系統(tǒng)各級(jí)瞬態(tài)波形,a為輸入的1.1ns、3mV脈沖信號(hào),b為A4后的波形,幅度為758mV,c為A5整形后得到的1.8V脈沖波形,d為經(jīng)過(guò)A6展寬后4.79ns脈寬的波形。圖9為本系統(tǒng)芯片照片,大小為O.66×0.49mm,功耗為32mW。在圖1所示的系統(tǒng)中,可以傳送40M數(shù)據(jù)率的清晰視頻。

|

4 結(jié)語(yǔ)

本文設(shè)計(jì)的單芯片極窄微弱脈沖檢測(cè)系統(tǒng),工作穩(wěn)定,采用CMOS工藝,低成本、低功耗,且尚有較大改進(jìn)余度。