摘? 要: 提出了一種新穎的非多路復(fù)用" title="多路復(fù)用">多路復(fù)用總線與多路復(fù)用總線的轉(zhuǎn)換接口電路。以兩種總線的典型代表芯片TMS320F206與SJA1000為例,分析了各自時(shí)序的特點(diǎn),詳細(xì)論述了兩種總線之間轉(zhuǎn)換的關(guān)鍵:讀、寫周期" title="寫周期">寫周期的使能信號(hào)和起始基準(zhǔn)的確定,并采用復(fù)雜可編程器件CPLD實(shí)現(xiàn)。

?? 關(guān)鍵詞: 非多路復(fù)用總線? 多路復(fù)用總線? 時(shí)序? CPLD DSP

?

微處理器對(duì)外并行總線接口方式一般分為兩種,一種為多路復(fù)用方式,數(shù)據(jù)與地址采用共用引腳,分時(shí)傳輸;另一種是非多路復(fù)用方式,數(shù)據(jù)與地址采用分離引腳,同時(shí)傳輸。目前國(guó)內(nèi)應(yīng)用廣泛的MCS196和MCS51系列微處理器采用多路復(fù)用總線,設(shè)計(jì)電路時(shí)應(yīng)考慮如何將數(shù)據(jù)和地址從總線上分離出來(lái),與存儲(chǔ)器、外圍接口芯片的數(shù)據(jù)和地址引腳連接。一般利用ALE(地址鎖存)信號(hào)觸發(fā)鎖存器(74LS373)將地址與數(shù)據(jù)信號(hào)分離出來(lái)。近幾年來(lái),隨著低價(jià)位DSP芯片的出現(xiàn),DSP芯片已被廣泛應(yīng)用到控制與測(cè)量領(lǐng)域中。國(guó)內(nèi)使用的DSP芯片以TI公司的TMS320系列為主流。這種微處理器對(duì)外的數(shù)據(jù)和地址總線接口方式為非多路復(fù)用方式,不能與多路復(fù)用方式的外圍接口芯片(如CAN控制器SJA1000)直接相連。國(guó)內(nèi)和國(guó)外也沒(méi)有一款專用集成電路芯片來(lái)實(shí)現(xiàn)非多路復(fù)用方式到多路復(fù)用方式的轉(zhuǎn)換。參考文獻(xiàn)[1]提出了一種轉(zhuǎn)換方法,是將DSP的數(shù)據(jù)線作為CAN控制器的數(shù)據(jù)地址復(fù)用線,用DSP的地址線A0作為地址、數(shù)據(jù)選擇線。A0=1時(shí),地址有效;A0=0時(shí),數(shù)據(jù)有效,即用奇數(shù)地址傳送地址,用偶數(shù)地址傳送數(shù)據(jù)。雖然此方法實(shí)現(xiàn)起來(lái)電路簡(jiǎn)單,但在編程時(shí)卻需要考慮發(fā)送的數(shù)據(jù)何時(shí)作為CAN控制器的地址,何時(shí)作為CAN控制器的數(shù)據(jù),沒(méi)有從根本上解決非多路復(fù)用方式到多路復(fù)用方式的轉(zhuǎn)換。本文以TMS320F206與SJA1000的連接為例,采用復(fù)雜可編程邏輯器件CPLD,完成了用硬件來(lái)實(shí)現(xiàn)非多路復(fù)用方式到多路復(fù)用方式的轉(zhuǎn)換。

1 多路復(fù)用總線的信號(hào)和時(shí)序

1.1 SJA1000接口的主要信號(hào)說(shuō)明

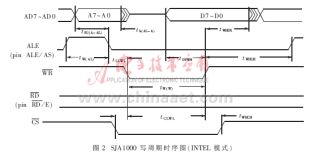

CAN控制器SJA1000提供的微處理器接口方式為典型INTEL或MOTOROLA地址數(shù)據(jù)多路復(fù)用總線模式,主要信號(hào)有地址數(shù)據(jù)信號(hào)AD7~AD0、地址選通信號(hào)ALE、片選信號(hào)/CS、讀信號(hào)/RD、寫信號(hào)/WR、模式選擇信號(hào)MODE。當(dāng)MODE=1時(shí),為INTEL模式;當(dāng)MODE=0時(shí),為MOTOROLA模式。本文描述的地址數(shù)據(jù)多路復(fù)用總線模式均為INTEL模式。圖1和圖2分別為INTEL模式讀、寫周期時(shí)序。AD7~AD0引腳在ALE有效時(shí),傳送的是地址信號(hào);在RD或WR有效時(shí),傳輸?shù)氖菙?shù)據(jù)信號(hào)。

?

?

1.2 SJA1000的時(shí)序分析

??? 以SJA1000的讀時(shí)序?yàn)槔M(jìn)行說(shuō)明。在設(shè)計(jì)轉(zhuǎn)換橋時(shí),多路復(fù)用總線的各信號(hào)必須滿足如下時(shí)間參數(shù)要求:ALE的脈沖寬度(tW(AL))最小為8ns;地址信號(hào)(A0~A7)建立到ALE變?yōu)榈碗娖剿钑r(shí)間(tsu(A-AL))最小為8ns;RD的有效脈寬(tW(R))最小為40ns;/RD為低電平到數(shù)據(jù)信號(hào)(D7~D0)有效所需時(shí)間(tRLOV)最大為50ns;/RD變?yōu)楦唠娖降降刂窋?shù)據(jù)線釋放(即高阻狀態(tài))所需時(shí)間(tRHDZ)最大為30ns。

2 非多路復(fù)用總線的信號(hào)和時(shí)序

2.1 TSM320F206接口的主要信號(hào)說(shuō)明

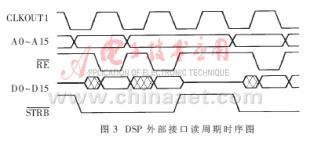

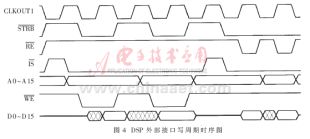

TSM320F206的總線接口方式采用地址和數(shù)據(jù)分離的形式。其主要信號(hào)有地址信號(hào)A0~A15、數(shù)據(jù)信號(hào)D0~D15、讀信號(hào)/RE、寫信號(hào)/WE、閘門信號(hào)STRB、I/O" title="I/O">I/O空間選擇信號(hào)/IS、數(shù)據(jù)存儲(chǔ)器選擇信號(hào)/DS、程序存儲(chǔ)器選擇信號(hào)/PS、機(jī)器時(shí)鐘輸出信號(hào)CLKOUT1。當(dāng)對(duì)外部數(shù)據(jù)存儲(chǔ)器、程序存儲(chǔ)器或I/O空間訪問(wèn)時(shí),STRB有效;當(dāng)對(duì)外部I/O訪問(wèn)時(shí)(即程序中使用PORTR和PORTW指令),IS有效。

2.2 TSM320F206的I/O時(shí)序分析

??? TMS320F206的讀寫時(shí)序[2]如圖3和圖4所示。I/O的讀或?qū)懝ぷ髦芷谝话阍趦蓚€(gè)機(jī)器周期內(nèi)完成。在此期間,IS信號(hào)和地址信號(hào)一直保持有效;閘門信號(hào)STRB發(fā)生在第一個(gè)機(jī)器周期有效后并保持一個(gè)機(jī)器周期以上;RE和WE有效時(shí),數(shù)據(jù)有效。兩次連續(xù)的寫操作(如圖4所示)時(shí),WE的有效間隔時(shí)間tW(WH)最小為(2H-4)ns,而兩次連續(xù)的讀操作(如圖3所示)時(shí),RE的有效間隔時(shí)間tW(RDH)為(H-4)ns~Hns,其中H為0.5倍的機(jī)器時(shí)鐘周期" title="時(shí)鐘周期">時(shí)鐘周期。可見(jiàn)對(duì)于連續(xù)的讀、寫操作,/RE、/WE的有效間隔不同,設(shè)計(jì)電路時(shí)應(yīng)注意此細(xì)節(jié)。在連續(xù)的讀或?qū)懖僮鲿r(shí),/IS信號(hào)一直為有效電平‘0’,無(wú)法以此信號(hào)作為產(chǎn)生SJA1000的ALE、讀、寫信號(hào)起始基準(zhǔn);而在寫周期時(shí),STRB與WE的變化始終保持一致,因此在產(chǎn)生SJA1000寫周期時(shí),可以用STRB作為ALE、/WR產(chǎn)生的起始基準(zhǔn)信號(hào)。但是TSM320F206在連續(xù)的讀操作時(shí),STRB一直保持為低電平,可見(jiàn)在產(chǎn)生SJA1000讀、寫操作周期時(shí),無(wú)法單獨(dú)以它作為ALE、/RD信號(hào)產(chǎn)生的起始基準(zhǔn),需與/IS、/WE、/RE進(jìn)行邏輯組合來(lái)作為SJA1000讀、寫操作周期的起始基準(zhǔn)信號(hào)。

?

?

3 CPLD實(shí)現(xiàn)轉(zhuǎn)換橋的設(shè)計(jì)方法

此轉(zhuǎn)換橋如果用中規(guī)模集成電路(74系列)實(shí)現(xiàn)起來(lái)比較復(fù)雜,工作頻率又較高,布線時(shí)若稍不合理,易引起干擾,使得電路工作不穩(wěn)定,因此這里采用高可靠性的復(fù)雜可編程邏輯器件CPLD,用硬件描述語(yǔ)言VHDL來(lái)實(shí)現(xiàn)。

3.1 轉(zhuǎn)換橋引腳信號(hào)定義

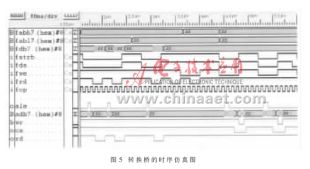

??? 圖5為轉(zhuǎn)換橋的時(shí)序仿真圖,其中轉(zhuǎn)換橋的各引腳信號(hào)與TMS320F206和SJA1000l引腳信號(hào)的對(duì)應(yīng)為:fabl7接A0~A7;fdb7接D0~D7;fds接IS;fstrb接STRB;fwe接WE;frd接RE;fcp接CLKOUT1;ale接/ALE;adb7接AD7~AD0;wr接/WR;rd接RD。

?

3.2 SJA1000讀、寫周期使能信號(hào)和起始基準(zhǔn)信號(hào)的確定

轉(zhuǎn)換橋的基準(zhǔn)時(shí)鐘fcp為TMS320F206的機(jī)器時(shí)鐘輸出信號(hào)CLKOUT1。fcp為20MHz的方波信號(hào)。因?yàn)門MS320F206的讀或?qū)懝ぷ髦芷谝话銥橐弧蓚€(gè)機(jī)器時(shí)鐘周期,此時(shí)基準(zhǔn)時(shí)鐘fcp最多含有四個(gè)邊沿狀態(tài),無(wú)法完成非多路復(fù)用到多路復(fù)用的轉(zhuǎn)換,所以通過(guò)軟件等待設(shè)置,使TMS320F206對(duì)外部總線操作時(shí),由原來(lái)所用的一個(gè)機(jī)器時(shí)鐘周期延長(zhǎng)到四個(gè)機(jī)器時(shí)鐘周期,邊沿狀態(tài)個(gè)數(shù)增加了4倍。另外fcp的脈寬為25ns,這樣可以保證轉(zhuǎn)換橋輸出的多路復(fù)用總線時(shí)序的時(shí)間參數(shù)滿足SJA1000的時(shí)序要求。從上面的時(shí)序分析中可以確定出SJA1000的讀、寫周期的使能信號(hào)(/IS)和起始基準(zhǔn)信號(hào)(/STRB、/WE、/RE邏輯組合)。/IS作為轉(zhuǎn)換橋的片選信號(hào),當(dāng)IS為“0”時(shí),轉(zhuǎn)換橋工作;否則,轉(zhuǎn)換橋的各輸出信號(hào)被懸掛。當(dāng)/IS為“0”、/STRB為“0”、/WE為“0”、/RE為“1”時(shí),DSP開(kāi)始對(duì)外部I/O進(jìn)行寫操作,在后面緊跟的四個(gè)DSP機(jī)器時(shí)鐘周期產(chǎn)生出1個(gè)SJA1000的寫周期;當(dāng)/IS為“0”、/STRB為“0”、/WE為“1”、/RE為“1”時(shí),DSP開(kāi)始對(duì)外部I/O進(jìn)行讀操作,在后面緊跟的四個(gè)DSP機(jī)器時(shí)鐘周期產(chǎn)生出1個(gè)SJA1000的讀周期。

3.3 讀操作轉(zhuǎn)換過(guò)程

通過(guò)軟件等待設(shè)置,使DSP的 I/O讀、寫操作需四個(gè)機(jī)器時(shí)鐘周期。在第一個(gè)時(shí)鐘周期的上升沿" title="上升沿">上升沿產(chǎn)生ale信號(hào)(脈寬為0.5倍的機(jī)器時(shí)鐘周期),同時(shí)將DSP輸入的低八位地址fabl7鎖存并送到地址數(shù)據(jù)復(fù)用總線adb7,并保持到第二個(gè)時(shí)鐘周期的上升沿為止,此時(shí)adb7為高阻狀態(tài)。第三、第四個(gè)時(shí)鐘周期,DSP的讀信號(hào)frd有效,將此信號(hào)直接送到rd引腳,此時(shí)adb7引腳的數(shù)據(jù)直接送給fdb7引腳,讀操作結(jié)束。

3.4 寫操作轉(zhuǎn)換過(guò)程

在寫操作的四個(gè)時(shí)鐘周期中,在第一個(gè)時(shí)鐘周期的上升沿產(chǎn)生ale信號(hào)(脈寬為一個(gè)機(jī)器時(shí)鐘周期),同時(shí)將DSP輸入的低八位地址fabl7引腳的信號(hào)送到adb7上,并保持到第三個(gè)時(shí)鐘周期結(jié)束。在第四個(gè)時(shí)鐘周期的上升沿產(chǎn)生寫信號(hào)wr(寬度為一個(gè)時(shí)鐘周期),在DSP寫信號(hào)few的上升沿處鎖存數(shù)據(jù)線fdb7來(lái)的信號(hào),并將其送到adb7引腳上,延時(shí)到第五個(gè)時(shí)鐘周期時(shí)把a(bǔ)db7變?yōu)楦咦锠顟B(tài),寫操作結(jié)束。

本文提出的非多路復(fù)用總線到多路復(fù)用總線轉(zhuǎn)換橋采用了Xilinx公司的CPLD芯片XC95144-15-PQ100,并使用該公司開(kāi)發(fā)的集成環(huán)境Fundation F3.1i,將其集成為一塊專用芯片。通過(guò)大量的實(shí)驗(yàn)測(cè)試,此轉(zhuǎn)換橋工作非常穩(wěn)定,現(xiàn)已應(yīng)用到電力網(wǎng)絡(luò)饋線遠(yuǎn)程終端裝置(FTU)中。

?

參考文獻(xiàn)

1 廖傳書,李 崇.CAN總線控制器與DSP的接口.電子技術(shù)應(yīng)用,2002;28(11)

2 TMS320LC206 Digital Signal Processors Data.Texas Instruments,1999

3 Stand-alone CAN Controller SJA1000 Data,Philips Semiconductors,2000

4 李 剛,林 凌,葉文宇. TMS320F206 DSP結(jié)構(gòu)、原理及應(yīng)用.北京:北京航空航天大學(xué)出版社,2002

5 徐志軍,徐光輝.CPLD/FPGA的開(kāi)發(fā)與應(yīng)用.北京:電子工業(yè)出版社,2002