引言

在數(shù)字信息傳輸中,基帶數(shù)字信號(hào)通常要經(jīng)過調(diào)制器調(diào)制,,將頻率搬移到適合信息傳輸?shù)念l段上,。2FSK就是用數(shù)字信號(hào)去調(diào)制載波的頻率(移頻鍵控),由于它具有方法簡(jiǎn)單,、易于實(shí)現(xiàn),、抗噪聲和抗衰落性能較強(qiáng)等優(yōu)點(diǎn),因此在現(xiàn)代數(shù)字通信系統(tǒng)的低,、中速數(shù)據(jù)傳輸中得到了廣泛應(yīng)用,。

直接數(shù)字頻率合成技術(shù)(DDS)將先進(jìn)的數(shù)字處理技術(shù)與方法引入信號(hào)合成領(lǐng)域。DDS器件采用高速數(shù)字電路和高速D/A轉(zhuǎn)換技術(shù),,具備頻率轉(zhuǎn)換時(shí)間短,、頻率分辨率高、頻率穩(wěn)定度高,、輸出信號(hào)頻率和相位可快速程控切換等優(yōu)點(diǎn),,可以實(shí)現(xiàn)對(duì)信號(hào)的全數(shù)字式調(diào)制。

DDS芯片——AD9833的介紹

AD9833是一塊完全集成的DDS芯片,,僅需要1個(gè)外部參考時(shí)鐘,、1個(gè)低精度電阻器和一些解耦電容器就能產(chǎn)生高達(dá)12.5MHz的正弦波。除了產(chǎn)生射頻信號(hào)外,,該電路還廣泛應(yīng)用于各種調(diào)制解調(diào)方案,,這些方案全都用在了數(shù)字領(lǐng)域。

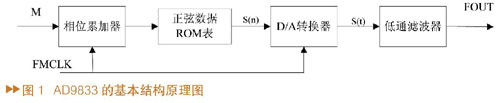

AD9833的內(nèi)部電路包括數(shù)字器件和模擬器件兩部分,。主要由相位累加器(由加法器和相位寄存器組成),、ROM波形查詢表、數(shù)模轉(zhuǎn)換器DAC和低通濾波器LPF構(gòu)成,。AD9833的基本結(jié)構(gòu)原理如圖1所示,。其中M為頻率控制字、FMCLK為時(shí)鐘頻率,相位累加器在時(shí)鐘FMCLK的控制下以步長(zhǎng)M作累加,,相位寄存器的輸出與相位控制字相加后輸入到正弦查詢表地址中,。正弦查詢表包含1個(gè)周期正弦波的數(shù)字幅度信息,每個(gè)地址對(duì)應(yīng)正弦波中0°~360°范圍內(nèi)的1個(gè)相位點(diǎn),。查詢表把輸入的地址相位信息映射成正弦波幅度的數(shù)字量信號(hào)S(n),,經(jīng)D/A轉(zhuǎn)化器變成階梯波S(t),再經(jīng)低通濾波器平滑后就可得到合成的信號(hào)波形,。其形狀取決于波形ROM中存放的幅碼,,因此用DDS可以產(chǎn)生任意波形。輸出正弦波頻率為:fOUT=M(fMCK/228),,其中,,M為頻率控制字,由外部編程給定,,其范圍為0≤M≤228-1 ,。

硬件電路連接

本設(shè)計(jì)用Silicon Labs公司推出的完全集成的混合信號(hào)片上系統(tǒng)C8051F060來控制AD9833,C8051F060有大量的數(shù)字資源需要通過4個(gè)低端I/O端口P0,、P1,、P2和P3才能使用。P0,、P1,、P2和P3的每個(gè)引腳既可定義為通用的端口I/O引腳,又可以分配給一個(gè)數(shù)字外設(shè)或功能(例如:UART0或INT1),。不管引腳被分配給一個(gè)數(shù)字外設(shè)或是作為通用I/O,,總是可以通過讀相應(yīng)的數(shù)據(jù)寄存器得到端口I/O引腳的狀態(tài)。

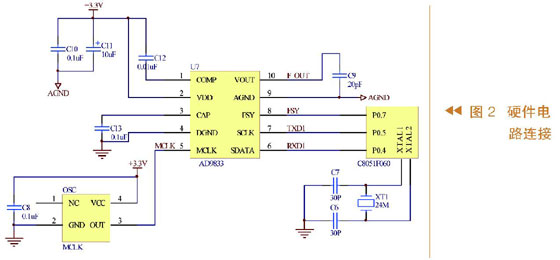

AD9833與單片機(jī)C8051F060連接時(shí),,使用單片機(jī)的3個(gè)I/O口和AD9833連接,。FSYNC(控制輸入,低電平有效)與單片機(jī)的可編程管腳P0.7連接,,SCLK(串行時(shí)鐘輸入)與可編程管腳P0.4連接,,SDATA(串行數(shù)據(jù)輸入)與可編程管腳P0.5連接。三個(gè)可編程管腳都可用軟件編程實(shí)現(xiàn)數(shù)據(jù)的傳送,。硬件電路連接如圖2所示,,單片機(jī)產(chǎn)生控制信號(hào)和波形參數(shù),通過串行接口將數(shù)據(jù)傳送到AD9833,,經(jīng)AD9833輸出的正弦波信號(hào)再經(jīng)低通濾波后輸出,。

軟件控制

寫數(shù)據(jù)到控制寄存器

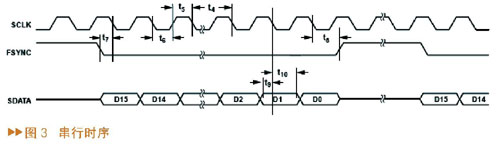

單片機(jī)傳送數(shù)據(jù)到AD9833的時(shí)序如圖3所示:FSYNC引腳是使能引腳,電平觸發(fā)方式,,低電平有效。進(jìn)行串行數(shù)據(jù)傳輸時(shí),F(xiàn)SYNC 引腳必須置低,,這種情況下,,16個(gè)SCLK的下降沿?cái)?shù)據(jù)被送到AD9833的輸入移位寄存器。在第16個(gè)SCLK的下降沿FSYNC可以被置高,,當(dāng)然,,也可以連續(xù)加載多個(gè)16位數(shù)據(jù),僅在最后一個(gè)數(shù)據(jù)的第16個(gè)SCLK的下降沿時(shí)將FSYNC置高,。需要注意的是,,在FSYNC開始變?yōu)榈颓埃磳㈤_始寫數(shù)據(jù)時(shí))),SCLK必須為高電平,。

單片機(jī)寫16位數(shù)據(jù)到AD9833時(shí),,高位在前,低位在后,。用軟件模擬時(shí)鐘信號(hào)和片選信號(hào),。傳送數(shù)據(jù)的程序如下:

SCLK =1; //時(shí)鐘信號(hào)

FSYNC=1;

Delay(100) ; 延時(shí)子程序

FSYNC=0; //片選有效

for(i=0;i<16;i++)

{ SDATA="datas"&0x8000;

SCLK=0; //時(shí)鐘信號(hào)下降沿?cái)?shù)據(jù)送入I/O口。

Delay(50) ;

SCLK=1;

datas=datas<<1; //16位數(shù)據(jù)從高位到低位送入

}

Delay(50) ;

FSYNC=1;

SCLK=0;

數(shù)據(jù)寫入方式

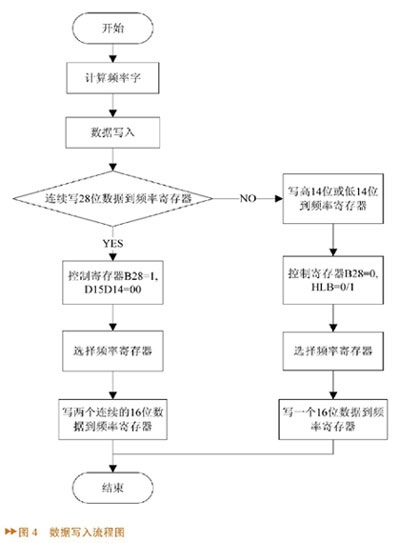

設(shè)置控制寄存器中的D15D14=00,,表示數(shù)據(jù)寫入控制寄存器,;設(shè)置B28(D13)=1,表示28位數(shù)據(jù)可以連續(xù)寫入頻率寄存器,,默認(rèn)先寫入低14位頻率字,,再連續(xù)寫入高14位頻率字到頻率寄存器中;設(shè)置B28(D13)=0,,表示28位數(shù)據(jù)分兩次寫入頻率寄存器,,此時(shí)配合 HLB 的值使用(當(dāng)HLB=1時(shí)允許高14位頻率字寫入到頻率寄存器,當(dāng)HLB=0時(shí)允許低14位頻率字寫入到頻率寄存器),。因此寫入到控制寄存器的數(shù)據(jù)可為:0010 0000 0000 0000,,表示設(shè)置連續(xù)28位頻率字。數(shù)據(jù)寫入流程圖如圖4所示,。

選擇頻率寄存器

由于AD9833片內(nèi)有2個(gè)頻率寄存器,,即FREQ0、FREQ1,,因此要確定是將頻率控制字寫入哪一個(gè),。這可通過設(shè)置 D15D14 的值來進(jìn)行選擇,當(dāng)D15D14=01表示14位的頻率字將寫入FREQ0,;當(dāng)D15D14=10表示14位的頻率字將寫入FREQ1,。以輸出頻率為7230Hz為例,介紹寫入到頻率寄存器1的頻率字,。

寫入低14位數(shù)據(jù)為:1011 0110 0001 1110,,表示將低14位頻率字寫入FREQ1,。

寫入高14位數(shù)據(jù)為:1000 0000 0000 1011,表示將高14位頻率字寫入FREQ1,。

主程序設(shè)計(jì)

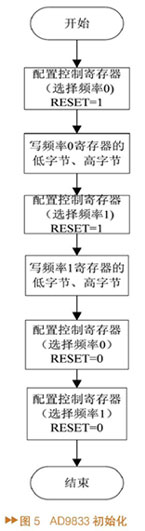

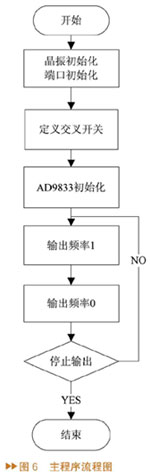

首先,,對(duì)C8051F060單片機(jī)初始化,這包括單片機(jī)晶振初始化,、端口初始化,,定義控制AD9833的I/O接口及交叉開關(guān),接著初始化AD9833,。當(dāng)AD9833初始化時(shí),,為避免DAC產(chǎn)生虛假輸出,RESET必須置為1(RESET不會(huì)復(fù)位頻率,、相位和控制寄存器),,直到配置完畢,需要輸出時(shí)才將RESET置為0,;RESET為0后的8-9個(gè)MCLK時(shí)鐘周期可在DAC的輸出端觀察到波形,。AD9833初始化流程圖如圖5所示。然后,,寫頻率寄存器0的控制字(0x2000),,在進(jìn)行FSK調(diào)制時(shí),AD9833的兩個(gè)頻率寄存器裝載不同的頻率值,,本實(shí)驗(yàn)中,,頻率寄存器0裝載低頻率6830Hz,頻率寄存器1裝載高頻率7230Hz,,通過設(shè)置AD9833的控制寄存器的FSELECT位來選擇頻率寄存器,。主程序流程如圖6所示。

實(shí)驗(yàn)結(jié)果

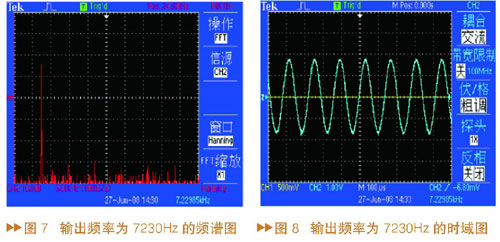

在示波器上能觀測(cè)到FSK調(diào)制信號(hào),,為方便截圖,,設(shè)置頻率為7230Hz的正弦信號(hào)在示波器上進(jìn)行觀察,圖7是頻率為7230Hz的正弦信號(hào)經(jīng)過低通濾波之后的頻譜圖,。由圖7可以看出,,實(shí)際輸出頻率為7.22985Hz。圖8是對(duì)應(yīng)的時(shí)域圖形,。

結(jié)論

本實(shí)驗(yàn)中設(shè)計(jì)的FSK調(diào)制信號(hào),,在工程中有較強(qiáng)的實(shí)用價(jià)值,已成功應(yīng)用于井下聲波傳輸系統(tǒng)中,。