摘 要: 針對(duì)多種采集信號(hào)類型,設(shè)計(jì)了一種采用CPLD實(shí)現(xiàn)信號(hào)采集控制,、信號(hào)處理,、通訊及輸出控制等功能的復(fù)合數(shù)據(jù)采集" title="數(shù)據(jù)采集">數(shù)據(jù)采集控制板,并分析了其相關(guān)應(yīng)用性能,。

關(guān)鍵詞: CPLD EPP接口 編碼器 數(shù)據(jù)采集

在需要采集多路模擬信號(hào),、開(kāi)關(guān)信號(hào)、頻率(計(jì)數(shù))信號(hào)以及編碼器信號(hào)等的數(shù)據(jù)采集應(yīng)用中,,利用通用板卡構(gòu)成計(jì)算機(jī)測(cè)控系統(tǒng)是可行的,,但對(duì)于產(chǎn)品的批量應(yīng)用,其成本與綜合性能不能令人滿意,。技術(shù)成熟的CPLD芯片的應(yīng)用,,可以很好地將邏輯控制、數(shù)字信號(hào)處理等功能集于一身,,使以往需要利用多塊信號(hào)板卡才能完成的任務(wù)整合于同一采集控制器中,,從而有效地提高測(cè)控系統(tǒng)的可靠性,降低測(cè)控系統(tǒng)的實(shí)現(xiàn)成本,。

本文設(shè)計(jì)一種基于CPLD的數(shù)據(jù)采集控制板,。它能實(shí)現(xiàn)信號(hào)采集與控制、信號(hào)處理、通訊及輸出控制等功能,。

1 總體設(shè)計(jì)方案

本專用數(shù)據(jù)采集控制板利用CPLD作為主控制器,,統(tǒng)一協(xié)調(diào)通道切換與數(shù)字信號(hào)處理、實(shí)現(xiàn)數(shù)據(jù)采集與接口傳輸邏輯控制,。該數(shù)據(jù)采集控制板共有四種類型的信號(hào)輸入和一種開(kāi)關(guān)信號(hào)量輸出,。圖1給出其基本硬件模塊組成。

利用CPLD的資源和結(jié)構(gòu)特點(diǎn)是本設(shè)計(jì)的核心,。為提高編碼器輸入信號(hào)" title="輸入信號(hào)">輸入信號(hào)的分辨力,,配套設(shè)計(jì)一個(gè)四倍頻電路,并在通道后端設(shè)計(jì)一個(gè)脈沖靜態(tài)計(jì)數(shù)電路,,使輸入信號(hào)轉(zhuǎn)換為8bit信號(hào)掛接到采集板總線上,。八路模擬輸入信號(hào)主要依靠CPLD實(shí)現(xiàn)通道切換和A/D" title="A/D">A/D采樣,采樣數(shù)據(jù)也以8bit信號(hào)并行進(jìn)入總線,??紤]到提高計(jì)數(shù)精度的要求,對(duì)兩路頻率輸入信號(hào)設(shè)計(jì)了一個(gè)動(dòng)態(tài)計(jì)數(shù)電路,,使計(jì)數(shù)值通過(guò)總線讀出,。I/O" title="I/O">I/O切換控制、EPP接口電路等都按一定的邏輯要求采用同一CPLD元件來(lái)實(shí)現(xiàn),。如此可使硬件電路十分簡(jiǎn)單,,并有利于上位機(jī)編程實(shí)現(xiàn)。

2 數(shù)據(jù)接口

根據(jù)IEEE1284標(biāo)準(zhǔn),,在標(biāo)準(zhǔn)并行口(SPP),、增強(qiáng)并行口(EPP)和擴(kuò)展并行口(ECP)三種模式中,,EPP模式既具有雙向數(shù)據(jù)傳輸功能,,又具有較高的數(shù)據(jù)傳輸能力,且編程操作相對(duì)容易,,最適合在數(shù)據(jù)采集系統(tǒng)中使用[1],。

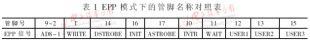

從硬件設(shè)計(jì)角度考慮,EPP接口的主要功能之一是將采集到的數(shù)據(jù)上傳給計(jì)算機(jī)或?qū)㈤_(kāi)關(guān)控制命令下載到采集控制板(數(shù)據(jù)流對(duì)應(yīng)8bit數(shù)據(jù)端口),;之二是實(shí)現(xiàn)硬件接口之間的信號(hào)通訊握手(控制狀態(tài)對(duì)應(yīng)其它I/O端口),。EPP協(xié)議定義了四種數(shù)據(jù)傳輸基本操作:數(shù)據(jù)讀、數(shù)據(jù)寫,、地址讀,、地址寫。工作時(shí)首先寫入I/O鎖存地址即模塊操作的I/O地址,,然后進(jìn)行相應(yīng)的讀出或?qū)懭氩僮?。如果不需I/O地址變化,那么就不再進(jìn)行I/O地址鎖存操作。EPP模式下一共定義17根信號(hào)線,,除8根雙向地址線和數(shù)據(jù)復(fù)用線外,,還有輸出控制信號(hào)線WRITE、DSTROBE,、ASTROBE,、INIT,其中WRITE,、DSTROBE和ASTROBE用于表示數(shù)據(jù)讀寫操作,。WRITE為低時(shí)表示正在進(jìn)行寫操作,DSTROBE為低表示進(jìn)行數(shù)據(jù)操作,,而ASTROBE為低則表示進(jìn)行地址操作,。EPP的INIT信號(hào)用來(lái)復(fù)位打印機(jī),本設(shè)計(jì)用來(lái)預(yù)置光電編碼器的初始計(jì)數(shù)值,。另外還有五根狀態(tài)信號(hào)線,。WAIT信號(hào)由外設(shè)發(fā)出,高電平表示正在進(jìn)行讀寫操作,,低電平表示操作完成,。但本設(shè)計(jì)沒(méi)有利用該信號(hào),因?yàn)榍懊嫒齻€(gè)讀寫信號(hào)已完全能滿足要求,。MAX197數(shù)據(jù)轉(zhuǎn)換結(jié)束信號(hào)EOC連接到并口的SELECT線上,,主機(jī)查詢到SELECT線為低時(shí),表示一次A/D轉(zhuǎn)換結(jié)束,,可以讀取轉(zhuǎn)換結(jié)果,。其余三根狀態(tài)線空置作為備用。 表1給出了IEEE1284協(xié)議EPP模式下的管腳定義,。

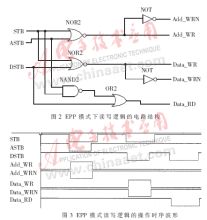

根據(jù)IEEE1284標(biāo)準(zhǔn)對(duì)EPP模式的地址,、數(shù)據(jù)讀寫操作的規(guī)定,可采用圖2的邏輯結(jié)構(gòu)分別實(shí)現(xiàn)地址寫,、數(shù)據(jù)寫和數(shù)據(jù)讀,。在圖2中,輸入信號(hào)中STB表示寫信號(hào),,ASTB表示地址寫信號(hào),,DSTB表示數(shù)據(jù)寫信號(hào);輸出信號(hào)中Add_WR表示地址寫信號(hào),、高電平有效,,Add_WRN表示地址寫信號(hào)、低電平有效,,Data_WR表示數(shù)據(jù)寫信號(hào),、高電平有效,、Data_WRN表示數(shù)據(jù)寫信號(hào)、低電平有效,;Data_RD表示數(shù)據(jù)讀信號(hào),。如此設(shè)計(jì)的目的是使該接口能方便地適應(yīng)各種邏輯器件的操作要求。圖3給出了采用MAXPLUS軟件對(duì)上述邏輯信號(hào)進(jìn)行仿真的操作時(shí)序波形,。

EPP模式可在上位機(jī)BIOS中設(shè)置或通過(guò)寫ECR寄存器直接設(shè)置(并行適配器基地址為0X378H,,I/O端口地址為77AH)。

3 編碼器信號(hào)處理

對(duì)于編碼器輸入信號(hào),,針對(duì)增量式光電編碼器的輸出具有A相,、B相方波正交信號(hào),而且二者相序取決于編碼器的正反轉(zhuǎn)方向,,設(shè)計(jì)了一個(gè)四倍頻及判向電路,,如圖4所示。

在圖4中,,CLK信號(hào)來(lái)自獨(dú)立振蕩源,,其頻率高于編碼器最大輸出頻率四倍以上,但也不宜過(guò)高,,以免導(dǎo)致CPLD內(nèi)部結(jié)構(gòu)中信號(hào)競(jìng)爭(zhēng)等問(wèn)題,。INA和INB分別為編碼器輸入的A相信號(hào)和B相信號(hào),CNT_UP和CNT_DN分別為輸出的正轉(zhuǎn)倍頻信號(hào)和反轉(zhuǎn)倍頻信號(hào),。為保證編碼器處于任何轉(zhuǎn)角位置都能可靠地讀出數(shù)據(jù),,編碼器倍頻信號(hào)最終以16bit靜態(tài)計(jì)數(shù)碼方式輸出,CNT_UP和CNT_DN分別作為后續(xù)靜態(tài)計(jì)數(shù)電路的“加”和“減”計(jì)數(shù)輸入信號(hào)端,。在限定轉(zhuǎn)動(dòng)角度≤6×360°情況下,,對(duì)于16bit計(jì)數(shù)碼,計(jì)數(shù)電路允許的最大計(jì)數(shù)值為65536,,計(jì)數(shù)值可以按高低八位分兩次讀出,。為提高編碼器工作可靠性,也可以考慮進(jìn)行格雷碼轉(zhuǎn)換,。圖5給出的是圖4電路的信號(hào)仿真波形,。

4 頻率測(cè)量

對(duì)于頻率輸入信號(hào),采用等精度測(cè)頻方法測(cè)量頻率,。這種方法在實(shí)際閘門時(shí)間為被測(cè)信號(hào)頻率整數(shù)倍的條件下,對(duì)被測(cè)信號(hào)計(jì)數(shù)時(shí)產(chǎn)生的±1個(gè)字誤差可以完全消除掉[3],,并可使整個(gè)頻率區(qū)域保持恒定的測(cè)試精度,。

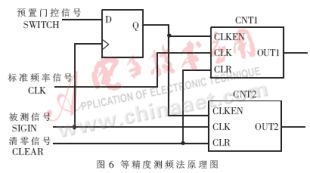

圖6給出了等精度測(cè)量原理圖,其測(cè)量原理為:首先給出閘門開(kāi)啟信號(hào)(預(yù)置門控信號(hào)SWITCH的上升沿),,此時(shí)計(jì)數(shù)器CNT1和CNT2并不開(kāi)始計(jì)數(shù),,而是等到被測(cè)信號(hào)SIGIN的上升沿到來(lái)時(shí),,計(jì)數(shù)器才開(kāi)始真正計(jì)數(shù)。經(jīng)過(guò)一段時(shí)間后,,預(yù)置閘門關(guān)閉信號(hào)(門控信號(hào)SWITCH的下降沿)到來(lái)時(shí),,計(jì)數(shù)器并不立即停止計(jì)數(shù),而是等到被測(cè)信號(hào)SIGIN的上升沿到來(lái)時(shí)才結(jié)束計(jì)數(shù),,完成一次測(cè)量過(guò)程,。此時(shí)可分別讀出計(jì)數(shù)器CNT1和CNT2的計(jì)數(shù)值OUT1和OUT2,用被測(cè)信號(hào)SIGIN的計(jì)數(shù)值OUT2除以標(biāo)準(zhǔn)信號(hào)CLK的計(jì)數(shù)值OUT1,,再乘以標(biāo)準(zhǔn)信號(hào)CLK的頻率值就得到了被測(cè)信號(hào)SIGIN的頻率值,。

使用時(shí)為提高測(cè)量精度,基準(zhǔn)信號(hào)CLK可以采用高精度的時(shí)鐘源,,因?qū)r(shí)鐘源和被測(cè)信號(hào)同步計(jì)數(shù),,計(jì)數(shù)時(shí)間長(zhǎng)度不會(huì)影響計(jì)算結(jié)果。圖7給出了等精度測(cè)頻法信號(hào)仿真波形圖,。

5 A/D轉(zhuǎn)換器與I/O切換控制

對(duì)于模擬輸入信號(hào),,采用12bit的MAX197作為A/D信號(hào)轉(zhuǎn)換器。該控制字" title="控制字">控制字器件工作的基本過(guò)程是:首先由地址總線選通MAX197,,然后通過(guò)數(shù)據(jù)總線向MAX197內(nèi)部寄存器寫入模擬通道控制字,。該控制字決定了所選的通道號(hào)、通道輸入電壓范圍,、極性以及內(nèi)部或外部觸發(fā)采集方式等,。例如,輸入電壓范圍為雙極性,、內(nèi)部觸發(fā)采集方式,、第一通道,則應(yīng)寫入16進(jìn)制數(shù)48H,,而對(duì)第八通道則寫入4FH,。控制字寫入后,,MAX197立即啟動(dòng)通道轉(zhuǎn)換,,經(jīng)過(guò)約10μs后轉(zhuǎn)換完畢。轉(zhuǎn)換結(jié)果放置在數(shù)據(jù)總線上,,首先將其高低位切換腳HBEN置為低,,此時(shí)數(shù)據(jù)總線先讀取結(jié)果的低八位,再置HBEN為高,,則結(jié)果的高四位放在MAX197的D0~D3口上,。同時(shí)置腳INT為低,通知控制器轉(zhuǎn)換完成,。MAX197的轉(zhuǎn)換結(jié)果用補(bǔ)碼表示,,最高位為符號(hào)位,。

本系統(tǒng)中還具有八路開(kāi)關(guān)量輸入輸出功能切換控制。這兩種功能分別由CPLD內(nèi)部的74244和74373實(shí)現(xiàn),。接口邏輯如圖8所示,。外部接口通過(guò)光耦隔離輸入輸出。開(kāi)關(guān)量寫入的順序是先由地址總線選通74373,,然后寫入相應(yīng)的命令字,。數(shù)字量讀入與此類似。具體控制信號(hào)由 EPP總線讀寫邏輯給出,。

?

6 驅(qū)動(dòng)軟件實(shí)現(xiàn)

考慮到NI公司LabView環(huán)境圖形化編程簡(jiǎn)便,、易于實(shí)現(xiàn)等特點(diǎn),通過(guò)設(shè)計(jì)動(dòng)態(tài)鏈接函數(shù)庫(kù)(DLL)與直接端口操作相結(jié)合實(shí)現(xiàn)采集板硬件驅(qū)動(dòng),。在程序編制過(guò)程中,,先利用VC++生成DLL,然后在LabView中使用CLF節(jié)點(diǎn)調(diào)用DLL,。對(duì)于直接端口操作,,使用LabView中的“In Port”和“Out Port”節(jié)點(diǎn),對(duì)端口實(shí)現(xiàn)操作,。當(dāng)然,,為使用方便起見(jiàn),也可以將I/O切換控制,、編碼器,、A/D數(shù)據(jù)采集、計(jì)數(shù)器等硬件特有功能設(shè)計(jì)成專用模塊供LabView直接圖形化調(diào)用,。

采集控制板的上述硬件模塊方案設(shè)計(jì),,可以利用適當(dāng)規(guī)模的CPLD實(shí)現(xiàn)。此舉除了成本優(yōu)勢(shì)外,,還有體積減小,、硬件集成度提高等優(yōu)點(diǎn),也為提高采集器可靠性創(chuàng)造了條件,。CPLD的各種邏輯功能設(shè)計(jì),,由于有功能強(qiáng)大的仿真軟件工具,設(shè)計(jì)過(guò)程的快速高效也不言而喻,。上述設(shè)計(jì)已經(jīng)在其實(shí)用測(cè)控設(shè)備中投入應(yīng)用,,在無(wú)板載FIFO情況下,A/D速度可以達(dá)到40kHz以上,;有板載FIFO情況下,,A/D速度可以達(dá)到A/D采集元件標(biāo)稱上限。EPP端口完全能滿足板載功能模塊的各類數(shù)據(jù)傳輸要求,。通過(guò)現(xiàn)場(chǎng)反饋的情況來(lái)看,,采集控制器本身的工業(yè)環(huán)境抗干擾性能和運(yùn)行穩(wěn)定性均表現(xiàn)良好。

參考文獻(xiàn)

1 陳培玉,,闕沛文. EPP并口與ADSP2181 DSP的接口設(shè)計(jì)[J]. 電測(cè)與儀表,, 2003;40(11)

2 張 斌,,姚英學(xué),,陳朔東. 復(fù)合式光電編碼器信號(hào)處理電路的設(shè)計(jì). [J ].機(jī)械工程師,2003,;(10)

3 侯俊勇. 高速高精度頻率測(cè)量系統(tǒng)的CPLD實(shí)現(xiàn)[J]. 儀器儀表學(xué)報(bào),,2003;24(z2)

3 張志明,,李蓉艷,,王 磊. 等精度頻率信號(hào)采集測(cè)試系統(tǒng)[J].儀器儀表學(xué)報(bào),2003,;23(z1)

4 林 凱,,何 川,毛樂(lè)山. 基于LabVIEW的多通道振動(dòng)測(cè)試與分析系統(tǒng). [J ]. 清華大學(xué)學(xué)報(bào)(自然科學(xué)版),,2003,;43(5)