硬件描述語言(HDL)是相對于一般的計算機軟件語言如C,Pascal而言的。HDL是用于設(shè)計硬件電子系統(tǒng)的計算機語言,它描述電子系統(tǒng)的邏輯功能、電路結(jié)構(gòu)和連接方式。設(shè)計者可以利用HDL程序來描述所希望的電路系統(tǒng),規(guī)定其結(jié)構(gòu)特征和電路的行為方式,然后利用綜合器和適配器將此程序變成能控制FPGA和CPLD內(nèi)部結(jié)構(gòu),并實現(xiàn)相應(yīng)邏輯功能的門級或更底層的結(jié)構(gòu)網(wǎng)表文件和下載文件。VHDL(Very High Speed Integrated Circuit Hardware descriptionLangtuage)主要用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)、行為、功能和接口。與其他的HDL語言相比,VHDL具有更強的行為描述能力,從而決定了它成為系統(tǒng)設(shè)計領(lǐng)域最佳的硬件描述語言。強大的行為描述能力是避開具體的器件結(jié)構(gòu)。從邏輯行為上描述和設(shè)計大規(guī)模電子系統(tǒng)的重要保證。在文獻中作者從不同的角度闡述了EDA技術(shù)的應(yīng)用,它具有功能強大、描述能力強、可移植性好、研制周期短、成本低等特點,即使設(shè)計者不懂硬件的結(jié)構(gòu),也能進行獨立的設(shè)計。本文以Alter公司提供的Max+PlusⅡ為平臺,設(shè)計一個可變速的彩燈控制器,可以在不修改硬件電路的基礎(chǔ)上,僅通過更改軟件就能實現(xiàn)任意修改花型的編程控制方案,實現(xiàn)控制16只LED以8種花型和4種速度循環(huán)變化顯示,而且設(shè)計非常方便,設(shè)計的電路保密性強。

l 設(shè)計原理

用VHDL進行設(shè)計,首先應(yīng)該理解,VHDL語言是一種全方位硬件描述語言,包括系統(tǒng)行為級,寄存器傳輸級和邏輯門級多個設(shè)計層次。應(yīng)充分利用VHDL“自頂向下”的設(shè)計優(yōu)點以及層次化的設(shè)計概念,層次概念對于設(shè)計復(fù)雜的數(shù)字系統(tǒng)是非常有用的,它使得我們可以從簡單的單元入手,逐漸構(gòu)成龐大而復(fù)雜的系統(tǒng)。

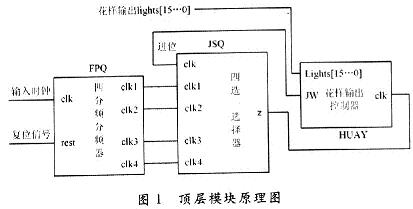

首先應(yīng)進行系統(tǒng)模塊的劃分,規(guī)定每一個模塊的功能以及各模塊之間的接口,最終設(shè)計方案分為三大模塊:16路花樣彩燈控制器、四頻率輸出分頻器、四選一控制器。四選一控制器從分頻器中選擇不同頻率的時鐘信號輸送到彩燈花樣控制器,從而達到控制彩燈閃爍速度的快慢和花型的的變換。

下面是本次設(shè)計的頂層模塊原理圖如圖1所示。

2 子模塊及其功能

(1)四頻率輸出分頻器。根據(jù)要求有4種速度的變化,每種都要顯示8種花樣,就要用到三位計數(shù)器和16位數(shù)字譯碼器。其次,速度有4種變化,而只有一個輸入的時鐘信號,所以要對輸入的時鐘信號進行分頻,本次設(shè)計采用了二分頻、四分頻、八分頻和15分頻得到4種不同頻率的信號。

二分頻電路的程序代碼如下:

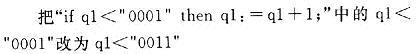

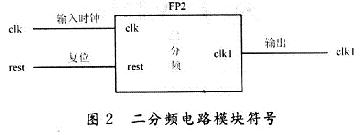

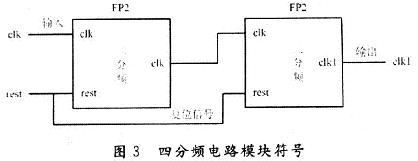

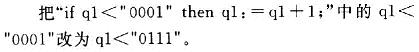

四分頻電路的設(shè)計有兩種方案:一是把兩個二分頻電路串聯(lián)起來(見圖2,3),實現(xiàn)四分頻;二是修改二分頻電路的程序代碼來實現(xiàn),做如下修改:

同理,八分頻電路的設(shè)計也有兩種方案:一種是把兩個四分頻電路串聯(lián)起來,實現(xiàn)八分頻;一種是修改二分頻電路的程序代碼,只需做如下修改即可:

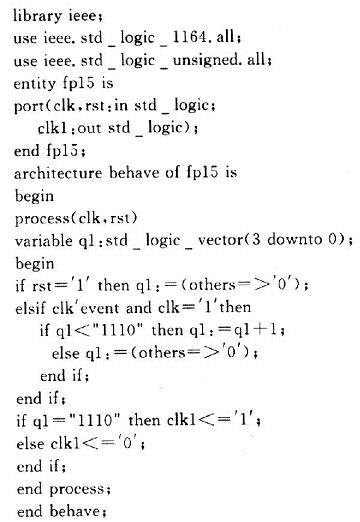

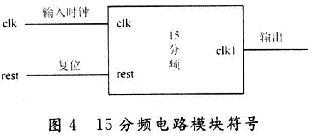

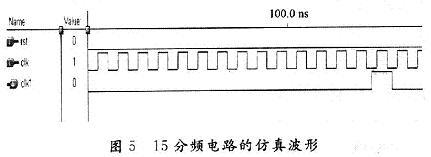

15分頻電路如圖4所示,仿真圖如圖5所示。代碼如下:

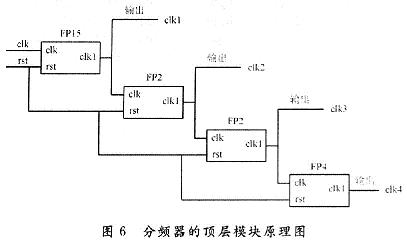

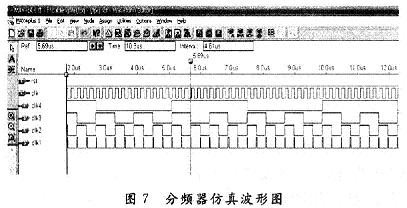

四頻率輸出分頻器的頂層模塊原理圖如圖6所示,仿真波形如圖7所示。

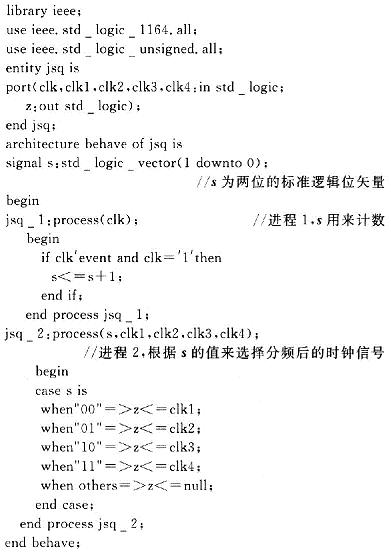

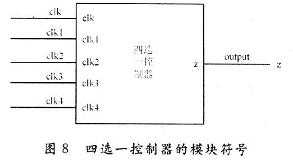

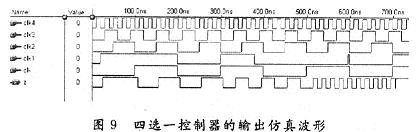

(2)四選一控制器。四選一控制器的功能是從分頻器中選擇不同的時鐘信號送給彩燈控制器,實現(xiàn)彩燈閃爍頻率的變化,如圖8,9所示。源代碼如下:

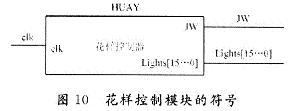

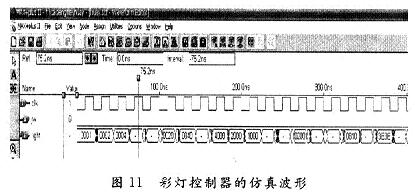

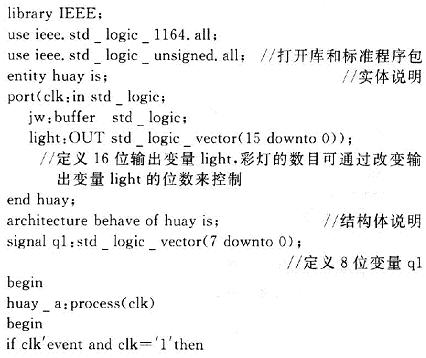

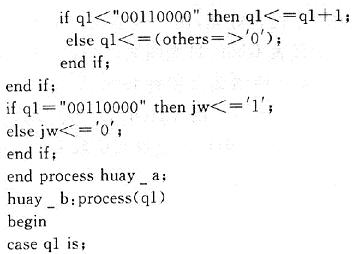

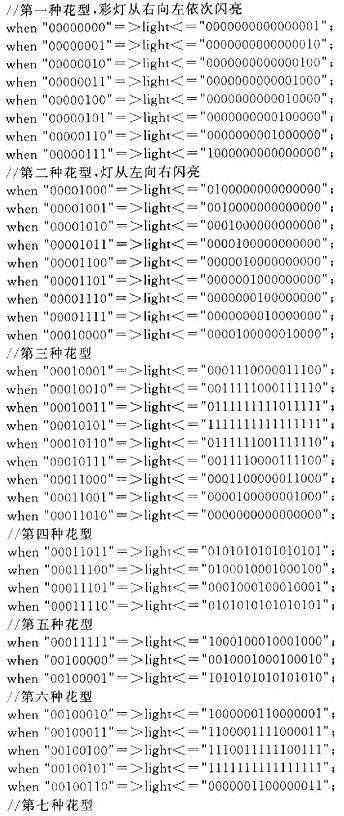

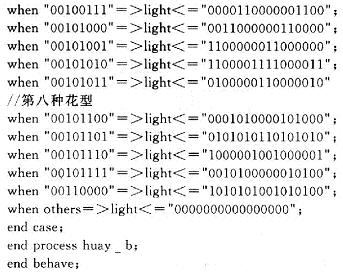

(3)彩燈控制器。彩燈控制器電路是整個設(shè)計的核心,它控制整個設(shè)計的輸出效果也就是圖案的樣式變化。在電路中用1代表燈亮,用O代表燈滅,由0,1按不同的規(guī)律組合代表不同的燈光圖案,同時使其選擇不同的頻率,以實現(xiàn)多種圖案及多種頻率的花樣功能顯示。該程序充分證明了用VHDL設(shè)計電路的靈活性,即可以通過改變程序中輸出變量的位數(shù)來改變彩燈的數(shù)目。如圖10,1l所示。

代碼如下:

3 結(jié)語

使用VHDL語言設(shè)計電路,思路簡單,功能明了。使用Max+PlusⅡ設(shè)計電路不僅可以進行邏輯仿真,還可以進行時序仿真,使用PLD不僅省去了電路制作的麻煩,還可以反復(fù)進行硬件的實驗,非常方便地修改設(shè)計,且設(shè)計的電路的保密性強。總之,采用EDA技術(shù)使得復(fù)雜的電子系統(tǒng)的設(shè)計變的簡單易行,提高了設(shè)計的效率。