引言

隨著SoC設(shè)計(jì)日趨復(fù)雜,驗(yàn)證成為SoC設(shè)計(jì)過程中最關(guān)鍵的環(huán)節(jié)。本文介紹了Synopsys的RVM驗(yàn)證方法學(xué),采用Vera硬件驗(yàn)證工具以及OpenVera驗(yàn)證語言建立目標(biāo)模型環(huán)境,自動生成激勵(lì),完成自核對測試、覆蓋率分析等工作。通過建立層次化的可重用性驗(yàn)證平臺,大大提高了驗(yàn)證工程師的工作效率。文中以一個(gè)SIMC功能模塊的驗(yàn)證為例,詳細(xì)介紹了RVM驗(yàn)證方法學(xué)在SoC芯片驗(yàn)證中的應(yīng)用。

功能驗(yàn)證

一個(gè)設(shè)計(jì)被綜合前,首先要對RTL描述進(jìn)行邏輯功能驗(yàn)證,以確保模塊或芯片的功能正確性。通常,RTL級的功能驗(yàn)證主要采用自底向上的驗(yàn)證策略,可分為模塊級驗(yàn)證和系統(tǒng)級驗(yàn)證兩個(gè)階段。

傳統(tǒng)驗(yàn)證方法大多是在信號級的接口上直接與待驗(yàn)證設(shè)計(jì)(DUT)通信,即用激勵(lì)直接驅(qū)動DUT的引腳,通過檢查接口信號的值和變化來達(dá)到驗(yàn)證設(shè)計(jì)功能的目的。這種方法的抽象層次較低,驗(yàn)證平臺的開發(fā)與DUT的接口協(xié)議緊密相關(guān),使得驗(yàn)證平臺的重用性較差。如果要做到一個(gè)驗(yàn)證平臺可以驗(yàn)證多個(gè)不同的DUT,必須將驗(yàn)證平臺的抽象層次提高到事務(wù)級,而且應(yīng)該構(gòu)建層次化的結(jié)構(gòu),層與層之間具有一定的獨(dú)立性,改變底層并不會影響上層。

基于事務(wù)的驗(yàn)證

所謂事務(wù)(Transaction)是指設(shè)計(jì)對象與事務(wù)處理器(Transactor)之間通過接口所做的一次數(shù)據(jù)傳輸。從硬件的角度來看,事務(wù)可看成作用在一個(gè)特定接口上的一組信號的集合單元。事務(wù)具有3個(gè)要素:起始時(shí)間、終止時(shí)間,以及所有與這個(gè)事務(wù)相關(guān)的信息。

基于事務(wù)的驗(yàn)證工具讓用戶除了可以在信號/引腳級上進(jìn)行驗(yàn)證,還可以在事務(wù)級上進(jìn)行驗(yàn)證,從而提高了設(shè)計(jì)生產(chǎn)率。

基于事務(wù)驗(yàn)證環(huán)境的基本要素

DUT:待驗(yàn)證設(shè)計(jì)對象的RTL描述或門級描述。

事務(wù):在DUT和事務(wù)處理器之間通過接口在特定起止時(shí)間內(nèi)的一次數(shù)據(jù)傳輸。事務(wù)能夠?qū)π盘柌ㄐ芜M(jìn)行標(biāo)識,表示相關(guān)的信號屬性,還可以標(biāo)識錯(cuò)誤。

事務(wù)處理器:也叫總線功能模型(BFM)。事物處理器可以表示事務(wù)所代表的信號變化,并與DUT通過接口進(jìn)行連接。一個(gè)典型的DUT往往具有不同的接口,因此一個(gè)驗(yàn)證環(huán)境中具有不同的事務(wù)處理器以產(chǎn)生相關(guān)的測試向量對DUT進(jìn)行激勵(lì)。

測試?yán)?Testcase):用來產(chǎn)生驗(yàn)證DUT特定功能所需要的事務(wù)。

基于事務(wù)的驗(yàn)證處理過程

測試?yán)ㄟ^特定的事務(wù)來調(diào)用事務(wù)處理器的任務(wù),事務(wù)處理器按照DUT所遵循的協(xié)議對事務(wù)進(jìn)行處理,經(jīng)過處理后的事務(wù)通過連接DUT的接口輸入到DUT中,DUT對輸入的激勵(lì)進(jìn)行響應(yīng)。DUT輸出的響應(yīng)再轉(zhuǎn)換為事務(wù)的形式,這樣驗(yàn)證平臺的自核對模塊就可以在事務(wù)級上對激勵(lì)和響應(yīng)進(jìn)行核對,以檢查DUT的功能是否正確。

RVM層次化驗(yàn)證方法學(xué)

RVM驗(yàn)證方法學(xué)是一種層次化的驗(yàn)證方法學(xué),它能把驗(yàn)證的步驟分層進(jìn)行,將驗(yàn)證工作提高到更高的抽象層次,即事務(wù)層。層次化的驗(yàn)證方法使得驗(yàn)證工程師只需關(guān)心DUT的輸入/輸出接口,而不必關(guān)心DUT內(nèi)部的具體實(shí)現(xiàn)。

根據(jù)RVM方法學(xué),驗(yàn)證工程師可以搭建出具有隨機(jī)測試、自動檢錯(cuò)核對、功能覆蓋等功能的層次化驗(yàn)證平臺。這類驗(yàn)證平臺包含很多參考模型,每個(gè)模型可完成不同的功能。在搭建驗(yàn)證平臺的過程中,還可以直接調(diào)用Synopsys提供的RVM基類庫,其中定義了豐富的標(biāo)準(zhǔn)類。利用RVM基類以及面向?qū)ο蟮募夹g(shù)可以更方便地生成驗(yàn)證平臺各個(gè)層次的模塊。

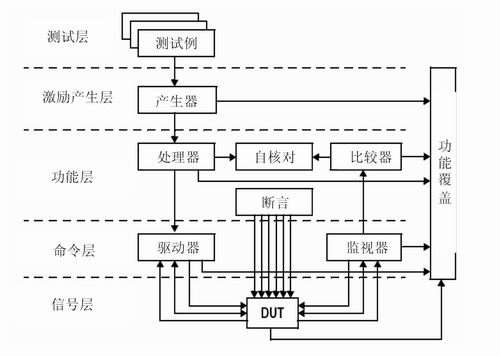

基于RVM的驗(yàn)證平臺分成5層,每層完成獨(dú)立的功能,層與層通過接口互相連接。RVM驗(yàn)證模型如圖1所示。

圖 1 RVM層次化驗(yàn)證模型

信號層

信號層提供驗(yàn)證平臺與DUT的信號級連接。驗(yàn)證平臺通過信號層將上層產(chǎn)生的激勵(lì)驅(qū)動到DUT中。具體實(shí)現(xiàn)時(shí),需要定義驗(yàn)證平臺與DUT連接的虛端口,當(dāng)DUT的接口改變時(shí),只需要修改驗(yàn)證平臺虛端口中的信號,上層模塊不需要修改,方便整個(gè)驗(yàn)證平臺的重用。

命令層

命令層將信號層的信號抽象為事務(wù),給高層提供DUT的接口與事務(wù)的轉(zhuǎn)換。命令層主要包括驅(qū)動器模塊和監(jiān)視器模塊,與上層模塊通過事務(wù)級通道連接,與下層模塊通過虛端口連接。驅(qū)動器完成對DUT激勵(lì)的驅(qū)動。監(jiān)視器檢測DUT的輸出,將輸出反饋給上層模塊。

功能層

功能層模擬DUT的基本行為,將DUT的行為抽象為更高一級的事務(wù)。功能層中包括事務(wù)處理器模塊和自核對模塊。事務(wù)處理器模塊根據(jù)DUT所遵循的協(xié)議將上層產(chǎn)生的事務(wù)進(jìn)行處理,經(jīng)過事務(wù)處理器處理的事務(wù)通過事務(wù)級通道傳給下層。自核對模塊用于對比事務(wù)經(jīng)過DUT處理之后是否符合協(xié)議的要求,通常用于檢查DUT傳輸數(shù)據(jù)的正確性。

激勵(lì)產(chǎn)生層

激勵(lì)產(chǎn)生層用于產(chǎn)生對DUT的激勵(lì)事務(wù)。這一層包括產(chǎn)生器模塊,該模塊產(chǎn)生一系列的事務(wù)對象,通過事務(wù)級通道傳輸給下層。RVM支持兩種產(chǎn)生器: Atomic產(chǎn)生器,用于產(chǎn)生一組相似的事務(wù)對象; Scenario產(chǎn)生器,用于產(chǎn)生順序可控制的事務(wù)對象。

測試層

測試層用于對DUT的邏輯功能進(jìn)行驗(yàn)證。這一層主要是用戶為了驗(yàn)證DUT的邏輯功能而編寫的不同測試?yán)跍y試?yán)锌梢詫Ω鱾€(gè)模塊的限制條件進(jìn)行修改。通過對不同測試?yán)\(yùn)行結(jié)果的統(tǒng)計(jì),可以查看DUT的功能覆蓋率,只有功能覆蓋率達(dá)到一定要求,才能夠認(rèn)為該DUT已經(jīng)被完備的驗(yàn)證通過。

SIMC模塊的功能驗(yàn)證

SIMC是SIM卡控制器的簡稱,通過SIMC可以在手機(jī)基帶處理芯片上外接SIM卡,實(shí)現(xiàn)數(shù)據(jù)的發(fā)送和接收。SIMC模塊連接在系統(tǒng)的APB總線上,ARM微控制器通過APB總線對SIMC進(jìn)行訪問。該模塊主要包括波特率產(chǎn)生部分、接收數(shù)據(jù)的串并轉(zhuǎn)換部分、發(fā)送數(shù)據(jù)的并串轉(zhuǎn)換部分、發(fā)送FIFO的控制部分、接收FIFO的控制部分等。發(fā)送數(shù)據(jù)時(shí),SIMC模塊會將發(fā)送數(shù)據(jù)寄存器的數(shù)據(jù)先放到發(fā)送FIFO中,再將FIFO中的數(shù)據(jù)發(fā)送出去;接收數(shù)據(jù)時(shí),SIMC模塊將接收到的數(shù)據(jù)放到接收FIFO中,再由處理器從接收數(shù)據(jù)寄存器中讀取數(shù)據(jù)。如果接收數(shù)據(jù)后,判斷

校驗(yàn)位或停止位出錯(cuò),則數(shù)據(jù)不會被放入接收FIFO中,SIMC模塊的狀態(tài)寄存器會有相應(yīng)的指示。

本文將以一款基帶處理芯片的SIMC為例,詳細(xì)介紹RVM驗(yàn)證方法學(xué)的應(yīng)用。其中DUT的RTL代碼用Verilog編寫,驗(yàn)證平臺的代碼用OpenVera編寫。OpenVera語言是一種新型的高階驗(yàn)證語言(HLV)。用OpenVera編寫的代碼中調(diào)用了RVM的基類和庫函數(shù),充分應(yīng)用了面向?qū)ο蠹夹g(shù)。

SIMC模塊的RVM分層驗(yàn)證平臺結(jié)構(gòu)

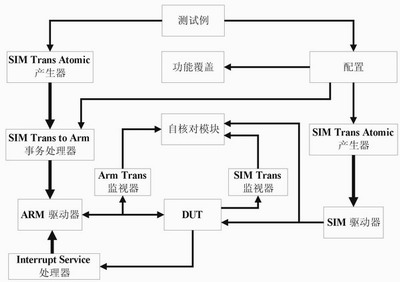

SIMC模塊的驗(yàn)證平臺利用Synopsys公司Vera驗(yàn)證工具搭建,驗(yàn)證平臺的搭建遵循RVM驗(yàn)證方法學(xué),代碼的編寫過程調(diào)用了RVM基類庫。SIMC模塊驗(yàn)證平臺結(jié)構(gòu)如圖2所示。

圖 2 SIMC模塊RVM層次化驗(yàn)證模型

信號層

信號層包括定義的虛端口,用于和SIMC模塊RTL代碼的接口相連。首先定義一個(gè)interface變量,該變量中定義的接口對應(yīng)于SIMC模塊的接口信號,interface變量的定義語句中用hdl_node關(guān)鍵字和RTL代碼的接口信號相連。定義的虛端口再和interface中的信號綁定。

命令層

命令層包括ARM端的驅(qū)動器和監(jiān)視器、SIM卡端的驅(qū)動器和監(jiān)視器。ARM端的驅(qū)動器模仿APB總線,按照協(xié)議的規(guī)定對DUT進(jìn)行驅(qū)動,SIM卡端的驅(qū)動器模仿一個(gè)SIM卡對DUT進(jìn)行驅(qū)動。兩端的監(jiān)視器檢測DUT的輸出數(shù)據(jù)和驅(qū)動到DUT中的數(shù)據(jù),將數(shù)據(jù)保存在自核對模塊中進(jìn)行比較,通過比較來檢查DUT傳輸數(shù)據(jù)是否正確。

編程實(shí)現(xiàn)時(shí),可以通過繼承RVM基類庫中的rvm_xactor類得到所需要的子類,在子類的代碼中加入需要實(shí)現(xiàn)的功能。

功能層

功能層包括將SIM卡事務(wù)轉(zhuǎn)化為ARM事務(wù)的事務(wù)處理器、實(shí)現(xiàn)中斷服務(wù)功能的事務(wù)處理器、自核對模塊。編程實(shí)現(xiàn)時(shí),事務(wù)處理器可以通過繼承RVM基類庫中的rvm_xactor得到,在子類的代碼中加入需要實(shí)現(xiàn)的功能。自核對模塊用于比較DUT的激勵(lì)和響應(yīng)是否符合要求。

激勵(lì)產(chǎn)生層

激勵(lì)產(chǎn)生層包括兩個(gè)Atomic產(chǎn)生器,兩個(gè)產(chǎn)生器是同一個(gè)類的兩個(gè)對象。產(chǎn)生器為DUT產(chǎn)生隨機(jī)激勵(lì),激勵(lì)封裝在一個(gè)事務(wù)中,通過事務(wù)通道傳到下層模塊中。兩端的產(chǎn)生器都是產(chǎn)生SIM卡事務(wù)的,ARM端有一個(gè)將SIM卡事務(wù)轉(zhuǎn)化為ARM事務(wù)的事務(wù)處理器來完成SIM卡事務(wù)向ARM事務(wù)的轉(zhuǎn)化。通過產(chǎn)生器可以隨機(jī)產(chǎn)生符合協(xié)議規(guī)范的激勵(lì)。編寫代碼時(shí),產(chǎn)生器可以通過調(diào)用RVM的宏rvm_atomic_gen很方便地實(shí)現(xiàn)。

測試層

在測試層,用戶可以編寫不同的測試?yán)龑UT的功能進(jìn)行驗(yàn)證。在測試?yán)校ㄟ^對約束的限制、環(huán)境類的例化、配置類的約束來實(shí)現(xiàn)對DUT的功能覆蓋,以達(dá)到100%的功能覆蓋率。

驗(yàn)證平臺的重用

對單個(gè)模塊驗(yàn)證完畢之后可以進(jìn)行系統(tǒng)級的驗(yàn)證。根據(jù)RVM驗(yàn)證方法學(xué)搭建的層次化驗(yàn)證平臺可以被重用到系統(tǒng)級的驗(yàn)證中。系統(tǒng)級驗(yàn)證側(cè)重于檢查各模塊間的接口和數(shù)據(jù)交互是否符合設(shè)計(jì)規(guī)范,某些模塊級驗(yàn)證的模塊可以被復(fù)用到系統(tǒng)級驗(yàn)證中。對SIMC模塊來說,系統(tǒng)級驗(yàn)證時(shí),ARM端的驅(qū)動器、監(jiān)視器以及激勵(lì)產(chǎn)生器都可以被APB總線代替,SIM卡端的各模塊可以繼續(xù)使用,達(dá)到重用的目的。

應(yīng)用RVM驗(yàn)證方法的注意事項(xiàng)與技巧

RVM驗(yàn)證方法學(xué)由Synopsys公司提出,利用RVM驗(yàn)證方法學(xué)首選的編程語言是OpenVera硬件驗(yàn)證語言。筆者在應(yīng)用RVM驗(yàn)證方法學(xué)搭建驗(yàn)證平臺過程中的一些技巧和注意事項(xiàng)歸納如下:

1、 驗(yàn)證某個(gè)模塊前,首先要閱讀相關(guān)文檔,熟悉模塊的功能特性,然后搭建驗(yàn)證平臺的基本框圖,選擇RVM的相關(guān)技術(shù),在驗(yàn)證平臺基本框圖指導(dǎo)下編程實(shí)現(xiàn)。

2、 驗(yàn)證平臺中功能覆蓋點(diǎn)的定義是驗(yàn)證成敗的關(guān)鍵,驗(yàn)證過程中利用RVM的覆蓋率驅(qū)動技術(shù),分析所定義的覆蓋點(diǎn)的覆蓋情況,改善該驗(yàn)證平臺,每個(gè)功能覆蓋點(diǎn)都必須被覆蓋到。

3、 RVM基類庫提供了豐富的函數(shù),但是Synopsys沒有開放RVM基類的源代碼,所以驗(yàn)證代碼的編寫過程中應(yīng)隨時(shí)查閱RVM文檔,盡量使用RVM基類提供的函數(shù),而不是自己去重新開發(fā)一個(gè)函數(shù)。

4、 RVM驗(yàn)證平臺中各個(gè)模塊之間通信有很多種方法,可以用RVM的callbacks類,也可以使用雙通道等。

5、 RVM為驗(yàn)證平臺中的進(jìn)程間通信提供了多種數(shù)據(jù)結(jié)構(gòu),例如semaphore、region、mailbox等,編程時(shí)應(yīng)根據(jù)需要進(jìn)行選擇。 例如,在某一時(shí)刻有多個(gè)并行的進(jìn)程對同一個(gè)信號進(jìn)行驅(qū)動,仿真工具會停止仿真并打印出錯(cuò)信息。解決的方法是應(yīng)用semaphores數(shù)據(jù)結(jié)構(gòu),每個(gè)進(jìn)程得到semaphore才可以驅(qū)動信號,對信號驅(qū)動后再釋放semaphore供其他進(jìn)程使用。

6、 如果要打

印信息,應(yīng)使用rvm_log類而不是printf()函數(shù)。rvm_log類除了將信息打印出來,還可以顯示出信息來源于驗(yàn)證平臺中的哪個(gè)模塊以及該模塊的仿真時(shí)間,便于編程人員調(diào)試代碼。

7、 隨機(jī)激勵(lì)的產(chǎn)生不是真正意義上的隨機(jī),而是一種偽隨機(jī)。編程人員在多次運(yùn)行同一個(gè)測試?yán)龝r(shí)應(yīng)改變驗(yàn)證平臺的隨機(jī)種子,可通過調(diào)用srandom()函數(shù)來實(shí)現(xiàn)。

結(jié)語

用RVM驗(yàn)證方法學(xué)搭建的層次化驗(yàn)證平臺將大大提高驗(yàn)證環(huán)境的執(zhí)行效率。RVM驗(yàn)證方法學(xué)中的隨機(jī)測試技術(shù)可以在很短的時(shí)間內(nèi)達(dá)到更高的功能覆蓋率,提高驗(yàn)證工程師的工作效率,達(dá)到有效縮短驗(yàn)證周期的目的。

參考文獻(xiàn)

1.[美]PeterPaterson.系統(tǒng)芯片(SoC)驗(yàn)證方法與技術(shù)[M].孫海平,丁健譯.北京:電子工業(yè)出版社,2005. 16~20

2.張亞楠,申敏,游敏惠.基于RVM的可重用測試方法及應(yīng)用[J].重慶郵電學(xué)院學(xué)報(bào), 2006,18(3):303~306

2.Synopsys Inc. Reference Verification Methodology User Guild.http://www.synopsys.com/