1 引言:

美國Atmel公司生產(chǎn)的AT94K系列芯片是以Atmel 0.35 的5層金屬CMOS工藝制造。它基于SRAM的FPGA、高性能準(zhǔn)外設(shè)的Atmel 8位RISC AVR單片機(jī)。另外器件中還包括擴(kuò)展數(shù)據(jù)和程序SRAM及器件控制和管理邏輯。圖1-1是Atmel公司的FPSLIC內(nèi)部結(jié)構(gòu)圖。

圖1-1 FPSLIC內(nèi)部結(jié)構(gòu)圖

AT94K內(nèi)嵌AVR內(nèi)核,Atmel公司的FPSLIC可編程SOC內(nèi)嵌高性能和低功耗的8位AVR單片機(jī),最多還帶有36KB的SRAM,2個(gè)UART、1個(gè)雙線串行接口,3個(gè)定時(shí)/計(jì)數(shù)器、1個(gè)8 8乘法器以及一個(gè)實(shí)時(shí)時(shí)鐘。通過采用單周期指令,運(yùn)算速度高達(dá)1MPS/MHz,這樣用戶可以充分優(yōu)化系統(tǒng)功耗和處理速度。AVR內(nèi)核基于增強(qiáng)型RISC結(jié)構(gòu),擁有豐富的指令系統(tǒng)以及32個(gè)通用工作寄存器。而且所有通用寄存器都與算術(shù)邏輯單元ALU相連;另外,在一個(gè)時(shí)鐘周期內(nèi),執(zhí)行單條指令時(shí)允許存取2個(gè)獨(dú)立的寄存器,這種結(jié)構(gòu)使得代碼效率更高,并且在相同的時(shí)鐘頻率下,可以獲得比傳統(tǒng)的CISC微處理器高10倍的數(shù)據(jù)吞吐量。AVR從片內(nèi)SRAM執(zhí)行程序,由于AVR運(yùn)行代碼存儲在SRAM中,因此它可以提供比較大的吞吐量,這樣可以使其工作在突發(fā)模式上。在這種模式上,AVR大多時(shí)間都是處于低功耗待機(jī)狀態(tài),并能在很短的時(shí)間里進(jìn)行高性能的處理。微處理器在突發(fā)模式運(yùn)行模式下的平均功耗要比長時(shí)間低頻率運(yùn)行時(shí)的功耗低得多。FPSLIC的待機(jī)電流小于100 ,典型的工作電流為2-3mA/MHz。在系統(tǒng)上電時(shí),F(xiàn)PGA配置SRAM和AVR程序SRAM都能自動地通過Atmel在系統(tǒng)可編程串行存貯器AT17來裝載。

2 FPSLIC硬件的設(shè)計(jì)實(shí)現(xiàn):

2.1 硬件實(shí)現(xiàn)框圖

圖2-1系統(tǒng)硬件實(shí)現(xiàn)框圖

圖2-1是為了實(shí)現(xiàn)加密算法的硬件框圖。計(jì)算機(jī)通過它的串口和FPSLIC的通信端口UART0相連,用來進(jìn)行數(shù)據(jù)的傳送和接收。FPSLIC通過AVR的通信端口等待接收主機(jī)傳來的信息,通過內(nèi)部的下載程序?qū)?shù)據(jù)進(jìn)行處理,最后再傳回到主機(jī)上。圖2-1中FPGA是一個(gè)計(jì)數(shù)器,此計(jì)數(shù)器一上電就從0計(jì)數(shù),并用進(jìn)位輸出信號產(chǎn)生一個(gè)AVR中斷,即進(jìn)位輸出信號RCO連接到AVR的中斷信號INTA0。當(dāng)AVR接收到由計(jì)數(shù)器的進(jìn)位信號產(chǎn)生的中斷時(shí),則執(zhí)行INTA0的中斷服務(wù)程序(ISR)。在此期間,AVR就給INTA0產(chǎn)生的次數(shù)計(jì)數(shù),并把它放到8位的AVR-FPGA數(shù)據(jù)總線上,這時(shí)就會觸發(fā)AVR的寫使能信號(FPGA的aWE信號端)和FPGA的I/O SELECT0信號(FPGA的LOAD信號端),同時(shí)從AVR——FPGA數(shù)據(jù)總線上將數(shù)據(jù)載入計(jì)數(shù)器。數(shù)碼管的各極連接在實(shí)驗(yàn)板上的可編程端口,通過引腳配置用來顯示數(shù)據(jù)。LED指示燈在AVR I/O輸出的D口,直接將數(shù)據(jù)通過命令PORTD來顯示。FPGA的時(shí)鐘通過GCLK5選自AVR單片機(jī)的時(shí)鐘。我們以DES數(shù)據(jù)加密為例,由仿真試驗(yàn)可以得出DES加密的速率為57.024 kbit/s,它大于串口的最大速率19.2kbit/s,因此可以實(shí)時(shí)進(jìn)行數(shù)據(jù)的加密操作。

一個(gè)典型的FPSLIC設(shè)計(jì)通常應(yīng)該包括以下幾個(gè)步驟:

1. 利用聯(lián)合仿真軟件建立一個(gè)FPSLIC工程。

2. 預(yù)先建立一個(gè)AVR軟件仿真程序文件。

3. 預(yù)先建立一個(gè)FPGA的硬件仿真程序文件。

4. 設(shè)置和運(yùn)行AVR-FPGA接口設(shè)計(jì)。

5. 運(yùn)行布局前的聯(lián)合仿真Pre-layout Converification(這一步是可選擇的)。

6. 運(yùn)行Figaro-IDS進(jìn)行FPGA的布局布線。

7. 運(yùn)行布局后的聯(lián)合仿真Pos-layout Converification(這一步是可選擇的)。

8. 器件編程數(shù)據(jù)下載與實(shí)驗(yàn)驗(yàn)證。

我們以DES數(shù)據(jù)加密為例,(新建的工程名為lab1.apj,AVR仿真程序文件為desjiami.asm,F(xiàn)PGA的硬件仿真程序?yàn)镃ount.vhdl)。

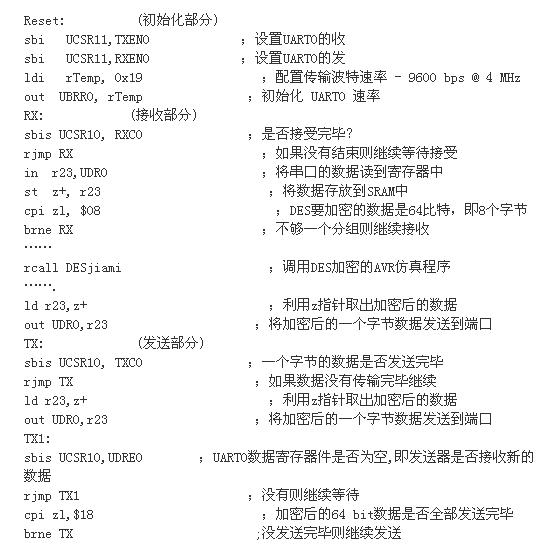

2.2 編譯AVR的仿真程序軟件

(以上程序代碼是整個(gè)仿真的程序框架,最主要的是對接口進(jìn)行初始化和對發(fā)送和接收部分進(jìn)行設(shè)置,以便進(jìn)行串口的通信)

2.3器件編程與試驗(yàn)驗(yàn)證

1. 將下載電纜ATDH2225的25針的一端從計(jì)算機(jī)的并行口接出,令一端10針扁平線插入ATSTK94實(shí)驗(yàn)板的J1插頭上。下載電纜的標(biāo)有紅色的線和J1插頭的第一腳連接。

2. 因?yàn)橐陀?jì)算機(jī)串口進(jìn)行通信,因此要制作一個(gè)串口連接電纜,其九針連接電纜的連接關(guān)系如下圖2-2。電纜一端連接在計(jì)算機(jī)的任意串口上,另一端連接在實(shí)驗(yàn)板上的UART0上。連接電纜只需要連接三根線,UART0的2端連接在FPSLIC的發(fā)送端,因此它和計(jì)算機(jī)的串口2端(接收數(shù)據(jù)端)相連。UART0的3端連接在FPSLIC的接收端,因此它和計(jì)算機(jī)的串口2端(發(fā)送數(shù)據(jù)端)相連。

圖2-2 串口通信連接指示圖

3. 選擇4MHz時(shí)鐘,即在實(shí)驗(yàn)板上將JP17設(shè)置在靠近板子內(nèi)側(cè)位置,而將JP18不連接,也就是將其連接跳線拔掉。

4. 將直流9V電源接頭插入ATSTK94實(shí)驗(yàn)板的電源插座P3上。

5. 將實(shí)驗(yàn)板上的開關(guān)SW10調(diào)至PROG位置。開關(guān)SW10有編程(PROG)和運(yùn)行(RUN)兩種連接。在編程位置,用戶可以通過下載電纜和下載程序軟件CPS,將System Designer生成的FPSLIC數(shù)據(jù)流文件給配置存儲器編程。在運(yùn)行位置,F(xiàn)PSLIC器件將載入數(shù)據(jù)流文件并運(yùn)行該設(shè)計(jì)。

6. 打開電源開關(guān)SW14,即將它調(diào)整到ON位置。這時(shí)候?qū)嶒?yàn)板上電源發(fā)光二極管(紅色)發(fā)光,表示實(shí)驗(yàn)板上已經(jīng)上電。這樣,硬件就連接完畢,等待下一步的數(shù)據(jù)下載。

7. 單擊OK按鈕,即生成數(shù)據(jù)流文件,它將下載到ATSTK94實(shí)驗(yàn)板的配置存儲器中,這時(shí),Atmel的AT17配置可編程系統(tǒng)(CPS)窗口被打開,如下圖2-3,并自動給器件編程。

圖2-3 FPSLIC控制寄存器設(shè)置對話框

在Procesure下拉列表框中選擇/P Partition,Program and Verify from an Atmel File。在Family下拉列表框中選擇AT40K/Cypress,在Device下拉列表框中選擇AT17LV010(A)(1M)。其余采用系統(tǒng)的默認(rèn)值。然后點(diǎn)擊Start Produce按鈕,如果電纜等硬件設(shè)置正確,那么程序?qū)⑾螺d到實(shí)驗(yàn)板上。

8. 將開關(guān)SW10調(diào)至RUN位置,打開串口調(diào)試程序Accesspot129軟件。對于Accessport129的設(shè)置為:串口為COM1(根據(jù)用戶選擇的計(jì)算機(jī)端口來設(shè)定),波特率:9600,校驗(yàn)位:NONE,數(shù)據(jù)位為8 ,停止位選擇1,串口開關(guān)選擇開;

3 試驗(yàn)結(jié)果:

圖3-1中,下面方框中是要輸入的64比特的明文,(程序中輸入的明文為0123456789ABCDEF),當(dāng)這64個(gè)比特的數(shù)據(jù)全部輸入完畢后,點(diǎn)擊發(fā)送按鈕,在軟件上方的數(shù)據(jù)接收端顯示出經(jīng)過DES算法加密后的密文(85E813540F0AB405)。通過硬件實(shí)現(xiàn)的的結(jié)果和實(shí)際仿真結(jié)果是完全一致的。同時(shí)通過數(shù)碼管也分別顯示出最后的加密數(shù)據(jù)。至此整個(gè)硬件試驗(yàn)結(jié)束。

圖3-1 Accesspot串口調(diào)試軟件顯示的結(jié)果圖

從上面的串口調(diào)試軟件可以看出,DES算法的仿真是正確的也是可以在實(shí)際中應(yīng)用的。同理,可以通過以上的方法來實(shí)現(xiàn)DES解密和AES等其它的分組加解密。