摘 要: 介紹了一種基于PC+ARM+DSP+DDS體系結(jié)構(gòu)的通用雷達中頻信號模擬器。該系統(tǒng)能夠模擬多種體制的雷達中頻信號,而且不同信號間切換方便、使用靈活。介紹了該系統(tǒng)的硬件設(shè)計和在模擬相參脈沖雷達動目標信號中的應(yīng)用。

關(guān)鍵詞: 雷達中頻信號模擬器 AD9852 TMS320C6416 S3C44B0X 相參

雷達信號模擬器是模擬技術(shù)與雷達技術(shù)相結(jié)合的產(chǎn)物。它通過模擬的方法產(chǎn)生雷達回波信號, 以便在實際雷達系統(tǒng)前端不具備的條件下對雷達系統(tǒng)后級進行調(diào)試[1]。隨著數(shù)字技術(shù)的進步,高速、超大規(guī)模集成電路的使用,雷達信號模擬系統(tǒng)正朝著靈活、通用的方向發(fā)展。筆者設(shè)計了一種基于PC+ARM+DSP+DDS體系結(jié)構(gòu)的通用雷達中頻信號模擬器,介紹了該系統(tǒng)的硬件設(shè)計,并以模擬相參脈沖雷達動目標信號為例,介紹了本系統(tǒng)的應(yīng)用。

1 系統(tǒng)結(jié)構(gòu)設(shè)計

現(xiàn)代雷達信號模擬器的設(shè)計偏重于運用數(shù)字化方式實現(xiàn),隨著實時數(shù)字信號處理技術(shù)的發(fā)展,PC+DSP+D/A的體系結(jié)構(gòu)成為雷達模擬器實現(xiàn)的主要方式。直接數(shù)字頻率合成技術(shù)(DDS)以其在頻率捷變速度、相位連續(xù)性、相對帶寬、高分辨率以及集成化等方面的優(yōu)異性能,成為現(xiàn)代頻率合成技術(shù)中的佼佼者,同時也為雷達中頻信號模擬的實現(xiàn)方式提供了新的選擇[2]。

本設(shè)計采用PC+ARM+DSP+DDS的體系結(jié)構(gòu)。PC機對目標及環(huán)境進行建模、運算,生成雷達中頻信號仿真數(shù)據(jù)庫,DSP根據(jù)模擬的雷達實時狀態(tài)及目標、環(huán)境的實時特性,進行數(shù)據(jù)調(diào)度、運算和處理,最后形成控制DDS所需的調(diào)幅、調(diào)相、調(diào)頻等控制字,通過DDS產(chǎn)生雷達中頻模擬信號。

出于對模擬器通用性的考慮,PC機與DSP間的通信,希望不僅能實時改變雷達模擬信號的參數(shù),還可以適應(yīng)不同雷達體制和不同信號處理機的具體要求,方便加載新的程序。雖然通過PCI(或CPCI)能實現(xiàn)程序加載,并且傳輸速率快,但不能脫機工作,且插拔麻煩,不能用于筆記本調(diào)試。本設(shè)計采用ARM作為主控模塊,控制USB接口器件和DSP的主機口,完成程序的加載和參數(shù)的實時設(shè)置。

2 硬件電路的設(shè)計與實現(xiàn)

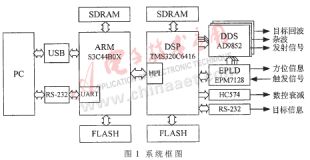

本系統(tǒng)主要包括以ARM為核心的主控模塊,以DSP為核心的實時數(shù)據(jù)處理模塊,以DDS為核心的信號生成模塊,以及包括USB、RS-232和鎖存器等的通信模塊和電源系統(tǒng),其系統(tǒng)框圖如圖1所示。

2.1 主控模塊

系統(tǒng)主控模塊負責控制和協(xié)調(diào)各種工作。ARM采用Samsung公司生產(chǎn)的S3C44B0X微處理器,通過集成鎖相環(huán)倍頻系統(tǒng)主頻可達66MHz,最大外部存儲空間256MB,片上資源豐富,外圍控制能力強,性價比高[3]。由它控制USB模塊接收PC機計算生成的雷達模擬信號的數(shù)據(jù)及代碼,控制主機口加載DSP,控制UART實現(xiàn)工作狀態(tài)在PC機上的實時顯示。

2.2 實時數(shù)據(jù)處理模塊

實時數(shù)據(jù)處理模塊利用PC機生成的雷達信號模擬數(shù)據(jù),根據(jù)設(shè)定的雷達工作狀態(tài)及目標、環(huán)境的實時動態(tài)計算DDS的控制字,控制三片DDS輸出雷達模擬信號。同時通過串口與信號處理機交換信息,通過鎖存器向處理板提供數(shù)控衰減控制信號。

DSP采用TI公司C6000系列中的TMS320C6416,系統(tǒng)時鐘達600MHz,數(shù)據(jù)處理速率可達4800MIPS。提供32/16bit主機口,具有兩個獨立的外部存儲器接口,其中EMIFA支持64bit總線寬度[4]。

2.3 信號生成模塊

DDS信號產(chǎn)生模塊采用三片ADI公司生產(chǎn)的AD9852ASQ,它們同時生成三路中頻信號。根據(jù)雷達體制和信號處理機要求不同,可分別對應(yīng)不同的信號,如雷達的目標回波、雜波和發(fā)射信號,或外輻射源雷達的直達波、目標回波和多徑信號,以及跟蹤雷達回波信號的和支路Σ、俯仰差支路△α以及方位差支路△β等。

AD9852最高工作頻率300MHz,可工作在單頻、FSK、Ramped FSK、Chirp、BPSK五種模式。具有豐富的寄存器組,通過設(shè)置相應(yīng)控制字可方便生成多種信號[5]。

2.3.1 總線及時序控制設(shè)計

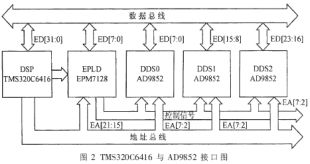

AD9852的頻率、相位和幅度控制字的設(shè)置和控制信號的產(chǎn)生由TMS320C6416完成,AD9852可以看作是異步存儲設(shè)備與TMS320C6416的EMIFA相連,EMIFA采用32bit總線。

AD9852采用并行輸入,總線寬度為8位,數(shù)據(jù)傳輸速率可達100MHz。為了提高控制DDS的速度,本系統(tǒng)采用了地址總線復用、數(shù)據(jù)總線“分裂”的技術(shù)。即三片AD9852的6位地址線同時占用TMS320C6416地址總線A2~A7位,而它們的數(shù)據(jù)線分別占用TMS320C6416數(shù)據(jù)總線的D0~D7、D8~D15和D16~D23位。這樣可以由DSP對三片DDS的I/O緩沖寄存器同時進行寫操作,提高了總線利用率,并保證了三片AD9852輸出信號的相位相參。TMS320C6416與AD9852接口示意圖如圖2所示。

三片AD9852的控制時序信號由EPLD產(chǎn)生。本設(shè)計采用ALTERRA公司生產(chǎn)的可編程邏輯器件EPM7128AETC100,對TMS320C6416的高位地址信號、數(shù)據(jù)信號和控制信號進行編碼,產(chǎn)生三片AD9852全局復位、讀/寫使能、頻率或相位切換等控制信號。

寫入AD9852的數(shù)據(jù)先存入I/O緩存器,在I/O更新信號到來時寫入相應(yīng)的寄存器改變AD9852的工作狀態(tài)。本設(shè)計中,I/O更新信號既可以由DSP寫完控制字后產(chǎn)生,也可由EPLD將系統(tǒng)時鐘分頻定時產(chǎn)生,兩種方式的選擇以及分頻倍數(shù)的控制同樣由EPLD對TMS320C6416的信號編碼實現(xiàn)。

2.3.2 時鐘設(shè)計

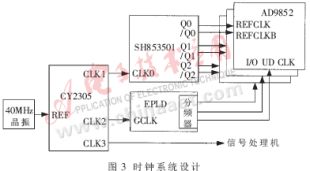

DDS輸出的信號的頻譜特性在很大程度上取決于參考時鐘的頻譜特性,參考時鐘的一些主要特性如相位噪聲、時鐘抖動以及頻率穩(wěn)定度都直接地反映在DDS的輸出信號上。DDS的時鐘電路能否設(shè)計達到高穩(wěn)定、低噪聲、精確同步直接影響本系統(tǒng)性能的優(yōu)劣。AD9852的參考時鐘可以采用單端輸入或差分輸入,由于差分信號可以有效抑制共模噪聲和電磁能量外泄,根據(jù)AD9852對峰峰值的要求(>400mV),本設(shè)計采用差分LVPECL邏輯。

本模塊采用40MHz的晶振,經(jīng)緩沖器CY2305輸出三路同步時鐘,如圖3所示。其中一路接SH853501,將一路LVCMOS時鐘變成三路差分LVPECL時鐘后,分別傳送給三片AD9852,經(jīng)片上鎖相環(huán)倍頻形成DDS的系統(tǒng)時鐘;一路給時序控制模塊EPLD,將時鐘信號分頻后產(chǎn)生三片AD9852的I/O更新時鐘;另一路作為同步時鐘供給信號處理機。

2.4 通信模塊

雷達模擬器與PC機間采用USB通信協(xié)議,由S3C44B0X控制USB接口器件ISP1581實現(xiàn)。DSP可以通過控制EPLD給信號處理機發(fā)送目標角度信息,也可以利用多通道緩沖串口向處理機傳送目標信息。本系統(tǒng)提供了衰減控制接口,由DSP產(chǎn)生相應(yīng)的衰減控制字,傳給鎖存器SN74LVC574,控制處理機上的數(shù)控衰減器。

3 相參脈沖雷達動目標信號的模擬

本系統(tǒng)中的三片DDS以及控制刷新和工作時序的EPLD采用同一個時鐘源,并向信號處理機提供同步時鐘輸出,因此應(yīng)用本系統(tǒng)可設(shè)計中頻相參雷達信號的模擬。

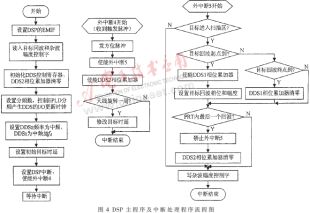

本設(shè)計中,信號處理機利用信號模擬器輸出的同步時鐘,將其分頻生成觸發(fā)脈沖,送給模擬器DSP的外中斷源4,觸發(fā)脈沖的周期對應(yīng)雷達信號的PRT(脈沖重復周期)。EPLD分頻時鐘的周期對應(yīng)雷達脈沖信號的脈寬,該信號提供AD9852的I/O更新時鐘,同時接DSP的外中斷源5。使用兩路DDS。DDS1模擬動目標回波,DDS2模擬雜波信號。

在PC機上,根據(jù)要模擬的目標及環(huán)境特性,通過建立相應(yīng)模型,計算生成目標回波及雜波的幅度控制字存儲。DSP主程序首先將這些數(shù)據(jù)讀入SDRAM。在設(shè)定的目標角度范圍內(nèi),每次接收到觸發(fā)信號,經(jīng)由目標距離決定的延時,DSP中斷產(chǎn)生一個目標回波信號。信號的頻率和相位包含目標運動的多普勒頻率信息,幅值從SDRAM讀入;雜波采用DDS2連續(xù)輸出產(chǎn)生,每隔一個脈沖持續(xù)時間DSP進入一次中斷,讀取SDRAM改變雜波的幅值。DSP主程序及中斷處理程序流程如圖4所示。

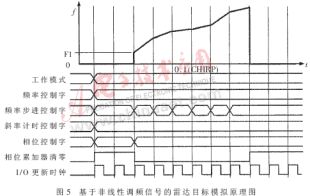

以上模擬過程采用的雷達信號為簡單矩形脈沖,脈寬等于DDS更新信號的周期。如果采用大脈寬,在脈寬內(nèi)每個DDS更新時鐘到來時,按照巴克碼或M序列改變信號的相位,可模擬相位編碼脈沖壓縮信號。當AD9852工作在CHIRP模式下,通過設(shè)置頻率步進步長和斜率計時(即變化的頻率在每個頻率點上停留的時間)控制字,可模擬線形調(diào)頻脈沖壓縮信號。在同一模式下,若在脈寬內(nèi)每個DDS更新時鐘到來時改變頻率步進步長或斜率計時控制字,可模擬非線性調(diào)頻脈沖壓縮信號,其原理如圖5所示。

本設(shè)計主要具有以下特點:

(1)利用AD9852的多種工作模式,可方便產(chǎn)生多種雷達信號,而且頻率捷變速度快,捷變時相位連續(xù),頻率分辨率高達10-6Hz。

(2)通過TMS320C6416同時控制三片DDS,讀寫速度快,保證了實時性和輸出信號相位相參性。

(3)通過ARM控制USB模塊和DSP主機口,可實時修改信號參數(shù)和加載新的程序及數(shù)據(jù)。

(4)采用三路DDS,并提供同步時鐘輸出,為適應(yīng)不同體制雷達的要求提供了保證,更具通用性。

實驗和應(yīng)用結(jié)果表明,該系統(tǒng)能夠模擬多種體制的雷達中頻信號,而且不同信號間切換方便,使用靈活。該系統(tǒng)為雷達中頻信號模擬提供了一個通用的硬件平臺。在此基礎(chǔ)上,通過豐富和完善軟件數(shù)據(jù)庫,可建成通用雷達中頻信號模擬系統(tǒng)。

參考文獻

1 R.L.米切爾著,陳訓達譯.雷達系統(tǒng)模擬[M].北京:科學出版社, 1982

2費元春,蘇廣川.寬帶雷達信號產(chǎn)生技術(shù)[M].北京:國防工業(yè)出版社,2002

3 S3C44B0X RISC MICROPROCESSOR.SAMAUNG Electronics.2000

4 TMS320C6416 FIXED-POINT DIGITAL SIGNAL PROCES-SOR. Texas Instruments Inc. 2004

5 CMOS 300 MSPS Complete-DDS. Analog Devices Inc.1999