摘 要: FPGA的內(nèi)嵌RocketIO模塊在實(shí)際應(yīng)用中需要解決時(shí)鐘不穩(wěn)及通道綁定" title="綁定">綁定同步等問題。通過精心設(shè)計(jì)DCM單元保證了RocketIO內(nèi)部時(shí)鐘的精確。同時(shí),針對(duì)通道不同步的問題,設(shè)計(jì)了一種彈性存儲(chǔ)器方案,很好地解決了通道同步接收問題。該方案在863重大課題“可擴(kuò)展到T比特的高性能IPv4/v6路由器基礎(chǔ)平臺(tái)及實(shí)驗(yàn)系統(tǒng)”中得到了驗(yàn)證。

關(guān)鍵詞: 同步 彈性存儲(chǔ)器

隨著線路傳輸技術(shù)的迅速發(fā)展,出現(xiàn)了10Gbps的鏈路接口類型,如10Gbps的POS、WAN、LAN等。863重大課題“可擴(kuò)展到T比特的IPv4/v6路由器基礎(chǔ)平臺(tái)及實(shí)驗(yàn)系統(tǒng)”要求T比特路由器支持10G的線卡。

傳統(tǒng)的單端互連方式在傳輸速率上(最高250Mbps)已無法滿足要求。而差分" title="差分">差分串行方式(如LVDS、LVPECL等),雖然采用源同步時(shí)鐘,但數(shù)據(jù)和時(shí)鐘分別發(fā)送,受信號(hào)瞬時(shí)抖動(dòng)的影響,破壞了數(shù)據(jù)與時(shí)鐘的定時(shí)關(guān)系,傳輸速率也存在一定的瓶頸。XILINX的Virtex-ⅡPRO 系列提供了內(nèi)嵌RocketIO模塊,通過采用CDR、8B/10B編碼,預(yù)加重等可在線配置技術(shù),減少了信號(hào)衰減和線路噪聲的影響,所提供的全雙工高速通道最高支持3.125Gbps。

但在高速環(huán)境下,RocketIO易出現(xiàn)時(shí)鐘漂移,同時(shí),在進(jìn)行通道綁定時(shí),也易出現(xiàn)通道間不同步的問題。針對(duì)時(shí)鐘不穩(wěn)的現(xiàn)象,筆者利用FPGA 的數(shù)字時(shí)鐘管理器(DCM)對(duì)RocketIO的時(shí)鐘進(jìn)行精心設(shè)計(jì); 對(duì)通道不同步問題,設(shè)計(jì)了一種稱為“彈性存儲(chǔ)器”的改進(jìn)方案。經(jīng)工程驗(yàn)證,本設(shè)計(jì)方案有效地解決了以上兩個(gè)問題。

1 RocketIO的特性

如圖1,RocketIO(也稱MGT)由物理媒質(zhì)適配層(PMA)和物理編碼子層(PCS)兩部分組成。PCS主要包括發(fā)送FIFO、8B/10B編碼器、8B/10B解碼器、CRC生成與校驗(yàn),通路綁定與時(shí)鐘修正的Elastic Buffer等。PMA包括串/并轉(zhuǎn)換器、差分接收器、發(fā)送時(shí)鐘生成電路、接收時(shí)鐘恢復(fù)電路等。

以轉(zhuǎn)發(fā)引擎選取的XC2VP70 FF1704系列為例,該芯片最多可提供40路高速收發(fā)器,每路可提供最高3.125Gbps的全雙工帶寬,可支持FibreChannel、Ethernet、Custom、XAUI、Infiniband等高速通信標(biāo)準(zhǔn)。其優(yōu)點(diǎn)有:(1)每個(gè)通道支持最高125Gbps的全雙工速率; (2)支持直流和交流耦合方式; (3)可編程差分終端電阻(50Ω、70Ω);(4)輸出預(yù)加重處理。

2 時(shí)鐘及復(fù)位

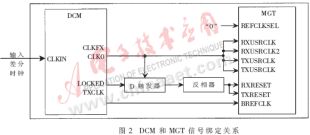

考慮到RocketIO的設(shè)計(jì)傳輸帶寬是10Gbps,RocketIO的參考時(shí)鐘選用差分輸入時(shí)鐘,這樣可極大地降低時(shí)鐘抖動(dòng)。同時(shí),利用FPGA內(nèi)部的DCM(數(shù)字時(shí)鐘管理器)產(chǎn)生Rocket IO的主時(shí)鐘,根據(jù)MGT設(shè)計(jì)的四通道綁定,分別送給RXUSRCLK、RXUSRCLK2、TXUSRCLK和TXUSRCLK2。

同時(shí),由于DCM的輸出時(shí)鐘在LOCKED指示信號(hào)無效之前處于非穩(wěn)態(tài),不適合直接作后級(jí)邏輯的參考時(shí)鐘。所以,選擇LOCKED作RocketIO的復(fù)位信號(hào)TX_RESET和RX_RESET,保證了DCM的輸出時(shí)鐘在RocketIO復(fù)位之后才送給下一級(jí)邏輯。如再加一級(jí)緩沖,保證RocketIO足夠的復(fù)位時(shí)間,效果更好。

DCM和MGT控制信號(hào)的對(duì)應(yīng)關(guān)系,如圖2所示。

3 通道綁定

理論上,經(jīng)MGT內(nèi)部緩沖處理及時(shí)鐘修正,各個(gè)例化模塊應(yīng)嚴(yán)格同步輸出。但由于硬件高頻時(shí)鐘電路" title="時(shí)鐘電路">時(shí)鐘電路的不穩(wěn)定及時(shí)鐘漂移等不確定因素,在實(shí)際工程應(yīng)用" title="工程應(yīng)用">工程應(yīng)用中經(jīng)常發(fā)生格式錯(cuò)位、通道之間不同步的現(xiàn)象,導(dǎo)致無法進(jìn)行通道綁定。

3.1 錯(cuò)誤情況分析

圖3給出了高速通道的幾種錯(cuò)誤情況。

K碼指示規(guī)則是:當(dāng)K碼依次為“10”、“00”、“01”時(shí),對(duì)應(yīng)數(shù)據(jù)包的包頭(數(shù)據(jù)為“BC95”)、正常數(shù)據(jù)報(bào)文、包尾(數(shù)據(jù)為“3CFB”); K碼為“11”時(shí),表示通道空閑(數(shù)據(jù)為“95FB”)。

圖3(a)中,序列DATA1為正確的接收序列,DATA2、DATA3均為錯(cuò)誤序列。

(1)DATA2:發(fā)生了前后兩字節(jié)錯(cuò)位的現(xiàn)象,數(shù)據(jù)格式不正確;

(2)DATA3:在時(shí)序上與DATA1不同步,但數(shù)據(jù)格式是正確的。

對(duì)于錯(cuò)位接收的原因分析,也可以從圖3(b)看出。對(duì)串行輸入的數(shù)據(jù),串并轉(zhuǎn)換之前的正確接收采樣操作應(yīng)該是采樣時(shí)鐘(RxClock)一次性采集到數(shù)據(jù)“b1b2b3b4”。但實(shí)際上,由于采用時(shí)鐘的不穩(wěn)定及高頻環(huán)境的影響,一次采樣操作卻采集到了數(shù)據(jù)“b1c2b3c4”。

3.2 彈性存儲(chǔ)器方案

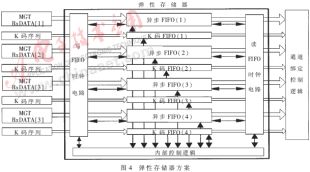

基于以上分析,在進(jìn)行通道綁定之前,筆者引入了一種彈性存儲(chǔ)器的方案(以四通道綁定為例),按照先緩存、后控制輸出的思路,實(shí)現(xiàn)對(duì)高速通道的糾錯(cuò)。彈性存儲(chǔ)器由異步FIFO(4個(gè))、時(shí)鐘電路(寫FIFO 時(shí)鐘電路,讀FIFO時(shí)鐘電路)、內(nèi)部控制邏輯" title="控制邏輯">控制邏輯三部分組成,如圖4所示。

(1)寫FIFO 時(shí)鐘電路

異步FIFO的寫時(shí)鐘產(chǎn)生電路。與內(nèi)部控制邏輯模塊配合,控制異步FIFO的數(shù)據(jù)接收及K碼序列的緩存。

對(duì)于此時(shí)的輸入數(shù)據(jù),不必考慮格式和數(shù)據(jù)的同步問題。

(2)讀FIFO 時(shí)鐘電路

4個(gè)異步FIFO及K碼FIFO的讀時(shí)鐘產(chǎn)生電路。與內(nèi)部控制邏輯模塊配合,控制4個(gè)異步FIFO及K碼序列的同步輸出。

(3)內(nèi)部控制邏輯

除了配合讀/寫時(shí)鐘電路來控制異步FIFO的讀寫,依據(jù)K碼序列對(duì)每個(gè)數(shù)據(jù)FIFO的接收數(shù)據(jù)進(jìn)行整包檢測(cè)。

具體判斷依據(jù)是根據(jù)K碼“01”表示的包尾,判定FIFO接收到了一個(gè)整包。

4個(gè)FIFO都有一個(gè)完整包時(shí),通過讀FIFO時(shí)鐘電路控制4個(gè)異步FIFO 的同步輸出,完成隨后的通道綁定。

可以看出,整個(gè)設(shè)計(jì)的關(guān)鍵在于對(duì)同步輸出時(shí)刻的把握。實(shí)現(xiàn)的重點(diǎn)在于內(nèi)部控制邏輯的整包檢測(cè)操作上。由于4個(gè)FIFO的整包檢測(cè)獨(dú)立進(jìn)行,這需要在實(shí)際編程實(shí)現(xiàn)時(shí)精心設(shè)計(jì)時(shí)序及對(duì)容錯(cuò)情況的考慮。

4 工程實(shí)現(xiàn)

圖5給出了在863課題“T比特路由器”中,基于XILINX的VIRTEXⅡPRO系列的XC2VP70芯片,采用彈性存儲(chǔ)器方案得到的MGT測(cè)試數(shù)據(jù)。

4.1軟件仿真

根據(jù)K碼序列指示,方案在時(shí)序上準(zhǔn)確實(shí)現(xiàn)了4個(gè)通道的數(shù)據(jù)對(duì)齊輸出,無通道錯(cuò)位或不同步現(xiàn)象。

4.2 工程應(yīng)用

(1)測(cè)試環(huán)境

利用光電轉(zhuǎn)換小板構(gòu)成環(huán)路,測(cè)試報(bào)文的處理流程為:CPU→FPGA→光模塊→光電轉(zhuǎn)換小板→GIGA→FPGA→CPU。如圖6所示。

(2)測(cè)試結(jié)果

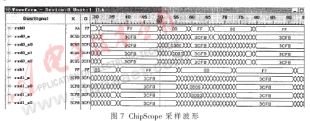

圖7為Virtex ⅡPRO-XC2VP70上實(shí)現(xiàn)兩平面接收、四通道綁定的ChipScope采樣波形。

rxk0、rxk1表示兩個(gè)平面的K碼序列。由K碼與通道的對(duì)應(yīng)關(guān)系得知,K碼為“AA”(即二進(jìn)制“10101010”),對(duì)應(yīng)數(shù)據(jù)包頭(BC95);K碼為“FF”(即二進(jìn)制“11111111”),對(duì)應(yīng)包尾(3CFB)。

由圖7知,彈性存儲(chǔ)器方案有效解決了MGT的數(shù)據(jù)同步問題。

RocketIO的難點(diǎn)在于它的鏈路層本質(zhì)及高速傳輸環(huán)境。其靈活的配置方式同時(shí)也增加了工程應(yīng)用上的難點(diǎn)。本文針對(duì)時(shí)鐘部分及通道綁定問題,提出了一種切實(shí)可行的解決方案,并得到了工程驗(yàn)證。

參考文獻(xiàn)

1 Howard Johnson, Martin Graham.High-Speed Digital Design. A Handbook of Black Magic.北京:電子工業(yè)出版社,2004.5

3 Xilinx Corporation. RocketIO Transceiver User Guide.2004.6