0 引 言

在現(xiàn)代雷達數(shù)據(jù)處理系統(tǒng)和其他應用系統(tǒng)中,傳統(tǒng)的ISA、EISA等總線已逐漸無法適應高速數(shù)據(jù)傳輸?shù)囊蟆6鳳CI局部總線以其高性能、低成本、使用方便和適應性等優(yōu)點成為大多數(shù)系統(tǒng)的主流總線。其中常用的33 MHz、32位的PCI總線尖峰傳輸速率為132 MB/s。PCI總線接口相對其他總線接口來說是比較復雜的,它有著嚴格的同步時序要求,且為了實現(xiàn)即插即用和自動配置,PCI總線的配置空間有許多配置寄存器需要設置。本文在簡要介紹PCI總線及其特點的基礎上,介紹了如何利用FPGA設計PCI總線的接口電路,并給出了設計PCI總線接口時應注意的一些問題。

1 PCI總線與數(shù)據(jù)傳輸規(guī)范

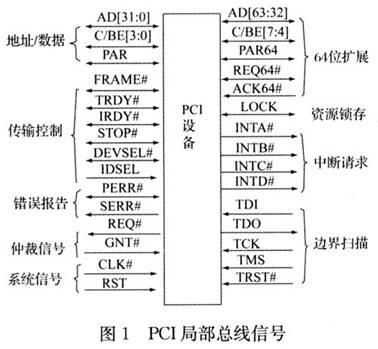

PCI總線信號可劃分為如圖1所示的幾種類型。其中64位總線擴展信號、資源鎖存信號和邊界掃描信號是可選的。

PCI總線上的數(shù)據(jù)傳送是基于猝發(fā)傳送的機制,一個猝發(fā)傳送包括一個地址相和一個或多個數(shù)據(jù)相。基本的PCI傳輸由FRAME#、IRDY#和TRDY#信號控制。當數(shù)據(jù)有效時,數(shù)據(jù)資源需要無條件設置xRDY#信號(寫操作為IRDY#,讀操作為TRDY#)。接收方可在適當時間發(fā)出它的xRDY#信號。FRAME#信號有效后的第一個時鐘上升沿是地址周期的開始,此時傳送地址信息和總線命令。下一個時鐘上升沿開始一個(或多個)數(shù)據(jù)周期,當IRDY#和TRDY#同時有效時,數(shù)據(jù)在主、從設備之間傳送。在此期間,可由主設備或從設備分別利用IRDY#和TRDY#的無效而插入等待周期。PCI總線傳輸包含讀、寫和中止3個內(nèi)容,圖2和圖3所示的時序圖顯示了PCI總線讀、寫操作的傳輸過程。

2 設計考慮及芯片選擇

目前PCI接口主要有2種實現(xiàn)方式:使用專用接口芯片和采用可編程器件。專用芯片如PLX公司的9050等,專用芯片可以實現(xiàn)完整的PCI主控模塊和目標模塊接口功能,將復雜的PCI總線接口轉換為相對簡單的用戶接口。缺點是缺少靈活性,用戶可能只用到了部分的PCI接口功能,造成了一定的邏輯資源浪費。采用FPGA的優(yōu)點在于其靈活的可編程性,首先PCI接口可以依據(jù)插卡功能進行最優(yōu)化設計,而不必實現(xiàn)所有的PCI功能,可以節(jié)約系統(tǒng)的邏輯資源。其次可以將PCI插卡上的其他用戶邏輯與PCI接口邏輯集成在一個芯片上,實現(xiàn)緊湊設計。再者當系統(tǒng)升級時,只需對可編程器件重新進行邏輯設計,而無需更新PCB版圖。

PCI總線是同步總線,時序要求比較嚴格,比如:Tval最大為11 ns,Tprop最大為10 ns,Tsu最小為7 ns,Th為0 ns,此外,PCI總線接口還需要一定數(shù)量的宏單元和I/0引腳。在本設計中,為了同時實現(xiàn)光纖數(shù)據(jù)傳輸?shù)绕渌倪壿嫻δ埽x用了ALTERA公司StratixIIGX系列中型號為EP2SGX90EF1152的一款FPGA芯片。該芯片主要性能如下:片內(nèi)90 960個邏輯單元;4.5 Mb的RAM資源;支持12路高速串行收發(fā)器通道,每路傳輸速率高達6.375 Gb/s;接口電平支持:LVTTL、LVDS、LVPECL。3.3-V PCI等眾多I/O標準。EP2SGX系列芯片內(nèi)部有專門支持PCI電氣特性的區(qū)域(Bank),非常適合于PCI接口的開發(fā)。

3 PCI接口設計實現(xiàn)

本設計利用ALTERA公司的QuartusIl7.2軟件和硬件描述語言,采用自頂向下的設計方法進行PCI接口的邏輯設計,并利用QuartusII軟件對設計進行了功能和時序仿真。

設計的具體流程如下:首先從總體上考慮:PCI接口作為一個功能模塊,嵌入在FPGA內(nèi)部,內(nèi)側面向用戶邏輯,外側通過芯片的I/O管腳與PCI總線相連。在用戶端,需要把復雜的PCI總線命令轉換為便于用戶使用的類似ISA總線的命令格式,把地址線與數(shù)據(jù)線分離,并產(chǎn)生單獨的讀寫控制信號。其次,根據(jù)總體要求,進行頂層設計和內(nèi)部模塊劃分。最后,對具體的功能模塊用軟件編程實現(xiàn)并進行功能仿真。

本設計中PCI接口的總體框圖如圖4所示。由圖4可知,PCI接口主要由地址/命令鎖存和譯碼、內(nèi)部通信、外部通信和總線狀態(tài)機、中斷處理等模塊組成。

3.1 地址/命令鎖存和譯碼

由于PCI總線為地址和數(shù)據(jù)復用型總線,在使用中需將地址和數(shù)據(jù)進行分離,首先要對PCI總線上的32位地址/數(shù)據(jù)總線鎖存。譯碼是對來自主機的PCI總線命令信號CBE[3..0]和IDSEL信號進行識別,并相應地向內(nèi)部邏輯發(fā)出配置空間讀寫操作、I/O讀寫操作、存儲器讀寫操作等信號。

3.2 外部通信

外部通信接口主要完成對PCI總線的應答,并發(fā)出相應的信號。對于瀆寫操作,接口發(fā)出DEVSEL#信號響應PCI的FRAME#信號,完成握手。PCI協(xié)議規(guī)定了在交易期間對地址/數(shù)據(jù)總線和命令/字節(jié)使能總線進行奇偶校驗。讀交易期間,接口被要求驅(qū)動PAR信號線;寫交易期間,目標將計算AD[31..0]和CBE[3..0]上的奇偶性,并把PERR信號送給PCI。

3.3 內(nèi)部通信

內(nèi)部通信接口主要產(chǎn),豐面向用戶端,便于用戶使用的一信號,包括復位信號、分離的讀和寫信號、地址總線、32位的數(shù)據(jù)讀寫總線。

3.4 總線狀態(tài)機

該模塊足本設計的關鍵部分,其主要功能是根據(jù)PCI協(xié)議產(chǎn)生總時序來控制總線交易。總線狀態(tài)機包含的狀態(tài)主要有總線空閑狀態(tài)、總線停靠狀態(tài)、主設備數(shù)據(jù)傳輸狀態(tài)、從設備數(shù)據(jù)傳輸狀態(tài)、配置空間讀寫狀態(tài)、目標I/O空間讀寫狀態(tài)、主設備讀寫狀態(tài)、總線翻轉狀態(tài)、數(shù)據(jù)傳輸終止狀態(tài)等。以上各狀態(tài)主要依據(jù)輸入的PCIRST、FRAME#、IDSEL、CBE [3..0 ]、GNT#、IRDY#、TRDY#、STOP#等信號變化進行狀態(tài)轉換。

3.5 中斷處理

本模塊主要實現(xiàn)各種外部中斷源的輸入處理、中斷允許寄存器和中斷狀態(tài)寄存器的控制和管理、INTA#信號的輸出處理等。

4 工具軟件在PCI總線調(diào)試中的使用

在板卡的調(diào)試過程中使用了WinDriver軟件,該軟件是美國Jungo公司出品用于編寫驅(qū)動程序的一種工具,是主要針對PCI、ISA、USB的一種開發(fā)工具。該軟件對于調(diào)試PCI板卡很方便。用戶不需要復雜的編程就能控制PCI沒備進行讀寫操作,從而在硬件剛設計調(diào)試時,就能測試板卡性能的好壞,可測試的功能具體包括VenderID、Device ID的識別、基地址的分配、中斷的分配、I/O端口的讀寫測試等。

另外,在調(diào)試過程中還利用了Quartus軟件自帶的SignalTap嵌入式邏輯分析儀軟件。該工具軟件只需要通過編程電纜將JTAG口與調(diào)試計算機連接后,便可在線采集各種信號波形,驗證邏輯設計是否正確。

5 PCI接口板卡設計體會

設計的CPCI板卡經(jīng)過多次試驗和測試,驗證了配置空間訪問、I/O空間訪問、外部中斷等功能均正確。目前已經(jīng)成功應用于產(chǎn)品中,下面簡要介紹設計開發(fā)過程中的一些體會。

(1)PCI接口在板卡設計中需注意的問題

①板卡上的一些信號都必須在靠近連接器J1的地方串行放置阻值為10 Ω的終端電阻。必須端接電阻的信號有:AD[31:0]、C/BE[3:0]、PAR、FRAME#、IRDY#、TRDY#、STOP#、LOCK#、IDSEL#、DEVSEL#、PERR#、SERR#、RST#、INTA#。電阻應放置在距PCI信號連接器引腳15.2 mm以內(nèi),以減少信號經(jīng)過板卡端接后對背板的影響。不需要使用終端電阻的信號有:CLK,REQ#和GNT#。在實際設計中,必須按以上要求將信號進行端接處理,否則PCI總線會工作不正常。

②從連接器J1到端接電阻的信號線的長度不應超過15.2 mm。

③從連接器兒經(jīng)端接電阻到FPGA的信號線的長度不應超過38.1 mm。

(2)配置空間的簡化設計

PCI總線的配置空間為2,56個字節(jié)。在設計中,只需對用到的參數(shù)進行配置。一般對VenderID、DeviceID、CommandStatus、RevisicmID、ClassCode、HeaderType、InterruptLine及InterruptPin等寄存器進行配置即可滿足大多場合下的使用要求。

(3)總線命令的簡化設計

PCI規(guī)范中規(guī)定了16種總線命令,設計者只需塒其中有用的命令進行響應即可。總線命令的簡化可減少總線對話的種類,從而可減少硬件沒計的復雜性。一般來說,只要有配置空間讀寫、I/O空間讀寫及存儲器的讀寫,便可滿足一般的使用。

6 結束語

本文介紹了在StratixⅡGX系列FPGA上實現(xiàn)PCI接口的設計技術,具有較強的靈活性,可以方便地移植到其他可編程器件上,有一定的通用性。隨著計算機技術的不斷發(fā)展,計算機總線在PCI總線基礎上逐漸發(fā)展為更高帶寬和頻率的PCI-X總線和擁有2.5G傳輸速率的PCI-Express總線。從當前發(fā)展趨勢來看,PCI-Express總線正得到越來越廣泛的應用,必將成為下一代的總線標準。