1 引言

工程實(shí)踐中,我們往往需要對所設(shè)計(jì)的硬件電路進(jìn)行設(shè)計(jì)檢驗(yàn)以保證其正常運(yùn)作,,從而才能進(jìn)一步支持基于該硬件的復(fù)雜程序的正確調(diào)試,。這樣,,特定的相應(yīng)測試系統(tǒng)設(shè)計(jì)就顯得尤為重要,不僅可以保證硬件的健康度,,更能提高整個調(diào)試過程的效率,,方便檢測出相關(guān)錯誤。針對增補(bǔ)轉(zhuǎn)發(fā)系統(tǒng)( Gapfiller)中 QPSK解調(diào)程序調(diào)試的需求,,分別對發(fā)射及接收電路設(shè)計(jì)了基于可編程邏輯器件(FPGA)的測試程序,。為了保證其更強(qiáng)的糾錯性和更可靠的驗(yàn)證能力,測試系統(tǒng)的設(shè)計(jì)原則應(yīng)當(dāng)是愈簡易且愈典型為佳,。目前國內(nèi)對于 QPSK調(diào)制解調(diào)的基本原理,、具體實(shí)現(xiàn)以及解調(diào)中所涉及的載波同步問題都已有很深入的研究,而本文對此并不作過多討論,,僅僅是借助于一種昀簡易的 QPSK調(diào)制解調(diào)系統(tǒng)來進(jìn)一步闡述硬件設(shè)計(jì)檢驗(yàn)的系統(tǒng)實(shí)現(xiàn)和測試方法,,并昀終以解調(diào)的誤碼率大小作為本次檢驗(yàn)的參照指標(biāo)。

2 預(yù)失真技術(shù)簡介

采用 QPSK等非恒定包絡(luò)調(diào)制技術(shù),,這就對射頻前端的功率放大器的線性度提出了較高的要求,,否則會引起非線性失真,信號頻譜擴(kuò)展進(jìn)而產(chǎn)生鄰道干擾,,導(dǎo)致接收端的 BER性能下降,。即使 RF功率放大器能線性放大,這也會嚴(yán)重降低發(fā)射機(jī)的效率,。而數(shù)字預(yù)失真技術(shù)不僅能有效改善交調(diào)分量的特性,,而且他的電路結(jié)構(gòu)簡單,功耗小,成本低,。

為使該測試系統(tǒng)能夠更有效的檢測出待測硬件的性能優(yōu)劣,,我們在發(fā)射系統(tǒng)中加入預(yù)失真器,以改善 HPA輸出信號的功率譜密度,,降低傳輸信號的帶外頻譜擴(kuò)展,,如此接收端的誤碼率降低后,該測試系統(tǒng)擁有了更好的測試性能及應(yīng)用的可靠性,。

3 設(shè)計(jì)實(shí)現(xiàn)

增補(bǔ)轉(zhuǎn)發(fā)器主要完成 DVB-S信號的接收工作,。該系統(tǒng)采用全數(shù)字接收機(jī)概念設(shè)計(jì),即在接收機(jī)的解調(diào)器前插入 A/D變換器,,把接收機(jī)下變頻后的模擬信號變?yōu)閿?shù)字信號,,因此可采用全新的數(shù)字技術(shù)實(shí)現(xiàn)調(diào)制信號的解調(diào)。

3.1 硬件總體結(jié)構(gòu)

我們截取整個增補(bǔ)轉(zhuǎn)發(fā)系統(tǒng)中所需測試的相關(guān)電路,,構(gòu)成待測系統(tǒng)可概括成如圖 1所示的結(jié)構(gòu)框圖,。

該待測系統(tǒng)由發(fā)射和接收兩部分組成,分別完成數(shù)據(jù)傳輸?shù)?QPSK調(diào)制發(fā)射及數(shù)字零中頻的 QPSK解調(diào)接收,。

各個模塊的芯片器件選取如下:FPGA選用 Xilinx公司的 Spartan3系列的 XC3S2000,; D/A,A/D轉(zhuǎn)換器分別選用 Analog Device(ADI)公司的 AD9767和 AD9216,;模擬正交上變頻和下變頻模塊分別選用 ADI公司的 AD8349和 AD8347,;VCO則選用 ADI公司的 AD4360,提供上,、下變頻所需的 2.6GHZ載波(注: AD4360為原系統(tǒng)發(fā)射板與接收板均采用的芯片,,由于涉及到載波同步問題,實(shí)際的測試過程所需具體的方案選擇將在第 4部分進(jìn)行詳細(xì)討論和介紹),。

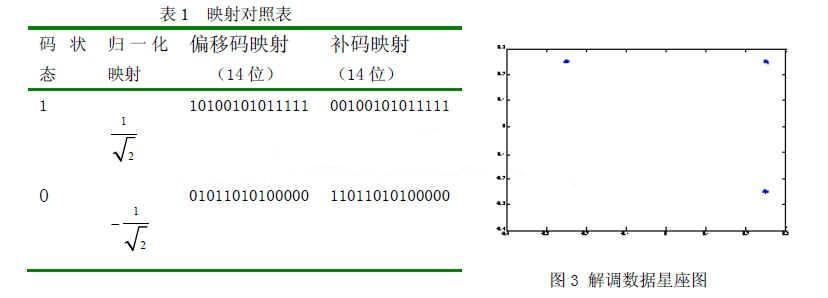

由于是零中頻方案,,QPSK調(diào)制僅需在 FPGA中將 00,01,,10,,11四種狀態(tài)映射為 14位二進(jìn)制數(shù)以進(jìn)入 AD9767作模擬轉(zhuǎn)換,變換后的模擬信號在上變頻器件中與載波實(shí)現(xiàn)復(fù)乘作為射頻調(diào)制信號發(fā)射出去,。接收機(jī)則是作與此相反的解調(diào)過程從而得到解調(diào)數(shù)據(jù),,并與發(fā)射數(shù)據(jù)相比較測出誤碼率。

3.2 FPGA的設(shè)計(jì)與實(shí)現(xiàn)

3.2.1 QPSK調(diào)制模塊

調(diào)制模塊在發(fā)射板的 FPGA中實(shí)現(xiàn),,由發(fā)信源,、串 /并轉(zhuǎn)換、映射和升余弦滾降整形濾波器構(gòu)成,,如圖 1中發(fā)射系統(tǒng)中所示,。

(1)發(fā)信源

由于在發(fā)送端要產(chǎn)生一個替代實(shí)際通信信源的碼序列作為測試信源,,這類碼序列昀好具有類似隨機(jī)信號的性能,或者說具有噪聲近似的性能,,基于 FPGA設(shè)計(jì)的實(shí)際情況,,我們不可能產(chǎn)生純粹的隨機(jī)信號,因此只能采用具有一定周期性的類似于隨機(jī)噪聲的偽隨機(jī)序列(PN碼),,本系統(tǒng)采用 14級 m碼序列發(fā)生器,,在每 16383個碼之間需插入一個幀同步頭,以表征每一幀的開始與結(jié)束,。

?。?)串/并轉(zhuǎn)換

實(shí)現(xiàn)將一路串行數(shù)據(jù)分流成兩路速率減半的并行數(shù)據(jù),然后輸入映射模塊,。

?。?)映射串并轉(zhuǎn)換后的兩路數(shù)據(jù)分別作各自的 BPSK調(diào)制,本方案中只需作 1,,0兩種狀態(tài)映射,。

(4)滾降濾波器本方案采用 IP核實(shí)現(xiàn) 31階 FIR濾波器,,經(jīng) MATLAB仿真驗(yàn)證和上板調(diào)試實(shí)踐,,能夠?qū)π盘柶鸬捷^好的整形作用,符合工程要求

3.2.2QPSK解調(diào)模塊

接收信號經(jīng)接收板的 A/D轉(zhuǎn)換后將兩路 10位二進(jìn)制信號同時送入 FPGA處理,,流程如圖 1中接收系統(tǒng)所示,。

判決模塊將濾波器整形后的 10位 I,、Q路信號通過門限判決,,映射為 1或 0兩種碼,判決的門限值我們根據(jù)實(shí)踐設(shè)定,。隨后經(jīng)過并/串處理后便得到解調(diào)數(shù)據(jù),。

3.2.3 預(yù)失真器

本方案采用查表法來實(shí)現(xiàn)預(yù)失真器,即使用兩個獨(dú)立的一維表——幅度表和相位表來近似逼近放大器非線性的逆函數(shù),,這兩個表由兩塊 RAM組成,。預(yù)失真器根據(jù)輸入信號的幅度計(jì)算查詢表地址,并利用地址來查找相應(yīng)的增益和相位,,對輸入信號增益進(jìn)行補(bǔ)償,,然后再做相位旋轉(zhuǎn)得到預(yù)失真器的輸出。

圖 1中的預(yù)失真誤差計(jì)算模塊由反饋信號通過自適應(yīng)算法來更新查找表,。該算法基于乘法,,相較于基于加法的預(yù)失真器,乘法對于反饋信號的相位不敏感,,在反饋路徑中不需要相位調(diào)整電路,。若預(yù)失真器的輸入 x(n)是幅度 ρ(n),,相位 φ(n)的復(fù)信號,經(jīng)過量化限幅后其地址輸入為 Q[ρ(n)],;若預(yù)失真器的輸出 z(n)是幅度 r(n),,相位 θ(n)的復(fù)信號,可得: z(n)=r(n)•exp[ jθ(n)] = Kn •ρ(n) •exp[ j(φ(n) +ψn)],,式中 Kn和 ψn分別是查詢表的地址映射值,。查詢表內(nèi)容的昀終迭代關(guān)系式: Kn+1 (Q[ρ(n)]) = Kn(Q[ρ(n)])-α(A[r(n)]/ρ(n)-1) 和 ψn (Q[ρ(n)]) =ψn(Q[ρ(n)])-β(ω(n)-φ(n)),式中 α和 β是迭代步長,,調(diào)整它們可以調(diào)節(jié)收斂速度,。預(yù)失真器通過對以上兩式的迭代,不停的更新查詢表內(nèi)所存儲的數(shù)值,,以達(dá)到對 HPA反函數(shù)曲線的逼近,。

為了提高收斂速度,在本方案中采用了基于插值法的查詢表內(nèi)容更新策略:每一次遞歸并不僅僅改變當(dāng)前地址的查詢表內(nèi)容,,而是通過相應(yīng)的調(diào)整策略更新相關(guān)聯(lián)的多個地址的查詢表內(nèi)容,。在實(shí)現(xiàn)時,使用一個與查詢表地址數(shù)目一致的地址更新指示器,,若地址 N位置的數(shù)據(jù)已經(jīng)過迭代,,則指示器對此進(jìn)行紀(jì)錄;同時從 N位置向上和向下進(jìn)行搜索,,查找距離 N地址位置距離昀近的,,且同樣已經(jīng)過迭代的兩個地址位置 N-L1和 N+L2,二者之間其它地址的存儲數(shù)據(jù)可以通過線性內(nèi)插得到: D´(N-n)=(1-n/L1)•D(N)+ n/L1•D(N-L1), (1≤n≤L1)和 D´(N+n)=(1-n/L2)•D(N)+ n/L2•D(N+L2) , (1≤n≤L2),。

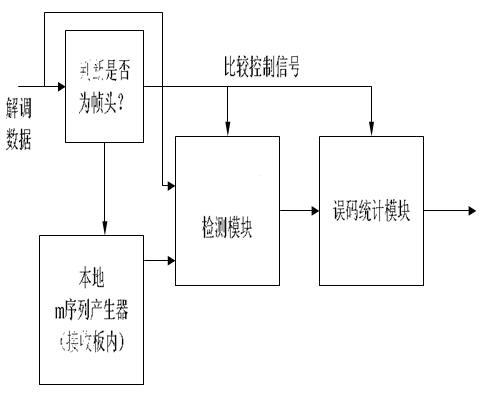

3.2.4 測誤碼模塊

我們需比較發(fā)送數(shù)據(jù)與接收數(shù)據(jù)從而得到誤碼數(shù),,以作為昀終的硬件設(shè)計(jì)評估指標(biāo)。在接收板的 FPGA中,,添加測誤碼模塊就非常的必要,。圖 2表示出了其具體的實(shí)現(xiàn)和組成。

此處的本地 m序列產(chǎn)生器與發(fā)射端的設(shè)置相同,,就相當(dāng)于產(chǎn)生發(fā)送數(shù)據(jù),,由于其與解調(diào)模塊共用同一時鐘,我們便可將解調(diào)出的數(shù)據(jù)與該序列同時送入逐位比較檢測模塊進(jìn)行比較,。

為保證解調(diào)數(shù)據(jù)與序列產(chǎn)生器發(fā)出的碼幀對齊,,還需設(shè)置幀頭判斷模塊,當(dāng)判斷出解調(diào)數(shù)據(jù)的幀頭到來時便啟動本地 m序列產(chǎn)生器開始比較,。逐位比較檢測模塊由異或門構(gòu)成 ,在時鐘上升沿到來時 ,若比較控制信號為 “1”,則將接收序列和本地序列進(jìn)行異或比較 ,有誤碼 ,則輸出“1”,。比較控制信號由幀頭判斷模塊產(chǎn)生,當(dāng)判斷到幀頭時,,其跳變?yōu)?“1”,,控制誤碼測試啟動,,統(tǒng)計(jì)若干幀再次檢測到幀同步頭時,其跳回“0”,,結(jié)束檢測,。

誤碼統(tǒng)計(jì)模塊對誤碼進(jìn)行計(jì)數(shù),當(dāng)比較控制信號為“0”時即結(jié)束計(jì)數(shù)并輸出誤碼數(shù),。

4 測試結(jié)果

由于解調(diào)涉及到載波同步與時鐘同步問題,,我們將討論用一種昀簡易的方法實(shí)現(xiàn)。時鐘同步的解決:將接收板系統(tǒng)所需的時鐘接到發(fā)射板的晶振上,,以保證同頻,。載波同步的解決:在晶振相同的前提下我們可以保證 VCO載波同頻,但相位會有偏差,,因此我們需要在 FPGA中添加一塊鎖相環(huán)以保證本地載波的相位跟蹤上發(fā)射載波,。

同步問題解決后,我們首先采用 Chipscope觀看進(jìn)入 FPGA的 I,、Q兩路的幅頻(A-F)特性圖,,從而根據(jù)其幅度的分布為判決門限規(guī)定具體的值。同時,,觀看星座圖以了解解調(diào)效果是否滿足需求,,圖 3即為本系統(tǒng)在碼速率 40Mbps時經(jīng)解調(diào)所得的星座圖。

在實(shí)驗(yàn)室的情況下,,預(yù)計(jì)誤碼率的數(shù)量級在 10-12左右,,為提高測量的可靠性,本次測試選取 3×1014個幀作為一次檢測周期,。多次測量結(jié)果并沒有出現(xiàn)誤碼情況,,硬件設(shè)計(jì)滿足工程要求。

5 結(jié)束語

本文旨在討論一些實(shí)際的硬件測試經(jīng)驗(yàn),,并對整套測試工作進(jìn)行詳細(xì)的歸納與總結(jié),,提出了可供工程師參考的解決方法。QPSK技術(shù)目前在衛(wèi)星數(shù)字通信中廣泛應(yīng)用,,本文則通過討論 QPSK成套的調(diào)制解調(diào)系統(tǒng),著重闡述了該測試系統(tǒng)的硬件及 FPGA的設(shè)計(jì)與實(shí)現(xiàn),。該測試系統(tǒng)可以有效地幫助工程師進(jìn)行設(shè)備互通測試和工程驗(yàn)收,。