??? 摘 要: 基于FPGA的通信卡設(shè)計原理,。通信卡實現(xiàn)了4路ISDN U接口,、4路RS232串口" title="串口">串口,、2路音頻接口及1路PCI總線之間的通信,,該卡以FPGA(現(xiàn)場可編程門陣列)和MPC860為核心進行設(shè)計,利用FPGA的可編程性靈活實現(xiàn)了各接口之間的數(shù)據(jù)通信" title="數(shù)據(jù)通信">數(shù)據(jù)通信,。本文給出了系統(tǒng)的硬件構(gòu)架,,并對串口傳輸" title="串口傳輸">串口傳輸功能和數(shù)字交換網(wǎng)絡(luò)功能的FPGA實現(xiàn)進行了分析。

??? 關(guān)鍵詞: 通信卡? FPGA? 串口傳輸? 數(shù)字交換網(wǎng)絡(luò)

?

??? FPGA是20世紀(jì)80年代中期以后發(fā)展起來的一種現(xiàn)場可編程的大規(guī)模集成器件,,具有高集成,、高速度、低功耗,、體積小,、可靠性高等一系列優(yōu)點,含有豐富的查找表(LUT)資源,,允許設(shè)計師在不改變硬件電路板的情況下實現(xiàn)不同的功能[1],。因此,F(xiàn)PGA在數(shù)字電路的設(shè)計中得到了廣泛應(yīng)用,。

??? 通信卡采用的FPGA是XILINX的SPARTAN-Ⅱ系列的XC2S50芯片,。該芯片具有176個用戶I/O接口、32Kbit的RAM塊及24 576bit的分散RAM等豐富資源,。在通信卡中,,F(xiàn)PGA芯片實現(xiàn)了串口的透明傳輸和解析傳輸功能、PCI總線的控制功能,、4路ISDN U接口數(shù)據(jù)的復(fù)接和分離功能,、各接口數(shù)據(jù)間的交換功能等。本文分析了基于FPGA的通信卡的設(shè)計原理,,給出了系統(tǒng)的硬件構(gòu)架框圖,,并對串口傳輸功能和數(shù)字交換網(wǎng)絡(luò)功能的實現(xiàn)進行了重點分析。

1 設(shè)計介紹

??? 通信卡的硬件構(gòu)架組成框圖如圖1所示,。CPU控制模塊采用MPC860小系統(tǒng),, MPC860芯片不僅具有普通CPU的運算和處理功能,其外圍還集成了一些控制領(lǐng)域的常用接口,,可支持多種協(xié)議,,如HDLC/SDLC協(xié)議、UART協(xié)議等,;另外,該芯片還具有一個時隙" title="時隙">時隙分配器,,可支持T1,、CEPT、PCM公共模塊和ISDN的基本速率的傳輸[2],。本設(shè)計中傳輸?shù)耐ǖ佬盘柌捎肐SDN的基本速率,,CPU信號由地址信號,、數(shù)據(jù)信號和控制信號三部分組成,實現(xiàn)對通信卡各芯片的配置及對一些公共資源的分配和管理,;PCI總線控制器采用PLX公司生產(chǎn)的PCI通用接口芯片PCI9054實現(xiàn),,本設(shè)計中,該芯片在本地總線側(cè)采用M模式,,可以與MPC860芯片進行無縫連接,;音頻口的編/譯碼器芯片采用TP3067,該芯片實現(xiàn)了模擬音頻信號和PCM數(shù)據(jù)信號的相互轉(zhuǎn)換,;在本卡中,,RS232串口的最大速率為19.2kb/s;U接口控制器采用MOTOROLA公司的MC145572芯片,,該芯片用于綜合業(yè)務(wù)數(shù)字網(wǎng)基本接入接口,,即適用于NT(網(wǎng)絡(luò)終端)也適應(yīng)于LT(線路終端)[3]。MC145572可工作于多種不同模式,,本文采用的是MCU模式的短幀操作模式,接口數(shù)據(jù)為MOTOROLA的IDL型時分2B(B通道數(shù)據(jù)為64Kb/s)+D(D通道數(shù)據(jù)為16Kb/s)數(shù)據(jù)接口,,通信卡的四個ISDN U接口作為NT使用;兩路音頻接口為用戶的語音通信提供接口,。

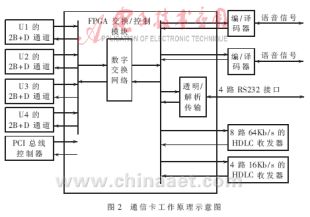

??? 實現(xiàn)圖1所用的FPGA是XILINX的SPARTAN-Ⅱ系列的XC2S50芯片,,該芯片負(fù)責(zé)通信卡各接口數(shù)據(jù)的控制和相互通信,包括:CPU對PCI總線控制器,、串口控制器,、U接口控制器等芯片的控制;PCI總線接口與CPU間的數(shù)據(jù)通信,;音頻口與U接口間的數(shù)據(jù)通信,;RS232串口的透明傳輸方式" title="傳輸方式">傳輸方式(串口與串口、串口與U口間的數(shù)據(jù)傳輸)和解析傳輸方式(串口與CPU間的數(shù)據(jù)傳輸)的控制,;U接口與CPU的數(shù)據(jù)通信,;U接口與串口間的數(shù)據(jù)通信。通信卡各接口間數(shù)據(jù)的交換和通信都由FPGA交換控制模塊的數(shù)字交換網(wǎng)絡(luò)完成,,其工作原理圖如圖2所示,。圖2中所示的8路64kb/s的HDLC收發(fā)器和4路16kb/s的HDLC收發(fā)器由MPC860芯片提供。本文將對由FPGA實現(xiàn)的串口傳輸功能和數(shù)字交換網(wǎng)絡(luò)功能的實現(xiàn)進行詳細(xì)分析,。

?

2 功能實現(xiàn)

??? 本設(shè)計中,,F(xiàn)PGA是通信卡功能實現(xiàn)的關(guān)鍵芯片,是各接口數(shù)據(jù)通信的橋梁,。下面就FPGA實現(xiàn)的串口傳輸功能(包括串口工作方式,,即透明傳輸方式和解析傳輸方式的切換及透明傳輸方式時不同速率數(shù)據(jù)間的轉(zhuǎn)換)及用于各接口數(shù)據(jù)通信的數(shù)字交換網(wǎng)絡(luò)功能的實現(xiàn)進行詳細(xì)分析。

2.1 串口傳輸功能的實現(xiàn)

??? 通信卡的串口功能芯片由串口擴展芯片ST16C654和收發(fā)器芯片LTC1387組成,ST16C654可擴展4個串口,,串口傳輸功能示意圖見圖3,。在通信卡中,串口的數(shù)據(jù)傳輸方式有透明傳輸方式和解析傳輸方式兩種,,利用FPGA的可編程性靈活實現(xiàn)了串口傳輸方式的切換,。在解析方式下,只需將ST16C654的收發(fā)數(shù)據(jù)線與LTC1387的收發(fā)數(shù)據(jù)線相連,,如要使串口1工作在解析模式下,,通過FPGA將L_TD1與ST_TD1連接及L_RD1與ST_RD1連接便可;在透傳方式下,,由于串口的傳輸速率不定(在本卡中,,串口的傳輸速率≤19.2Kb/s),而ISDN U接口一個時隙的傳輸速率為64kb/s,,因此,,在串口與U口進行數(shù)據(jù)透傳時,需要編寫一個具有速率轉(zhuǎn)換功能的編/解碼器,。根據(jù)抽樣原理,,對串口輸入的數(shù)據(jù)(速率≤19.2kb/s),用64kb/s(64>19.2×2)速率進行抽樣,,根據(jù)抽樣值能準(zhǔn)確地確定原信號[4],。本文以如圖3所示的串口1與串口5間的數(shù)據(jù)透傳為例進行說明,其工作過程描述如下:首先,,通過CPU控制FPGA,,使串口1和串口5工作在透傳模式下,將串口1的L_RD1數(shù)據(jù)線連接到FPGA的編/解碼器,,編/解碼器以64Kb/s的速率對串口數(shù)據(jù)進行采樣,,并將采樣數(shù)據(jù)放到U接口中的一個B通道的一個時隙上進行傳輸。通過ISDN通道傳輸?shù)搅硪粋€的U接口,,該U接口將透傳的數(shù)據(jù)送往本地FPGA,,并經(jīng)過FPGA編/解碼器后將數(shù)據(jù)送往串口5,這樣便完成了數(shù)據(jù)從串口1到串口5的透傳,。同理,,可實現(xiàn)數(shù)據(jù)從串口5到串口1的透傳。本設(shè)計串口數(shù)據(jù)的FPGA編/解碼功能的實現(xiàn)采用VHDL語言編寫,。編碼時,,根據(jù)抽樣原理采用64kb/s速率進行采樣便可;解碼時,,只需將FPGA收到的數(shù)據(jù)以64Kb/s速率發(fā)往LTC1387的收數(shù)據(jù)端口即可,。其功能實現(xiàn)代碼如下所示,。其中CLK2M為2MHz時鐘信號,C64K為與2MHz時鐘信號的下降沿對齊的64kb/s采樣信號,,C64K_1n的上升沿與C64K信號的下降沿對齊且其高電平寬度為(1/2M)s,DATA_SR為串口輸入的數(shù)據(jù),,DATA_SR_N為串口輸入數(shù)據(jù)的取反,,Q為編碼后的數(shù)據(jù),asyn_out為解碼后送給串口的數(shù)據(jù),。

??????????????????????????????

??? 下面是FPGA編/解碼器編碼部分的代碼:

process(CLK2M,,C64K)

begin

if C64K=′1′ then QQ1 <=(others=>′0′);else if CLK2M′

event and CLK=′1′ then if DATA_SR=′1′ then

QQ1 <=QQ1+1,;end if,;end if;

end process,;

Q1 <=QQ1,;

process(CLK2M,C64K)

begin

if C64K=′1′ then QQ <=(others =>′0′),;else if CLK2M′

event and CLK2M=′1′ then if DATA_SR_N=′1′ then

QQ2 <=QQ2+1,;end if;end if,;

end process,;

Q2 <=QQ2;

Q1_compare_Q2<=′1′ when Q1(7 downto 0)>Q2(7 downto 0)

else ′0′,;

process(CLK2M)

begin

if CLK2M′ event and CLK2M=′1′ then if C64K_1n=′1′ then

Q<=Q1_compare_Q2,;end if;end if,;

end process,;

??? 以下為FPGA編/解碼器解碼部分的代碼:

process(CLK2M,F(xiàn)8K)

begin

if? CLK2M′event and CLK2M=′1′ then? if F8K=′0′ then?

p<=(others =>′0′),;else p<=p+1,;end if;end if,;

count<=p,;

end process;

process(count(7 downto 5))?--msb comes out first,;

begin

?case count(7 downto 5) is

??? when ″000″=>Dout <=locked_ts(7),;--locked_ts存儲的數(shù)據(jù)為解碼前的串口數(shù)據(jù)

??? when ″001″=>Dout<=locked_ts(6);

??? when ″010″=>Dout<=locked_ts(5),;

??? when ″011″=>Dout<=locked_ts(4),;

??? when ″100″=>Dout<=locked_ts(3),;

??? when ″101″=>Dout<=locked_ts(2);

??? when ″110″=>Dout<=locked_ts(1),;

??? when ″111″=>Dout<=locked_ts(0),;

??? when others=>Dout<=′Z′;

? end case,;

end process,;

asyn_out<=′0′ or Dout;

2.2 數(shù)字交換網(wǎng)絡(luò)功能的實現(xiàn)

??? 數(shù)字交換網(wǎng)絡(luò)是通信卡實現(xiàn)數(shù)據(jù)交換的核心部分,,其基本功能是在兩個不同時隙間進行交換(每個時隙對應(yīng)一個用戶),。數(shù)字交換網(wǎng)絡(luò)由數(shù)據(jù)存儲器和控制存儲器兩部分組成。數(shù)據(jù)存儲器的工作方式是“順序?qū)懭?,控制讀出”,,即由定時脈沖控制,按順序?qū)⒉煌瑫r隙的數(shù)據(jù)寫入相應(yīng)的單元中,,寫入的單元號和時隙號一一對應(yīng),,讀出時則要根據(jù)控制存儲器的控制信息(讀出數(shù)據(jù))進行;控制存儲器是“控制寫入,,順序讀出”,,即數(shù)據(jù)寫入由CPU控制進行,而數(shù)據(jù)讀出由定時脈沖控制,,按照時隙號讀出相對應(yīng)單元內(nèi)容[5],。

??? 本設(shè)計的交換網(wǎng)容量為128(條)×128(條),假設(shè)基地址為BASE_ADDR,,按單字節(jié)尋址,,每個地址代表接收時隙號(目的時隙號),該地址對應(yīng)的內(nèi)容字節(jié)最高位指示是否做交換,,“0”代表不交換,,“1”代表做交換,低7位數(shù)據(jù)表示發(fā)送時隙號(源時隙號),。例如:要將N時隙發(fā)送到M時隙,,使用如下等式:BASE_ADDR[M]=N|0X80,其中BASE_ADDR[M]為(BASE_ADDR+M)的地址,;BASE_ADDR[M]=N|0X80表示將N與0X80相或后的值賦予(BASE_ADDR+M)的地址空間,。

??? 通信卡FPGA數(shù)字交換網(wǎng)絡(luò)的VHDL語言實現(xiàn)代碼如下所示。其中CLK2M為2MHz時鐘信號,,F(xiàn)8K_1D為與CLK2M上升沿對齊的同步信號,。

process(CLK2M)????--產(chǎn)生讀CM的地址

begin

if CLK2M′event and CLK2M=′0′ then if F8K_1D=′0′ then

sm_ram_addr(6 downto 0)<=″0000001″;

else sm_ram_addr(6 downto 0)<=sm_ram_addr(6 downto 0)+1,;

end if,;end if,;end if;

end process,;

cm_ram_addr(6 downto 0)<=sm_ram_addr(6 downto 0)–′1′,;

DRAM_SM:dual_ram_8_128??--數(shù)據(jù)存儲器

PORT MAP(?addra?=>sm_ram_addr(6 downto 0),

??? addrb?=>cm_to_sm_addr(6 downto 0),,

??? clka??=>CLK2M,,

??? clkb??=>not CLK2M,

??? dina??=>sm_in_data(7 downto 0),, --數(shù)據(jù)存儲器輸入數(shù)據(jù)

??? doutb?=>sm_out_data(7 downto 0),--數(shù)據(jù)存儲器讀出數(shù)據(jù)

??? ena??=>′1′,,

??? enb??=>cm_to_sm_addr(7),,--是否允許數(shù)據(jù)輸出

??? wea??=>′1′);

DRAM_CM:dual_ram_8_128???--控制存儲器

PORT MAP(?addra?=>cpu_a(6 downto 0),,?--cpu地址

??? addrb?=>cm_ram_addr(6 downto 0),,

??? clka??=>cpu_clk,??--cpu時鐘信號

??? clkb??=>CLK2M,,

??? dina??=>cpu_din(7 downto 0),,--cpu輸入數(shù)據(jù)

??? doutb?=>cm_to_sm_addr(7 downto 0),

??? ena??=>not cs,,--cs為FPGA的片選信號

??? enb??=>′1′,,

????wea??=>not cpu_rw);--cpu_rw為cpu的讀寫信號

??? 基于FPGA設(shè)計的通信卡具有靈活性強,、可控性好,、硬件構(gòu)架簡單等優(yōu)點。通信卡在實際應(yīng)用中,,很好地實現(xiàn)了各接口間的數(shù)據(jù)通信且其性能非常穩(wěn)定,。另外,通信卡能根據(jù)需要對一些功能進行刪除和添加,,方便了系統(tǒng)功能的調(diào)試,,滿足了用戶的不同需求。

參考文獻

[1] 王俊雄,,黃鉉,,劉正義.基于FPGA的嵌入式系統(tǒng)設(shè)計.電子工程師,2006,,(10).

[2] 陳曉竹,,道克剛.PowerPC860嵌入式系統(tǒng)及應(yīng)用.北京:機械工業(yè)出版社,2006.

[3] 錢志軍,鄧志宏.MC145572 ISDN U接口收發(fā)器與MC145574 ISDN S/T接口收發(fā)器用戶手冊.北京:人民郵電出版社,,1998.

[4] 樊昌信,,張甫翊.通信原理(第5版).國防工業(yè)出版社,,2002.

[5] 葉敏.程控數(shù)字交換與現(xiàn)代通信網(wǎng).北京:北京郵電大學(xué)出版社,1997.