1 引言

自動測試系統(tǒng)ATS(Automatic Test System)集成測試所需的全部激勵與測量設備,計算機高效完成各種模式的激勵及響應信號的采集、存儲與分析,對被測單元進行自動狀態(tài)監(jiān)測、性能測試和故障診斷。總線是ATS的重要組成部分,是計算機與測試硬件內(nèi)部及外設傳遞信息的公共通路,其性能參數(shù)直接影響ATS整體的功能實現(xiàn)和性能指標。

通用串行總線USB(Universal Serial Bus)主要用于PC與外圍USB設備互聯(lián)。其物理連接是一種分層的菊花鏈結構,最多支持5 Hub層及127個外設。該結構獨立性強。抗干擾性強、傳輸速率高、占用資源有限、使用靈活、支持熱插拔,因此USB技術逐漸成為現(xiàn)代ATS數(shù)據(jù)傳輸?shù)陌l(fā)展趨勢。

這里通過Cypress公司的USB單片機CY7C68013A的PE和GPIF接口實現(xiàn)計算機與測試控制器件FPGA和緩沖FIFO的高速數(shù)據(jù)通信,完成ATS測試指令信號和數(shù)據(jù)的下載,自檢和反饋數(shù)據(jù)的上傳功能,實現(xiàn)測試技術的智能化。重點從USB硬件和固件代碼設計闡述在測試系統(tǒng)數(shù)據(jù)傳輸過程中USB技術的應用。

2 USB接口通信工作流程

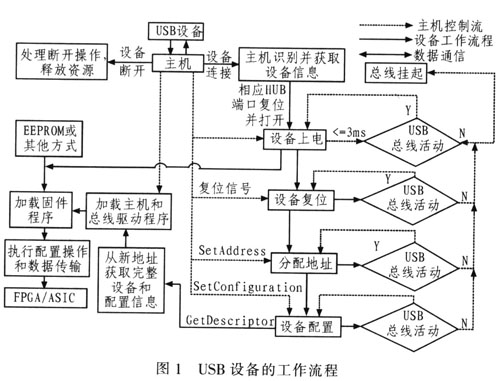

USB具有靈活的1二作流程,如圖1所示。

|

圖1中,USB設備的工作流程從設備連接→上電→復位→分配地址→配置操作→執(zhí)行固件代碼,6大工作狀態(tài),這些狀態(tài)在USB主機的控制下實現(xiàn)狀態(tài)間的轉換和總線的訪問。USB設備隨時根據(jù)總線活動情況判斷是否進入或退出掛起狀態(tài),節(jié)省USB系統(tǒng)的功耗。

從圖1分析可知,USB通信包括USB系統(tǒng)應用軟件、設備及總線驅動程序和USB固件3層。應用軟件設計由2部分組成:動態(tài)鏈接庫和應用程序。動態(tài)鏈接庫負責與內(nèi)核態(tài)的USB功能驅動程序通信并接收應用程序對USB設備I/O的各種操作請求,應用程序調(diào)用Win32 APl函數(shù)DeviceToCon-trol向設備發(fā)出命令;USB設備驅動程序通過總線驅動程序發(fā)出輸入輸出請求(IRP),實現(xiàn)對USB設備信息的發(fā)送和接收;總線驅動程序負責總線檢測、電源管理和USB事務處理,固件程序實現(xiàn)FX2器件的初始化設置,設備請求處理,電源管理和外圍通信功能,是整個通信架構的核心。在測試系統(tǒng)中,通過固件代碼建立數(shù)據(jù)物理通道并實現(xiàn)通信協(xié)議,用戶可通過測試軟件對USB設備進行功能控制,實現(xiàn)數(shù)據(jù)的有效通信和測試任務高效、可靠地完成。

3 測試系統(tǒng)USB硬件電路原理

CY7C68013A(簡稱68013A)集成USB2.0收發(fā)器、串行接口引擎(SIE)、增強8051內(nèi)核和可編程外圍接口,提供一個高效的USB2.0解決方案,它可配置為3種數(shù)據(jù)通信模式:端口、GPIF和Slave FIFO模式。本設計利用GPIF方式快速、靈活等特點,有效地解決了端口方式下USB2.0設備數(shù)據(jù)傳輸速度瓶頸,大大提高了數(shù)據(jù)的傳輸速率。FX2專門為GPIF提供外圍接口信號,如8/16位數(shù)據(jù)線、CTL、Ready信號及地址線。從通用性、低功耗等方面考慮,將68013A的PA,PB,PD和 PE 4個I/O端口,6個CTL[5:0]和6個RDY[5:0]與FIFO或FPGA相連實現(xiàn)數(shù)據(jù)通信和握手、控制等功能。

圖2為GPIF方式硬件連接框圖,其中IFCLK是雙向時鐘信號,當配置為輸出時,IFCLK被FX2驅動為30 MHz/48MHz:當配置為輸入時,時鐘范圍為5~48 MHz;GPIFADR(9)信號為外部設備提供地址線,在總線上地址值是自增的;FD[15:0]是USB主機通過FX2和外部設備進行數(shù)據(jù)傳輸?shù)臄?shù)據(jù)線,可配置成8位或16位;CTL[5:0]為外設控制信號,如讀寫選通、使能等;RDY[5:0]為外設狀態(tài)檢測信號,如外部FIFO的空、滿等。

整個系統(tǒng)的工作原理:主機通過應用軟件設置將相應的測試指令和數(shù)據(jù)經(jīng)USB總線下載到68013A內(nèi)部FIFO中,按照同件代碼配置相關寄存器、端口和中斷,實現(xiàn)與FIFO和FPGA的數(shù)據(jù)通信。外部使用兩片F(xiàn)IFO匹配數(shù)據(jù)傳輸速率,由外部控制信號RD(或RD2)/WR(或WR2)來控制數(shù)據(jù)的讀/寫。為防止數(shù)據(jù)的空讀或寫溢出,用標志端EF和HF標明FIFO狀態(tài)。這種內(nèi)外FIFO雙緩沖設計為大容量、高速數(shù)據(jù)傳輸提供更大的緩沖空間和時序匹配。 FPGA從FIFO1接收數(shù)據(jù)的同時,按照從PE口收到的Status[7:0]指令,判斷所接收數(shù)據(jù)的類型和職能,將數(shù)據(jù)傳輸?shù)较鄳臏y試調(diào)理和輸出電路,執(zhí)行相應操作,判斷被測試對象的工作情況;如從PE端口收到的是自檢命令,則將測試數(shù)據(jù)回采,判斷系統(tǒng)自身工作情況。被測試對象反饋的信號和測試采集的數(shù)據(jù),自檢數(shù)據(jù)經(jīng)FPGA數(shù)據(jù)融合處理,從FIFO2傳到68013A的GPIF接收端口,所有CY7C68013A的內(nèi)部數(shù)據(jù)和端口操作全部由固件程序描述。

|

4 固件程序設計

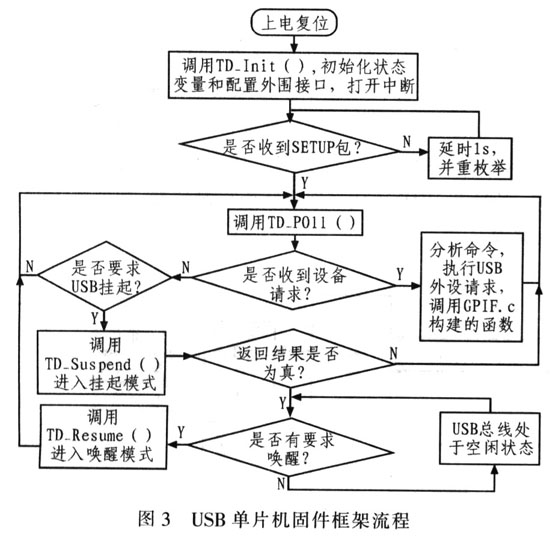

68013A固件負責處理主機各種USB設備請求,控制68013A與外圍電路FPGA進行數(shù)據(jù)傳輸,協(xié)調(diào)主機和FPGA 之間的通信。設計利用Cypress公司生產(chǎn)的EZ-USB固件程序框架,其中包括初始化、處理USB設備請求、中斷和USB電源管理等任務,固件的編譯在KeilμVision2的集成開發(fā)環(huán)境中進行。68013A固件設計流程如圖3所示。該設計主要包括5個部分:fw.c(框架源文件)、 periph.c(用戶任務調(diào)度函數(shù)文件)、dscr.a(chǎn)51(描述符表)、USBJmpTb.OBJ(中斷跳轉表)、Ezusb.lib(EZ_USB 庫文件)。用戶僅需對dscr.a(chǎn)51和pe-riph.c修改文件中部分代碼即可完成USB設備的各種功能。periph.c文件通過調(diào)用任務分配、標準設備請求和中斷處理等函數(shù)來處理USB事件。其中主要修改TD_Init()和TD_Poll()兩個任務分配函數(shù)。

TD_Init()函數(shù)用于負責初始化端點狀態(tài)變量,配置外圍I/O接口及設置端口初始值。TD_Poll()主要是初始化功能寄存器,并對設備進行重新列舉,完成主機對設備的配置任務;執(zhí)行過程中響應中斷,對中斷作相應處理并控制外圍電路。

5 GPIF waveforms設計及測試分析

利用GPIF Designer編輯GPlF waveform波形文件,然后轉換生成GPIF.c文件,作為固件的一部分,加入keil c工程進行編譯。每個GPIF波形描述符都由7段組成:state0~state6(簡稱S0~S6)。執(zhí)行完S0-S6的動作后,都進入idle狀態(tài) (S7),以準備啟動下一次GPIF動作。每個state可定義為非決定態(tài)(NDP)或決定態(tài)(DP)。當state為NDP時只是簡單地延時;為DP 時,它將根據(jù)RDY[0:5]上的輸入信號狀態(tài)及內(nèi)部FIFO的可編程標志和內(nèi)部自定義的Ready標志,將這些信號進行邏輯處理,并根據(jù)邏輯結果在選擇即將執(zhí)行的state。每個state執(zhí)行時可指定CTL[0:5]輸出狀態(tài)。從而控制外圍時序電路。圖4和圖5分別是GPIF波形編輯文件和測試結果。圖5中下載了開關量,模擬量和數(shù)字量信號,各1路,4C6600為START發(fā)送握手標志。

|

6 結束語

充分利用CY7C68013A的GPIF通信方式,實現(xiàn)計算機和測試系統(tǒng)硬件之間控制信號和測試數(shù)據(jù)高速、可靠的傳輸;通過適當修改硬件測試接口,即可利用新開發(fā)固件和應用軟件實現(xiàn)通用化測試目的,具有較高的實用價值。基于該設計方案的某型號自動測試系統(tǒng)已成功應用于航天測試領域。