0 引 言

目前,在很多視頻數(shù)據(jù)采集以及實時顯示的應(yīng)用開發(fā)中,常需要用到存儲容量大、讀寫速度快的存儲器。在各種存儲器件中,同步動態(tài)隨機存儲器SDRAM 以其速度快、容量大、價格低的特點而備受關(guān)注。SDRAM 的工作頻率可以達到100MHz 甚至更高,但是在其工作周期內(nèi),因為要有刷新、預(yù)充電以及尋址等必要的操作,不可能總處于數(shù)據(jù)傳輸狀態(tài),使得它的帶寬不能達到百分之百的利用,實時顯示效果因此受到影響。為此,本文在研究有關(guān)文獻的基礎(chǔ)上,根據(jù)具體情況提出了一種獨特的方法,利用FPGA 的片上資源開辟了多個FIFO 作為讀寫緩存,實現(xiàn)了多端口SDRAM 控制器的設(shè)計,并用Verilog 硬件描述語言[1] 給予實現(xiàn),仿真結(jié)果表明該控制器能夠輪流地從多個緩存向SDRAM 進行存取,實現(xiàn)了高速多數(shù)據(jù)緩存,充分利用了SDRAM 的有效帶寬,提高了存取速度,從而達到實時顯示的要求,并且只要將該設(shè)計稍加修改,便可應(yīng)用到其他需要多數(shù)據(jù)緩存的場合。

1 SDRAM 基本操作原理[2] [3]

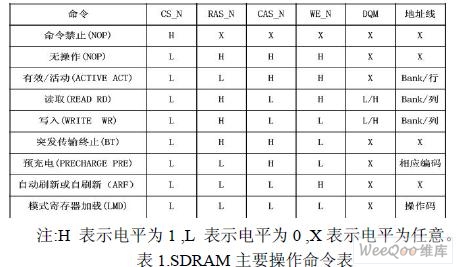

SDRAM 的主要控制信號有:CS_N:片選使能;CAS_N:列地址選通信號;RAS_N:行地址選通信號;WE_N:寫使能信號;DQM:字節(jié)掩碼信號;ADDR:地址線。以上這些信號的邏輯組合就組成了SDRAM 的主要操作命令,如表1 所示:

|

1.1 初始化操作

SDRAM 上電一段時間后, 經(jīng)過初始化操作才可以進入正常工作過程。初始化主要完成預(yù)充電、自動刷新和模式寄存器的配置。

1.2 SDRAM 的基本讀寫操作

讀寫操作主要完成與SDRAM 的數(shù)據(jù)交換。可以分為非突發(fā)連續(xù)操作模式和突發(fā)連續(xù)操作模式, 非突發(fā)指的是傳送數(shù)據(jù)和地址必須是相對應(yīng)一個一個的傳輸, 突發(fā)模式則是地址控制信號只需要給出首地址信息, 而數(shù)據(jù)實現(xiàn)連續(xù)傳輸過程, 突發(fā)數(shù)據(jù)的長度可以為1, 2,4, 8 和全頁。

1.3 刷新操作

動態(tài)存儲器都存在刷新問題。SDRAM 的刷新方式有自動刷新和自主刷新, 這里主要采用自動刷新方式, 每隔一段時間向SDRAM 發(fā)一條刷新命令。

2 基于FPGA 的多端口SDRAM 控制器設(shè)計

設(shè)計中選用的FPGA 是Altera 公司生產(chǎn)的CycloneII 系列中的EP2C35,選用的SDRAM 是ISSI 推出的64-MBIT 的IS42S16400B ,它是以1MWords X 16Bits X 4Banks 為組織結(jié)構(gòu)的同步動態(tài)隨機存儲器,最高時鐘頻率可達143MHz[4]。

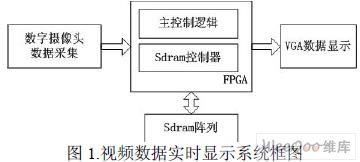

視頻數(shù)據(jù)實時顯示系統(tǒng)的基本構(gòu)成如圖1 所示[5]:

SDRAM 作為幀緩沖器,它的上一級數(shù)據(jù)輸入是25MHz 的視頻數(shù)據(jù)采集模塊,所得到的數(shù)據(jù)經(jīng)處理以后是每個像素點30 位數(shù)據(jù),下一級是VGA 顯示器以25MHz 的時鐘進行數(shù)據(jù)輸出,也要求是每個像素點30 位,而SDRAM 的數(shù)據(jù)寬度是16 位,因而每當(dāng)存入和讀取一個像素點的數(shù)據(jù)時,各需要進行兩次傳輸。本款芯片SDRAM 的工作頻率雖然可設(shè)置為100MHz ,但是如果不加緩存的話,就不能使用頁突發(fā)模式來有效利用帶寬,而且SDRAM 內(nèi)部其他操作也需要占用一定的時間,不能達到實時顯示的效果。本文在研究有關(guān)文獻的基礎(chǔ)上,利用FPGA 的片上資源開辟4 個FIFO 緩存,將SDRAM 的數(shù)據(jù)端口仿真成四個虛擬端口(兩個寫端口+兩個讀端口),每個端口的數(shù)據(jù)寬度都是16位,深度是兩頁SDRAM 的大小。且按照一致的規(guī)則將30 位采集和顯示的數(shù)據(jù)分成兩組與緩存進行存取,相應(yīng)的,在SDRAM 上使用兩個Bank 來分別存取每組數(shù)據(jù)。控制器根據(jù)緩存FIFO 的狀態(tài)對SDRAM 發(fā)出讀寫請求,采用頁模式突發(fā)傳輸和Bank 切換的方式來匹配時序要求。

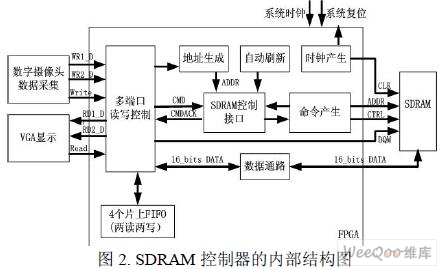

SDRAM 控制器的內(nèi)部結(jié)構(gòu)如圖2 所示:

各功能模塊描述如下:

2.1 多端口讀寫控制模塊

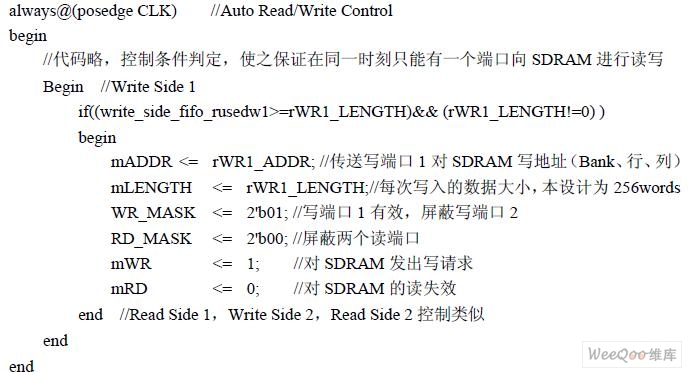

該模塊是與外設(shè)交換數(shù)據(jù)的接口,并且根據(jù)緩存FIFO 的狀態(tài),自動生成對SDRAM 的讀寫請求以及數(shù)據(jù)緩沖處理。它是本設(shè)計的核心。下面著重描述一下讀寫請求產(chǎn)生的設(shè)計過程和簡要代碼。

將數(shù)據(jù)采集模塊得到的兩組數(shù)據(jù)同時存貯到各自的寫緩存FIFO 里,只要寫緩存里的數(shù)據(jù)達到了SDRAM 每頁的數(shù)據(jù)大小,就產(chǎn)生對SDRAM 的寫請求,因為每個緩存的大小是兩頁SDRAM ,所以此時數(shù)據(jù)采集模塊還可以繼續(xù)存數(shù)據(jù)。類似的,VGA 所顯示的數(shù)據(jù)也是從兩個讀緩存 FIFO 得到的,只要讀緩存里的數(shù)據(jù)小于SDRAM 每頁的數(shù)據(jù),就產(chǎn)生對SDRAM 的讀請求,這樣每個緩存里的兩頁輪流操作。關(guān)鍵代碼如下:

2.2 地址生成模塊

該模塊用來自動生成對SDRAM進行存取操作的Bank地址,起始地址和突發(fā)長度。由于30位的像素數(shù)據(jù)等分各存入兩個Bank里,所以在Bank里它們的對應(yīng)地址是相同變化的,這樣存取數(shù)據(jù)時,對兩個Bank的讀寫地址的控制就是統(tǒng)一增減的,降低了使用一個Bank時讀寫控制的繁雜性。

2.3 自動刷新模塊

SDRAM需要不斷的刷新操作,同一行的存儲單元每隔64m s 需要刷新一次,對于本芯片的一個Bank 中的4096 行存儲單元,則每15. 625us 就需要發(fā)出一個刷新命令,由于本設(shè)計采取緩存的辦法,所以應(yīng)該按讀寫SDRAM到緩存FIFO的時間為準(zhǔn)來設(shè)計刷新計數(shù)器的初始值。以頁模式進行讀寫,讀數(shù)據(jù)的整個時間過程是tRCD+ tCL+mLENGTH ,寫數(shù)據(jù)的整個時間過程是tRCD+mLENGTH ,其中tRCD是激活命令到讀或?qū)懨钇陂g的延遲,tCL是讀命令發(fā)出后到第一個有效數(shù)據(jù)之間的間隔,mLENGTH 是SDRAM 的頁長,本設(shè)計中tRCD =3, tCL=3,mLength=256 。因此刷新計數(shù)器的初始值設(shè)置為2X(256+3+3)+ 2X(256+3)=1042 ,經(jīng)計算遠遠小于所要求的刷新周期,初值設(shè)置合理。開始工作后,每當(dāng)刷新計數(shù)器值減為0, 便會發(fā)出刷新命令,保證SDRAM內(nèi)的數(shù)據(jù)不丟失,自動刷新之后直接進行預(yù)充電來關(guān)閉工作行。

2.4 命令產(chǎn)生模塊

該模塊主要負責(zé)命令仲裁、命令生成以及時序控制等。SDRAM 優(yōu)先級仲裁算法通常有兩種:一種是固定優(yōu)先級算法,另一種是循環(huán)優(yōu)先級算法。本文設(shè)計的SDRAM 控制器是應(yīng)

用在實時圖像處理系統(tǒng)中的,對數(shù)據(jù)處理效率要求很高,因此設(shè)計中選用固定優(yōu)先級算法。本文規(guī)定優(yōu)先級如下:初始化請求>刷新請求>讀請求>寫請求>其他。

2.5 時鐘產(chǎn)生模塊

通過使用PLL(鎖相環(huán)) 資源為FPGA 內(nèi)部的時序元件提供穩(wěn)定的時鐘以及為SDRAM 提供可靠的時鐘,本設(shè)計中為100MHz 。

1 SDRAM 控制接口模塊:該模塊主要完成對SDRAM 的命令解碼、初始化配置等。

2 數(shù)據(jù)通路模塊:根據(jù)模式寄存器的模式字及對用戶指令的分析結(jié)果,使SDRAM 的地址及數(shù)據(jù)和相應(yīng)的操作指令在時序上同步。

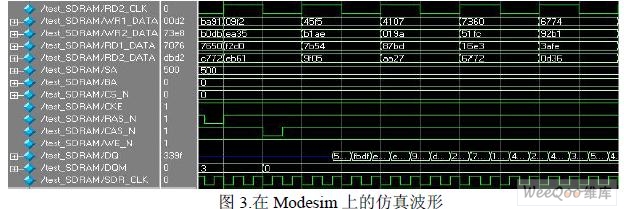

3 仿真驗證

使用Modesim 軟件[6]對多端口SDRAM 控制器進行仿真驗證,得到的SDRAM 讀寫信號仿真波形圖時序合理、邏輯正確,可以從多個緩存FIFO 輪流地向SDRAM 以頁突發(fā)模式進行讀寫操作,有效利用了SDRAM 的帶寬,而數(shù)據(jù)采集和數(shù)據(jù)顯示模塊可以在不受SDRAM 操作時序影響的情況下,連續(xù)地向緩存FIFO 中存取數(shù)據(jù)。仿真波形如圖3 所示:

將該控制器集成到視頻數(shù)據(jù)采集顯示系統(tǒng)的設(shè)計中,經(jīng)QuartusII 分析綜合,生成的網(wǎng)表文件下載到FPGA 芯片上,并將數(shù)字攝像頭和VGA 顯示器連接好,進行實際硬件驗證,幾經(jīng)調(diào)試,該系統(tǒng)已能夠成功運行并且達到了良好的實時顯示效果。

4 結(jié) 論

本文使用狀態(tài)機的設(shè)計思想,采用Verilog 硬件描述語言設(shè)計實現(xiàn)了一種基于FPGA 的,可用于多數(shù)據(jù)緩存的、高效利用SDRAM 帶寬的多端口SDRAM 控制器。

本文作者創(chuàng)新點:設(shè)計實現(xiàn)的SDRAM 控制器能夠完成多端口數(shù)據(jù)緩存,充分利用了SDRAM 的有效帶寬,提高了存取速度,只要稍加修改就可以應(yīng)用到圖像處理,視頻監(jiān)控等需要高速多數(shù)據(jù)緩存的場合,可重用性好。