1.引言

隨著當前移動存儲技術(shù)的快速發(fā)展和移動存儲市場的高速擴大,FLASH型存儲器的用量迅速增長。FLASH芯片由于其便攜、可靠、成本低等優(yōu)點,在移動產(chǎn)品中非常適用。市場的需求催生了一大批FLASH芯片研發(fā)、生產(chǎn)、應用企業(yè)。為保證芯片長期可靠的工作,這些企業(yè)需要在產(chǎn)品出廠前對FLASH存儲器進行高速和細致地測試,因此,高效FLASH存儲器測試算法的研究就顯得十分必要。

不論哪種類型存儲器的測試,都不是一個十分簡單的問題,不能只將存儲器內(nèi)部每個存儲單元依次測試一遍就得出結(jié)論,這是因為每一個存儲單元的改變都有可能影響存儲器內(nèi)部其他單元的變化(這種情況又是常常發(fā)生的)。這種相關(guān)性產(chǎn)生了巨大的測試工作量[1]。另外,F(xiàn)LASH存儲器有其自身的特點,它只能將存儲單元內(nèi)的數(shù)據(jù)從“1”寫為“0”,而不能從“0”寫為“1”,若想實現(xiàn)“0”->“1”操作,只能把整個扇區(qū)或整個存儲器的數(shù)據(jù)擦除,而擦除操作要花費大量的時間。FLASH存儲器還有其他特性,比如讀寫速度慢、寫數(shù)據(jù)之前要先寫入狀態(tài)字、很多FLASH只適于順序讀寫而不適于跳轉(zhuǎn)操作等,這些特點都制約了FLASH存儲器的測試。

為解決FLASH測試中的這些問題,人們提出了應用內(nèi)建自測試[2]或利用嵌入式軟件[3]等測試方法測試相關(guān)性能,都取得了比較好的效果,但這些方法大多不適用于利用測試儀進行批量的產(chǎn)品測試。而多數(shù)對通用存儲器測試很有效的算法,由于受到FLASH器件自身的限制(如不能不能直接從“0”寫為“1”),很難直接適用于FLASH測試。

文本在簡單介紹FLASH芯片的結(jié)構(gòu)與特點之后,說明了FLASH存儲器測試程序原理。在此基礎上,分析和改進了幾種通用的存儲器測試方法,使之能有效地應用于FLASH測試中。這些方法簡單高效,故障覆蓋率高,并且可以快速預先產(chǎn)生,與其他一些測試算法[4][5]相比,更適于應用在測試儀中進行工程測試。本文分析了這些方法的主要特點,在此基礎之上,介紹了實際FLASH存儲器測試中應用的流程。

2.FLASH芯片的結(jié)構(gòu)特征

FLASH存儲器種類多樣,其中最為常用的為NOR型和NAND型FLASH。通常,NOR型比較適合存儲程序代碼,其隨機讀寫速度快,但容量一般較小(比如小于32 MB),且價格較高;而NAND型容量可達lGB以上,價格也相對便宜,適合存儲數(shù)據(jù),但一般只能整塊讀寫數(shù)據(jù),隨機存取能力差。它們對數(shù)據(jù)的存取不是使用線性地址映射,而是通過寄存器的操作串行存取數(shù)據(jù)。

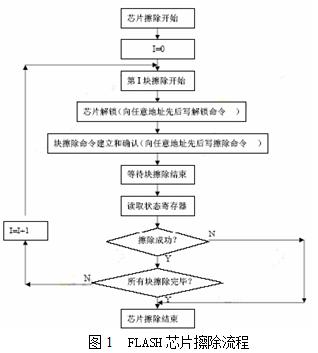

一般來說,不論哪種類型的FLASH,都有一個ID寄存器,用來讀取存儲器信息,可根據(jù)供應商提供的芯片資料進行具體的類型判斷。另外,F(xiàn)LASH存儲器的擦除過程相對費時,且擦除流程相對復雜。圖1為FLASH芯片擦除的一般流程。

|

可見,擦除數(shù)據(jù)的操作限制了FLASH芯片的工作速度。此外,其他一些特性,比如讀寫速度慢、寫數(shù)據(jù)之前要先寫入狀態(tài)字、很多FLASH都設有冗余單元等等,這些特點都制約了測試速度的提高。因此,設計合理的方法,或?qū)讐KFLASH并測,并且應用測試算法減少測試時間就顯得十分必要。

3.系統(tǒng)連接

本文選用的芯片為AMD公司的NOR型FLASH——Am29LV400B及三星公司的NAND型FLASH K9F5608UOB,它們都可通過44 PIN專用適配器和數(shù)字電路測試儀的數(shù)字通道直接相連。我們所采用的硬件實驗平臺是北京自動測試技術(shù)所開發(fā)的BC3192數(shù)模混合測試系統(tǒng),該系統(tǒng)可提供工作速度快,算法圖形產(chǎn)生方式靈活,非常適合測試需要。

4.測試實現(xiàn)方法

假設存儲器可選址的存儲單元數(shù)為N,由于存儲器芯片每次只能訪問一個存儲單元,每個單元只有“0”或“1”兩種狀態(tài),所以所有可能出現(xiàn)的狀態(tài)共2N種。由于選取的地址又是隨機的,所以,當測試步數(shù)為M時,選址序列組合可能有2N NM種之多。即使采用全“0”或全“1”兩種圖案測試,總的測試圖形也將有2NM種,這是個巨大的數(shù)字。

為了能夠有效地檢測存儲器芯片,必須分析半導體存儲器的結(jié)構(gòu),確定和選擇幾種能夠有效檢驗存儲器功能的圖形,使之既能達到檢測目的,又使測試量限定在允許范圍之內(nèi)。但實際應用中,由于每種測試圖形都有其局限性,再加上各個生產(chǎn)廠家以及各種型號存儲器的特性不完全一致,現(xiàn)在還沒有最佳的統(tǒng)一測試方法。

根據(jù)FLASH芯片的特點,我們主要改進并使用了以下幾種辦法:

4.1 奇偶校驗圖形檢驗法

奇偶校驗圖形檢驗法[6]是一種比較適合存儲器測試的方法。在奇偶性圖形檢驗法中,向存儲單元矩陣寫入的數(shù)據(jù)圖案是根據(jù)存儲單元選址地址碼的奇偶性而定的。如果存儲單元的行地址碼和列地址碼中有偶數(shù)個1,其奇偶性為0,則在該存儲單元中寫入“0”(或“1”);如果有奇數(shù)個1,其奇偶性為1,則在該存儲單元中寫入“1”(或“0”);存儲單元矩陣存入的信號數(shù)據(jù)將是行地址碼和列地址碼之間的異或關(guān)系。

FLASH芯片奇偶性圖形功能檢測的流程是:首先根據(jù)算法寫入背景圖形,然后逐位讀出并檢驗結(jié)果的正確性,再將芯片數(shù)據(jù)擦除,以反碼圖形重復上述測試過程。其總的測試步數(shù)為M=4N。

由于奇偶性圖形是不對稱的,任何一位的地址譯碼器失效都會引起本應寫入互為反碼數(shù)據(jù)的兩個存儲單元之一重復選址,并且第二次選址改變了第一次選址時寫入的內(nèi)容,而另一個存儲單元未被訪問。因此地址奇偶性圖形可以很好地檢驗出地址譯碼器的故障。

奇偶性圖形每次都把整個存儲器單元寫完后再整體讀出,沒有反復擦除的過程(整個過程只需擦除兩次),非常適用于FLASH芯片測試。

4.2 齊步法

齊步法[6]是對存儲器的每個單元依次進行檢驗的一種方法。首先從第一個存儲單元開始,逐個對每個單元進行取反和檢驗,直到最后一個單元檢測結(jié)束才完成一遍掃描。然后,在背景為反碼的情況下,從第一個存儲單元開始,逐個對每個單元進行取反和檢驗,直到最后一個單元檢測結(jié)束。整個過程就像所有單元一起向前走步一樣,因此稱為“齊步法”。根據(jù)FLASH芯片特點,我們改變在反碼背景條件下走步的過程,把它改造如下,形成了適合的齊步算法。

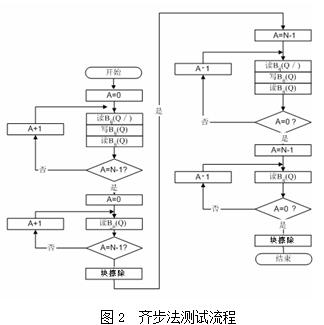

在圖2中給出了測試FLASH齊步法的測試流程:

|

在測試之前,每個存儲單元具有信息“1”。首先在存儲矩陣中寫入背景圖案(初始狀態(tài)為全“1”),然后從地址A0開始選址進行讀“1”,寫“0”,讀“0”操作,并檢驗讀出結(jié)果。接著,依次到下一個選址單元重復該操作(讀“1”,寫“0”,讀“0”),直到全部存儲單元(A=N-1)重復完為止。再在讀操作方式下對全部存儲單元進行一次正向掃描讀出,檢查有無正向?qū)Ψ聪虻亩嘀貙懭雴栴}。然后將存儲器輸入擦除,使之全部單元為全“1”。進而開始反向掃描:從最高地址AN-1開始執(zhí)行讀“1”,寫“0”,讀“0”操作,逐位進行上述操作過程,直至最終地址為AN-1,最后對全部存儲單元進行讀“0”掃描,以檢驗讀出結(jié)果的正確性。

用這種測試算法檢測存儲芯片,可使每個存儲單元都被訪問。既能保證每個存儲單元都能存儲“1”和“0”數(shù)據(jù),又能保證每個存儲單元都受到周圍其他單元的讀“1”、讀“0”和寫“1”、寫“0”的打擾。齊步法總的測試步數(shù)為:

式(3)中,W表示寫操作,R表示讀操作,Q表示“1”, 表示“0”。Bij表示存儲器第i行j列的存儲單元。如WBij(Q)就表示對第i行j列的存儲單元進行寫“1”操作所用的時間。

由式(3)可知,其測試步數(shù)共9N,且整個過程只需兩次擦除操作,可見它是一種即快速又有效的方法。

4.3 移動變反法

移動變反測試法[6]是按順序變反每個地址存儲單元數(shù)據(jù)的方法。它需要在變反前后讀出每個存儲單元的數(shù)據(jù),而且,還必須借助于前進和后退的地址尋址序列產(chǎn)生地址跳躍,地址以20、21…、2n-1次方的增量變化(n是地址位數(shù))。按照以上規(guī)律進行地址跳變后,再對每個地址進行三次操作:讀、寫和讀即可完成一個循環(huán)。

以上操作的目的主要在于地址間產(chǎn)生有效相互打擾,但顯然如果以整個芯片為單元進行上述操作需要多次擦除數(shù)據(jù),因此對FLASH測試芯片應做如此改進:以扇區(qū)為單元完成操作。假設FLASH芯片有N個扇區(qū),移動變反法的功能測試先要以“1”為背景圖案寫入全部存儲單元。首先,在第一個扇區(qū),對A0存儲單元讀出并驗證是“1”,再將該存儲單元改寫成“0”,最后讀出該存儲單元的信息以證明新寫入的“0”仍存于該存儲單元中。第一扇區(qū)測試地址按有效位的階20遞增,對每個存儲單元都要重復上述的讀“1”,寫“0”讀“0”的操作過程,需要測試步長為3n(n為該扇區(qū)的存儲單元數(shù))才能使全部的存儲單元都變成“0”。這次測試的地址序列是遞增1的,即由地址最低位A0增加到最高位A(n-1),對A(n-1)存儲單元進行讀“1”,寫“0”和讀“0”驗證。

對第二個扇區(qū),以下一個地址階21作為地址增量的變化量,每次用不同的地址位作為最低位(分別為第0位和第1位),使地址以此增量的變化通過所有可能的地址。因此在一次測試程序中所有地址的存儲單元都被測試一次。

然后,依次以22、24…2N作為地址增量,重復上述過程,每完成一個循環(huán)便產(chǎn)生一個循環(huán)進位。

由于各個扇區(qū)的大小不同,移動變反法功能測試圖形步長為3n(n為最大扇區(qū)存儲單元個數(shù))。以扇區(qū)為單元的測試實際上是一種對芯片功能的抽測,因為它并沒有進行對各單元存取數(shù)據(jù)進行反復打擾,以驗證其地址線間信號改變所帶來的影響,但這種方法分別在各個扇區(qū)對鄰近地址線一一做了打擾測試,由于各個扇區(qū)結(jié)構(gòu)根本上是相同的,因此這種抽測很有代表性,并且把測試時間減少了一個數(shù)量級。

移動變反法測試圖形是一種良好的折衷測試方案。因為它幾乎具有各種測試圖形的最好特點,可以用較少的試驗步數(shù)測試盡可能多的存儲單元間打擾的相互影響。在具體程序中,“1”場變反為“0”場是按序選擇地址,并通過寫入這些地址而產(chǎn)生的,在兩次讀出之間有一次寫操作。移動變反法測試包括了功能測試和動態(tài)測試,功能測試保證被測存儲單元不受讀、寫其他存儲單元的影響,動態(tài)測試預測最壞和最好條件下的取數(shù)時間,并預測地址變換對這些時間的影響。

這種測試方法易于實現(xiàn),它是在跳步算法[1]的基礎上,通過改變跳步的長度,減小了算法的復雜度。移動變反法測試是一種具有良好功能測試和動態(tài)測試特點的測試圖形,并且所需的測試時間較短,在很多情況下都有很好的效果。尤其是對于較大容量存儲器的測試,該方法特別有效。

移動變反法還可以作進一步擴展,即對數(shù)據(jù)做移動變反處理。以芯片為32位總線為例,首先對存儲器各單元寫入0xAAAAAAAA,檢驗并擦除,然后對存儲器寫入0xCCCCCCCC,檢驗并擦除,以后依次寫入0xF0F0F0F0,0x0F0F0F0F,0xFF00FF00,0x00FF00FF,0xFFFF0000,0x0000FFFF, 0xFFFFFFFF,0x0,都在檢驗所寫的正確性后再擦除數(shù)據(jù)。其原理與地址移動變反相同,在此不再贅述。

4.測試方法的綜合使用和流水測試

以上,從算法的角度上提高了FLASH芯片的可測性。雖然NOR、NAND型FLASH結(jié)構(gòu)不同,但由于以上算法都可通過計算,順序產(chǎn)生測試圖形,因此可通用于以上兩類器件的測試中。

上述三種方法各有優(yōu)點,在實際應用中可配合使用。地址奇偶性圖形測試最為方便高效,因為在寫入圖形過程中每次只改變一位地址線,而且寫入的是相反的數(shù)據(jù),所以如果哪一位地址線出現(xiàn)短路立刻會被檢查出來,使用該方法最適宜檢驗地址譯碼器的故障。齊步法適于用來檢驗多重地址選擇與譯碼器的故障,并且可以檢測寫入時噪聲對存儲芯片特性的影響,它能保證正確的地址譯碼和每個存儲單元存儲“1”和“0”信息的能力。在大多數(shù)生產(chǎn)測試中,聯(lián)合使用這兩種方法可以判別出FLASH絕大多數(shù)的故障。當然,各個廠家生產(chǎn)的芯片在結(jié)構(gòu)和工藝上有一定區(qū)別,因此出現(xiàn)各種錯誤的概率也不同,可以根據(jù)實際情況調(diào)整方法。由于設計問題,有些芯片還有可能出現(xiàn)其他一些不太常見的錯誤,這就需要進行更詳盡的測試,這時使用移動變反測試法就比較合適。這種方法可以很好地測試芯片的動態(tài)錯誤,并且可根據(jù)具體需要詳細展開測試或簡化測試,對于產(chǎn)品性能分析十分有效。

在具體程序設計時,為簡化算法執(zhí)行,可以將讀取產(chǎn)品型號、調(diào)用讀寫命令的語句作為子程序存儲在測試儀中,每次需要時都可以無縫調(diào)用。

在測試過程中,最耗費時間的是程序擦除操作,一次擦除往往就需要幾秒,其解決辦法是將擦除工序單獨處理。在實際應用中,可使用兩臺測試儀,其中,在擦除時幾個芯片并行運行。這樣,一臺設備用于讀、寫、測試,另一臺設備用于擦除數(shù)據(jù),就可以有效地形成流水線操作,大大節(jié)省測試時間。此外,將幾種方法綜合使用,還有助于提高故障覆蓋率。

5.實驗結(jié)果

根據(jù)上述思想,我們在國產(chǎn)BC3192的測試系統(tǒng)平臺[7][8]上,對AMD公司的NOR型FLASH——Am29LV400B及三星公司的NAND型FLASH——9F5608UOB都進行了測試。實驗表明,和傳統(tǒng)的以棋盤格為基礎的測試圖形[1]相比,奇偶校驗法、齊步法和移動變反法產(chǎn)生的測試圖形故障覆蓋率更高,這些算法由于最多只有兩次芯片擦除操作,所以測試時間完全能符合工程測試需要,其中,移動變反法沒有擦除操作,所以測試速度最快。在實驗中,我們采用上述三種方法中任意一種,按照流水的方法測試,在相同故障覆蓋率下,都可以使測試效率可提高40%以上。

6.結(jié)論

本文是在傳統(tǒng)存儲器測試理論基礎上對FLASH測試的嘗試,該方法保留了傳統(tǒng)方法的優(yōu)點,較好地解決了FLASH存儲器測試的困難。該方法方便快捷,流程簡單,所有測試圖形都可以事先生成,這樣就可以直接加載到測試儀中,有利于直接應用于測試儀進行生產(chǎn)測試。