??? 摘 要: 針對(duì)特定環(huán)境(車內(nèi)空間)內(nèi)的聲場(chǎng)重建,給出了聲效處理器的硬件設(shè)計(jì)方案。以TI公司的數(shù)字信號(hào)處理器TMS320VC5402為硬件中心,對(duì)聲音信號(hào)進(jìn)行算法處理;串行16位模數(shù)轉(zhuǎn)換芯片AD1870實(shí)現(xiàn)對(duì)音頻信號(hào)" title="音頻信號(hào)">音頻信號(hào)的采集;串行數(shù)模轉(zhuǎn)換" title="數(shù)模轉(zhuǎn)換">數(shù)模轉(zhuǎn)換芯片AD1858完成對(duì)處理后的音頻信號(hào)的輸出。詳細(xì)敘述了TMS320VC5402和AD1870、AD1858之間的連接和時(shí)序。實(shí)驗(yàn)表明,此系統(tǒng)可靠、穩(wěn)定,為完成音頻信號(hào)的實(shí)時(shí)編解碼提供了硬件支持,使在非規(guī)范空間播放高品質(zhì)立體聲音效成為可能。

??? 關(guān)鍵詞: 聲場(chǎng)重建? 聲效處理? 數(shù)字信號(hào)處理

?

??? 隨著現(xiàn)代科技的迅猛發(fā)展,立體聲音頻制作系統(tǒng)日臻完美,聲場(chǎng)的信息幾乎被全部收集。由于大部分放音聲學(xué)環(huán)境不可能像錄制環(huán)境那么完善,這些“聲音畫面”的恢復(fù)就成為研究的難點(diǎn)[1]。在大空間放音環(huán)境中(如露天環(huán)境),需要大量的放聲設(shè)備來完成對(duì)聲場(chǎng)的重建。因?yàn)檫@些設(shè)備占用了很多空間,阻礙了這種技術(shù)在小空間放音環(huán)境(如車內(nèi)環(huán)境)下的應(yīng)用。這些小空間放音環(huán)境的聲場(chǎng)效果的采集、傳輸、恢復(fù)與重建是音頻信號(hào)處理的研究熱點(diǎn)[2]。從經(jīng)過傳輸混疊的雙聲道信號(hào)重建模擬聲效是電聲技術(shù)的核心,本文據(jù)此設(shè)計(jì)了一種基于數(shù)字信號(hào)處理器(DSP)的音頻實(shí)時(shí)處理的硬件系統(tǒng)[3-5]。本系統(tǒng)可以用來對(duì)立體聲音頻信號(hào)進(jìn)行實(shí)時(shí)編解碼與特定環(huán)境(車內(nèi)空間)下聲場(chǎng)效果重現(xiàn)處理,還可以用作同步的實(shí)時(shí)信號(hào)采集與處理。

1 聲效處理器的DSP實(shí)現(xiàn)

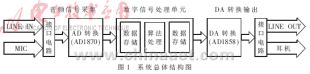

??? 本系統(tǒng)由TMS320VC5402[6](以下簡(jiǎn)稱C5402)芯片、閃存(Flash)、雙通道隨機(jī)存儲(chǔ)器(DRAM)、模數(shù)轉(zhuǎn)換電路、數(shù)模轉(zhuǎn)換電路和電平轉(zhuǎn)換芯片等組成。系統(tǒng)框圖如圖1所示。

???????????????????

????由麥克或數(shù)據(jù)線傳來模擬聲音信號(hào),首先經(jīng)過ADC(AD1870)進(jìn)行采集轉(zhuǎn)換,轉(zhuǎn)換后的數(shù)字音頻信號(hào)通過串行方式傳入DSP單元,DSP單元對(duì)接收的數(shù)字音頻信號(hào)進(jìn)行存儲(chǔ)、運(yùn)算、再存儲(chǔ)等一系列處理,處理后的數(shù)字音頻信號(hào)通過串口" title="串口">串口傳給DAC(AD1858),AD1858完成對(duì)音頻信號(hào)的恢復(fù),把數(shù)字音頻信號(hào)轉(zhuǎn)換為模擬聲音信號(hào),DA轉(zhuǎn)換后模擬聲音信號(hào)通過接口電路傳給耳機(jī)輸出或通過數(shù)據(jù)線由放音設(shè)備輸出。從而實(shí)現(xiàn)對(duì)音頻信號(hào)的采集、傳輸、恢復(fù)與重建,完成了對(duì)聲音效果的處理。

??? 其中DSP芯片C5402具有100MIPS的運(yùn)算速度,配有專用的硬件乘法-累加器,可以進(jìn)行高速實(shí)時(shí)運(yùn)算,為音頻數(shù)字信號(hào)的實(shí)時(shí)編解碼提供了高速、可靠的硬件基礎(chǔ);在對(duì)音頻信號(hào)處理時(shí)會(huì)產(chǎn)成緩存數(shù)據(jù),這些數(shù)據(jù)需要占有大量的存儲(chǔ)空間,雙口RAM則主要負(fù)責(zé)數(shù)據(jù)的存儲(chǔ);模數(shù)、數(shù)模轉(zhuǎn)換的實(shí)現(xiàn)在本系統(tǒng)中選用的是AD公司的音頻專用芯片:模數(shù)轉(zhuǎn)換芯片AD1870、數(shù)模轉(zhuǎn)換芯片AD1858。它們具有轉(zhuǎn)換速度快、采樣頻率符合聲音信號(hào)的要求、串行傳輸數(shù)據(jù)、無軟件控制寄存器、操作簡(jiǎn)單等特點(diǎn)。

2 ADC、DAC與DSP的硬件連接與工作時(shí)序

??? DSP芯片C5402具有兩個(gè)獨(dú)立的多功能串口McBSP0、McBSP1,在此聲效處理系統(tǒng)中被用來分別與AD1870和AD1858通信。下面詳細(xì)介紹它們之間的連接和工作時(shí)序。

2.1 DSP串口與AD1870的連接

??? 在本設(shè)計(jì)中,ADC與DSP以及DSP與DAC之間的通信采用的都是串行傳輸方式,C5402芯片內(nèi)部集成了兩個(gè)高速、雙向、多通道帶緩沖串行端口McBSP[7],每個(gè)串口提供了6個(gè)功能引腳和多個(gè)可程序讀寫的寄存器。C5402內(nèi)部CPU通過對(duì)這些控制寄存器的讀寫完成數(shù)據(jù)的發(fā)送、接收以及對(duì)數(shù)據(jù)傳輸時(shí)序的控制。6個(gè)功能引腳分別為:

??? (1)接收、發(fā)送引腳DR、DX;

??? (2)接收、發(fā)送時(shí)鐘引腳CLKR、CLKX;

??? (3)接收、發(fā)送幀同步引腳FSR、FSX。

??? AD1870[8]是一個(gè)基于Σ-Δ技術(shù)的高速串行16位模數(shù)轉(zhuǎn)換芯片,主要用于雙聲道音頻模擬量的采集。AD1870可以以48kHz、44.1kHz、32kHz等三種采樣頻率對(duì)音頻模擬量進(jìn)行采集。主要的引腳有:

??? (1)VINL、VINR——左右聲道模擬聲音信號(hào)的輸入引腳;

??? (2)BCLK、L CLK——位時(shí)鐘、左右時(shí)鐘;

CLK——位時(shí)鐘、左右時(shí)鐘;

??? (3)WCLK——字時(shí)鐘;

??? (4)SOUT——串行數(shù)據(jù)輸出引腳;

??? (5)RDEDGE——讀邊沿的極性選擇引腳;

??? (6) ——復(fù)位引腳。

——復(fù)位引腳。

?其他的引腳還有:

??? (1)CLKIN為模數(shù)轉(zhuǎn)換器AD1870的工作時(shí)鐘輸入端,fCLKIN=384×fS或者fCLKIN=256×fS;

??? (2)引腳384/ 用來選擇采用上述兩種模式的哪一種,如果384/

用來選擇采用上述兩種模式的哪一種,如果384/ =HI,則選用384模式;如果384/

=HI,則選用384模式;如果384/ =LO,則選用256模式;

=LO,則選用256模式;

??? (3)引腳S/ 、RLJUST、

、RLJUST、 用來設(shè)置AD1870數(shù)據(jù)傳輸模式,AD1870提供了8種數(shù)據(jù)傳輸模式,其中5種AD1870用做主設(shè)備,3種AD1870用做從設(shè)備。

用來設(shè)置AD1870數(shù)據(jù)傳輸模式,AD1870提供了8種數(shù)據(jù)傳輸模式,其中5種AD1870用做主設(shè)備,3種AD1870用做從設(shè)備。

??? 結(jié)合本系統(tǒng)的應(yīng)用,經(jīng)過分析把AD1870作為從設(shè)備使用,它們之間的連接如圖2所示。C5402的串口McBSP0用以和AD1870通信。C5402的主時(shí)鐘輸出引腳CLKOUT和AD1870的CLKIN引腳,這樣由DSP處理單元向AD1870提供工作時(shí)鐘。選用AD1870工作在從模式、32位數(shù)據(jù)傳送格式[5],需要做如下設(shè)置:S/ =HI、LRJUST=LO、

=HI、LRJUST=LO、 =LO。在這種模式下,要求fLRJUST=fBCLK/32,即在兩個(gè)左右時(shí)鐘LRJUST脈沖之間位時(shí)鐘BCLK要經(jīng)歷32個(gè)周期。每一位時(shí)鐘BCLK周期時(shí)間傳送一位數(shù)據(jù),共傳送32位數(shù)據(jù),其中前16位為左聲道的數(shù)據(jù),后16位為右聲道的數(shù)據(jù)。根據(jù)這種要求把C5402的BCLKXO、BCLKRO與AD1870的BCLK連在一起,由BCLKXO向BCLKRO和BCLK提供位時(shí)鐘信號(hào)" title="時(shí)鐘信號(hào)">時(shí)鐘信號(hào);把C5402的BFSX0、BFSR0與AD1870的LRCLK連在一起,由BFSX0向BFSR0和LRCLK提供頻率為時(shí)鐘信號(hào)頻率的1/32的左右時(shí)鐘信號(hào);把C5402的BDR0和AD1870的SOUT連在一起,這樣C5402就可以接收來自AD1870的數(shù)字音頻信號(hào)了,C5402的接收數(shù)據(jù)引腳接收來自AD1870串行數(shù)據(jù)輸出引腳輸出的數(shù)字音頻信號(hào)。為滿足數(shù)據(jù)傳輸要求需要對(duì)McBSP0的串口寄存器進(jìn)行設(shè)置,主要設(shè)置如下:

=LO。在這種模式下,要求fLRJUST=fBCLK/32,即在兩個(gè)左右時(shí)鐘LRJUST脈沖之間位時(shí)鐘BCLK要經(jīng)歷32個(gè)周期。每一位時(shí)鐘BCLK周期時(shí)間傳送一位數(shù)據(jù),共傳送32位數(shù)據(jù),其中前16位為左聲道的數(shù)據(jù),后16位為右聲道的數(shù)據(jù)。根據(jù)這種要求把C5402的BCLKXO、BCLKRO與AD1870的BCLK連在一起,由BCLKXO向BCLKRO和BCLK提供位時(shí)鐘信號(hào)" title="時(shí)鐘信號(hào)">時(shí)鐘信號(hào);把C5402的BFSX0、BFSR0與AD1870的LRCLK連在一起,由BFSX0向BFSR0和LRCLK提供頻率為時(shí)鐘信號(hào)頻率的1/32的左右時(shí)鐘信號(hào);把C5402的BDR0和AD1870的SOUT連在一起,這樣C5402就可以接收來自AD1870的數(shù)字音頻信號(hào)了,C5402的接收數(shù)據(jù)引腳接收來自AD1870串行數(shù)據(jù)輸出引腳輸出的數(shù)字音頻信號(hào)。為滿足數(shù)據(jù)傳輸要求需要對(duì)McBSP0的串口寄存器進(jìn)行設(shè)置,主要設(shè)置如下:

??? (1)串口引腳控制寄存器PCR:FSXM(11)=1;FSRM(10)=0;CLKXM(9)=1;CLKRM(8)=0

??? (2)接收控制寄存器RCR1:RFRLEN1(14-8)=0000001;RWDLEN(7-5)=010。

???????????????????????????

??? 在數(shù)據(jù)傳送期間AD1870的字時(shí)鐘WCLK一直輸出高電平,據(jù)此把C5402的通用IO口 與它連在一起,用于DSP單元檢測(cè)AD1870是否工作。另外,C5402的通用IO口XF與AD1870的

與它連在一起,用于DSP單元檢測(cè)AD1870是否工作。另外,C5402的通用IO口XF與AD1870的 直接連接,這樣就可以對(duì)AD1870進(jìn)行軟件復(fù)位操作。

直接連接,這樣就可以對(duì)AD1870進(jìn)行軟件復(fù)位操作。

2.2 AD1870到C5402工作時(shí)序

??? 從AD1870到TMS320VC5402的數(shù)據(jù)傳輸工作時(shí)序如圖3所示。由圖可知,在接電源后C5402通過主時(shí)鐘輸出引腳CLKOUT向AD1870的工作時(shí)鐘輸入引腳發(fā)送工作時(shí)鐘,AD1870開始工作,把模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),即把左右聲道模擬聲音信號(hào)的輸入引腳VINL、VINR采集來的模擬聲音信號(hào)轉(zhuǎn)換為數(shù)字音頻信號(hào)。同時(shí)C5402的CPU通過對(duì)串口McBSP0寄存器的讀寫使串口McBSP0通過發(fā)送時(shí)鐘引腳BCLX0向C5402的接收時(shí)鐘引腳BCLR0和AD1870的位時(shí)鐘引腳BCLK發(fā)送位時(shí)鐘;通過發(fā)送幀同步引腳BFSX0向C5402的接收幀同步引腳BFSR0和AD1870的左右時(shí)鐘引腳發(fā)送左右時(shí)鐘。按照?qǐng)D3所示的時(shí)序數(shù)字音頻信號(hào)由AD1870向DSP單元傳送:在第一個(gè)左右時(shí)鐘脈沖的觸發(fā)下,第一幀數(shù)據(jù)開始向DSP單元傳送,共32位數(shù)據(jù)。首先傳送的是左聲道的第一幀數(shù)據(jù)(16位);然后傳送右聲道的第一幀數(shù)據(jù)。接著出現(xiàn)第二個(gè)左右時(shí)鐘脈沖,第二幀數(shù)據(jù)也是按照先前的順序傳入DSP單元。數(shù)據(jù)按照這種模式連續(xù)傳向DSP單元。

?????????????????????????????

2.3 DSP串口與AD1858的連接

??? 在DSP單元處理好的音頻數(shù)字信號(hào)需要經(jīng)過數(shù)模轉(zhuǎn)換,轉(zhuǎn)換成模擬聲音量輸出。本系統(tǒng)選用的數(shù)模轉(zhuǎn)換芯片是同為AD公司生產(chǎn)的AD1858數(shù)模轉(zhuǎn)換芯片。AD1858[9]是一個(gè)雙通道高速串行DA轉(zhuǎn)換芯片,用于對(duì)數(shù)字音頻信號(hào)的數(shù)模轉(zhuǎn)換。主要引腳有:

??? (1)SDATA——串行輸入引腳;

??? (2)BCLK、LRCLK——位時(shí)鐘、左右時(shí)鐘;

??? (3)MODE——輸入串行數(shù)據(jù)模式控制;

??? (4) ——上電/復(fù)位引腳;

——上電/復(fù)位引腳;

??? (5)MUTE——利用此引腳可以控制數(shù)模轉(zhuǎn)換通路的通和斷;

??? (6)MCLK——主時(shí)鐘輸入;

??? (7)OUTL、OUTR——左右聲道輸出引腳;

??? (8)MCLK為數(shù)模轉(zhuǎn)換器AD1858的工作時(shí)鐘輸入端,fMCLK=384×fS或者fMCLK= ×fS;

×fS;

??? (9)引腳384/256用來選擇采用上述兩種模式的哪一種。如果384/ =HI,選用384模式;如果384/256=LO,選用256模式;

=HI,選用384模式;如果384/256=LO,選用256模式;

?? ?(10)MODE用來設(shè)置AD1858數(shù)據(jù)接收模式,AD1858提供了二種數(shù)據(jù)傳輸模式。

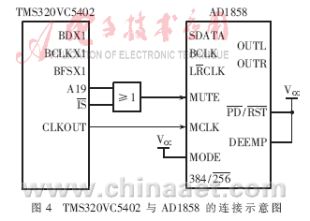

??? 與C5402的連接如圖4所示。由圖可知,C5402的串口McBSP1用以和AD1858通信。C5402的主時(shí)鐘輸出引腳CLKOUT和AD1858的MCLK引腳,由DSP處理單元向AD1858提供工作時(shí)鐘。將AD1858的引腳MODE接高電平,使AD1858工作在L-J DSP串行口模式[6]。這種工作模式要求fLRCLK≤fBLCK/16,即在兩個(gè)LRCLK脈沖之間BCLK要經(jīng)歷多于16個(gè)周期。每一BCLK周期時(shí)間傳送一位數(shù)據(jù),共傳送16位數(shù)據(jù),在16位數(shù)據(jù)傳送完后等待下一個(gè)幀脈沖。在第一個(gè)幀同步脈沖到來時(shí),傳送左聲道的16位數(shù)據(jù),下一個(gè)幀同步脈沖,傳送右聲道的16位數(shù)據(jù),這樣在LRCLK時(shí)鐘的調(diào)節(jié)下依次輪流進(jìn)行傳送左右聲道的數(shù)據(jù)。根據(jù)這種要求把C5402的BCLKX1與AD1858的BCLK連在一起,由BCLKX1向BCLK提供位時(shí)鐘信號(hào);把C5402的BFSX0與AD1858的LRCLK連在一起,由BFSX0向LRCLK提供頻率為時(shí)鐘信號(hào)頻率1/16的左右時(shí)鐘信號(hào);把C5402的BDX1和AD1858的SDATA連在一起,這樣C5402就可以把經(jīng)過算法處理的數(shù)字音頻信號(hào)傳送給AD1858了。為了使數(shù)據(jù)傳輸需要對(duì)McBSP1的串口控制寄存器進(jìn)行設(shè)置,設(shè)置如下:

?? ?(1)串口引腳控制寄存器PCR:FSXM(11)=1;CLKXM(9)=1;

??? (2)發(fā)送控制寄存器XCR1:XFRLEN1=0000000;XWDLEN1=010。

??????????????????????

??? 另外,C5402的A19、IS通過或門與AD1858的引腳MUTE連接,這樣C5402就可以軟件控制數(shù)模轉(zhuǎn)換的開啟與關(guān)閉了。

2.4 C5402到AD1858時(shí)序邏輯

??? 由C5402到AD1858的工作時(shí)序如圖5所示。由圖可知,上電以后AD1858開始工作。DSP單元中處理好的音頻數(shù)字量在時(shí)鐘調(diào)節(jié)下向AD1858傳送,在第一個(gè)左右時(shí)鐘脈沖的的觸發(fā)下,數(shù)據(jù)開始傳送,AD1858根據(jù)左右時(shí)鐘先接收左聲道的一幀數(shù)據(jù)(16位)轉(zhuǎn)化為模擬量由OUTL引腳輸出;然后出現(xiàn)第二個(gè)左右脈沖,AD1858接著接收右聲道的一幀數(shù)據(jù),數(shù)模轉(zhuǎn)換后由OUTR引腳輸出模擬聲音信號(hào)。接著出現(xiàn)第三個(gè)左右脈沖,第二幀左聲道的數(shù)據(jù)也是按照先前的順序傳入AD1858進(jìn)而進(jìn)行數(shù)模轉(zhuǎn)換,數(shù)模轉(zhuǎn)換依次進(jìn)行下去。

?????????????????????????

2.5 電平匹配

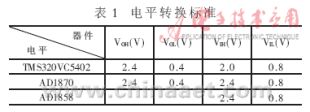

??? 在設(shè)計(jì)DSP硬件系統(tǒng)時(shí),由于DSP芯片C5402的I/O工作電壓是3.3V,而ADC芯片AD1870和DAC芯片DA1858的工作電壓卻是5V,因此要分析它們之間的電平轉(zhuǎn)換標(biāo)準(zhǔn),以滿足電壓的兼容性和接口條件。電平轉(zhuǎn)換標(biāo)準(zhǔn)從器件的電氣特性中獲得,如表1所示。

????????????????????????????????

??? 由表1可知,C5402與AD1870和AD1858的電平轉(zhuǎn)換標(biāo)準(zhǔn)是一致的,因此從C5402到AD1870和AD1858的時(shí)鐘、數(shù)據(jù)線可以直接連接。但是,由于C5402不能承受5V的電壓,因此從AD1870到C5402的數(shù)據(jù)線不能直接相連,解決的辦法是在它們之間加入一個(gè)3.3V電壓供電并能承受5V電壓的緩沖器SN74LVC245A[10]。SN74LVC245A有8路數(shù)據(jù)通道,引腳DIR用來控制數(shù)據(jù)的傳輸方向,SN74LVC245A的接口示意見圖2,基本功能如表2所示。

??????????????????????????????????

3 工作流程

??? 綜上所述,系統(tǒng)上電后,AD1870啟動(dòng)開始模數(shù)轉(zhuǎn)換,DSP單元開始向AD1870和AD1858輸出時(shí)鐘信號(hào),由C5402的串口McBSP0向AD1870發(fā)送左右時(shí)鐘信號(hào),數(shù)據(jù)開始傳輸;根據(jù)位時(shí)鐘的調(diào)節(jié),AD1870連續(xù)向DSP單元傳送數(shù)據(jù),在DSP單元內(nèi)數(shù)據(jù)經(jīng)過緩存、算法處理,最后處理好的數(shù)據(jù)存在固定的數(shù)據(jù)空間;這時(shí)串口McBSP1向AD1858發(fā)送的左右時(shí)鐘信號(hào),信號(hào)啟動(dòng)向AD1858傳輸數(shù)據(jù);同樣根據(jù)串口McBSP1送給AD1858 BCLK的位時(shí)鐘,AD1858連續(xù)接收DSP單元傳過來的數(shù)據(jù),進(jìn)行數(shù)模轉(zhuǎn)換,模擬聲音量由引腳OUTL、OUTR輸出。

??? 該系統(tǒng)設(shè)計(jì)已通過實(shí)驗(yàn)運(yùn)行驗(yàn)證,達(dá)到了相應(yīng)的設(shè)計(jì)要求,可用于不規(guī)范空間聲場(chǎng)效果的恢復(fù)。

參考文獻(xiàn)

[1] 惠特克 J.C.數(shù)字音頻技術(shù)寶典[M].北京:科學(xué)出版社,2004.

[2] 莫偉源.音響技術(shù)在汽車中的應(yīng)用[J].音響技術(shù),2006(1):68-69.

[3] 周霖.算法設(shè)計(jì)與系統(tǒng)方案[M].北京:國(guó)防工業(yè)出版社,2004.

[4] 王建平.基于DSP的多路音/視頻采集處理系統(tǒng)設(shè)計(jì)[J].國(guó)外電子元器件,2006,(6):27-31.

[5] 劉耦耕.語音信號(hào)變速算法及其TMS320C5402實(shí)時(shí)實(shí)現(xiàn)[J].中南大學(xué)學(xué)報(bào)(自然科學(xué)版),2004,35(1):117-121.

[6] TMS320VC5402 fixed-point digital signal processor.Texas?Instruments Incorporated,2000.

[7] 鄒彥.DSP原理及應(yīng)用[M].北京:電子工業(yè)出版社,2005.

[8] Single-Supply 16-Bit Σ-Δ Stereo ADC AD1870.Analog?Device,Inc,2001.

[9] Stereo,Single Supply 16-,18- and 20-Bit Sigma-Delta?DACs AD1857/AD1858.Analog Device,Inc,2001.

[10] SN74LVC245 Aoctal bus transceiver with 3-state outputs.Texas Instruments Incorporated,1998.