??? 摘 要: 提出自適應(yīng)多速率寬帶語音編碼" title="語音編碼">語音編碼標(biāo)準(zhǔn)G.722.2,重點(diǎn)研究了建立在代數(shù)碼激勵(lì)線性基礎(chǔ)上的信源編碼技術(shù),簡單介紹了包括活動(dòng)語音檢測(cè)、舒適噪聲生成的源控制速率方案及錯(cuò)誤隱藏機(jī)制。針對(duì)G.722.2算法復(fù)雜度高的特點(diǎn),對(duì)TI公司的定點(diǎn)DSP TMS320VC5416的硬件原理進(jìn)行重點(diǎn)研究,給出了編解碼算法實(shí)現(xiàn)的軟件架構(gòu),分析了軟件實(shí)現(xiàn)流程。

??? 關(guān)鍵詞: 語音編碼? 自適應(yīng)多速率? 代數(shù)碼激勵(lì)線性預(yù)測(cè)? 源控速率

?

??? 脈沖編碼調(diào)制(PCM)原理的出現(xiàn)標(biāo)志著現(xiàn)代數(shù)字通信技術(shù)研究的開始。經(jīng)過半個(gè)多世紀(jì)的發(fā)展,數(shù)字通信系統(tǒng)以其在可靠性、抗干擾性、易集成性、保密性、交換速度和成本等方面的優(yōu)異性能取代了模擬通信系統(tǒng)。

??? 為壓縮語音編碼速率以提高通信系統(tǒng)的頻帶利用率,擴(kuò)大通信容量,ITU-T先后推出PCM、ADPCM、G.728、G.729、G.723.1等語音編碼標(biāo)準(zhǔn)。2001年,3GPP和ITU-T采納G.722.2為GSM、WCDMA和3G系統(tǒng)的語音編碼解碼" title="編碼解碼">編碼解碼標(biāo)準(zhǔn),2002年ITU-T又將其選為有線應(yīng)用的寬帶標(biāo)準(zhǔn)。

1 G.722.2寬帶語音編碼標(biāo)準(zhǔn)研究[1~7]

??? G.722.2寬帶語音編碼器是單個(gè)的集成語音編碼器,由9種速率模式組成,位速率分別為:23.85、23.05、19.85、18.25、15.85、14.25、12.65、8.85和6.6kbps。它包括活動(dòng)語音檢測(cè)(VAD)、舒適噪聲生成(CNG)以及對(duì)付傳輸錯(cuò)誤和丟包后的錯(cuò)誤隱藏機(jī)制組成。

1.1 編碼算法部分

??? G.722.2以代數(shù)碼激勵(lì)線性預(yù)測(cè)為基礎(chǔ),通過線性預(yù)測(cè)分析、基音預(yù)測(cè)分析和在12.8kHz采樣的固定碼本參數(shù)的分析,以期最小化感覺加權(quán)差信號(hào)。處理時(shí)以幀為單位,分析每幀語音抽取CELP參數(shù),除此還計(jì)算出23.85kbps模式下高帶增益索引值。

1.2 解碼算法部分

??? 主要解碼器發(fā)送的參數(shù)(包括LP參數(shù),自適應(yīng)碼本矢量和增益,固定碼本矢量和增益以及高帶增益),分析合成重構(gòu)語音。

1.3 源控制速率方案

??? 源控制速率的作用是讓語音編碼器用一個(gè)低速率來編碼只包含背景噪音的語音幀,而不是編碼所有的語音。在GSM中,將這種模式稱為DTX(非連續(xù)傳輸)控制和操作。編碼解碼器在采用這種模式編碼時(shí),位速率是1.75kbps。網(wǎng)絡(luò)可以調(diào)整其傳輸方案獲得可變速率。

1.4 丟幀/失幀錯(cuò)誤隱藏機(jī)制

??? 由于傳輸錯(cuò)誤,幀可能會(huì)出錯(cuò),而在無線網(wǎng)絡(luò)和包交換網(wǎng)絡(luò)還可能造成幀丟失。為了將單個(gè)錯(cuò)幀/失幀屏蔽,錯(cuò)幀/失幀發(fā)生時(shí)會(huì)通知語音解碼器,而后初始化錯(cuò)誤隱藏的過程。在語音合成時(shí)使用一組預(yù)測(cè)參數(shù),網(wǎng)絡(luò)通過設(shè)置被傳輸語音幀的類型標(biāo)志位來指明發(fā)生了錯(cuò)幀/失幀或者丟失SID幀。

2 TMS320VC5416的硬件平臺(tái)解決方案[8][9]

??? 采用 美國TI公司的54X系列定點(diǎn)DSP TMS320VC5416,具有低功耗、高性能等特點(diǎn)。

2.1 硬件平臺(tái)介紹

??? TMS320VC5416的主要特征有:

??? (1)優(yōu)化的CPU結(jié)構(gòu):增強(qiáng)的多總線結(jié)構(gòu),數(shù)據(jù)總線具有總線保持特性;40bit的算術(shù)邏輯單元(ALU),包括兩個(gè)獨(dú)立的40bit的累加器,一個(gè)40bit的桶形移位器;一個(gè)17×17的乘法器連接一個(gè)40bit專用加法器,可用來進(jìn)行非流水線式的單周期乘/累加(MAC)操作等。

??? (2)存儲(chǔ)器:擴(kuò)展地址模式可最大尋址8M×16bit" title="16bit">16bit;64K×16bit雙訪問片內(nèi)RAM;64K×16bit單訪問片內(nèi)RAM;16K×16bit片內(nèi)ROM。

??? (3)指令集:支持單指令循環(huán)和塊循環(huán)操作;塊存儲(chǔ)器傳送指令提供了高效的程序和數(shù)據(jù)存儲(chǔ)器管理;支持32bit長字操作;支持并行存儲(chǔ)/加載" title="加載">加載指令;支持條件存儲(chǔ)指令和中斷快速返回;支持定點(diǎn)DSP的C語言編譯器。

??? (4)片上硬件資源:軟件可編程等待狀態(tài)發(fā)生器和可編程存儲(chǔ)單元轉(zhuǎn)換;鎖相環(huán)(PLL)時(shí)鐘發(fā)生器;一個(gè)16bit定時(shí)器;三個(gè)多通道緩沖串口(McBSPs);六通道直接存儲(chǔ)訪問控制器;增強(qiáng)型8/16bit并行主機(jī)接口(HPI)。

??? (5)速度:在3.3V(內(nèi)核電壓1.6V)供電時(shí),執(zhí)行周期是6.25ns(160MIPS)。

??? (6)電源:功耗低,工作電源有3.3V、1.6V和1.5V(內(nèi)核電壓),用節(jié)電模式IDLE1、IDLE2、IDLE3指令作功率控制,可禁止CLKOUT。

2.2 直接存儲(chǔ)器訪問DMA

??? C5416的DMA擁有6個(gè)獨(dú)立的可編程通道,同時(shí)允許6個(gè)不同的DMA操作。DMA控制器可以在不影響CPU情況下,允許數(shù)據(jù)在片內(nèi)存儲(chǔ)器、片上外設(shè)和片外設(shè)備之間獨(dú)立傳輸。主要特點(diǎn):DMA操作獨(dú)立于CPU;擁有6個(gè)通道,DMA可以跟蹤6個(gè)獨(dú)立塊傳輸情況;對(duì)于內(nèi)部和外部訪問,DMA比CPU有更高優(yōu)先級(jí);每一通道優(yōu)先級(jí)可編程;每個(gè)通道的源、目的地址寄存器值每次讀寫后可靈活配置,讀寫一次后地址可以為常數(shù)、后加一、后減一或者被一個(gè)編程值修改;每次讀寫內(nèi)部傳送可由選擇的時(shí)間來初始化;完成一半或整個(gè)數(shù)據(jù)塊傳送,DMA向CPU發(fā)中斷;DMA可執(zhí)行雙字傳送。

2.3 多通道緩沖串行口McBSP

??? C5416內(nèi)置了3個(gè)高速、全雙工的McBSPs。通過McBSPs可直接接到其他DSP器件、CODEC器件或系統(tǒng)內(nèi)其他器件。主要特點(diǎn)有全雙工通信;雙緩沖數(shù)據(jù)寄存器,允許連續(xù)數(shù)據(jù)流;收發(fā)時(shí),獨(dú)立的幀和時(shí)鐘;可直接連接T1/E1、AC97等;最大至128通道的多通道收發(fā);u律和A律壓擴(kuò)可選;幀同步和數(shù)據(jù)時(shí)鐘的極性可選等。

??? CPU和DMA控制器通過內(nèi)部外設(shè)總線對(duì)McBSP進(jìn)行訪問,當(dāng)McBSP同步到一個(gè)DMA通道時(shí),數(shù)據(jù)可以集中在發(fā)送和接收緩沖區(qū),并且整個(gè)緩沖區(qū)是連續(xù)的。當(dāng)DMA填充完整個(gè)緩沖區(qū)后,就觸發(fā)一個(gè)中斷給CPU。這就明顯降低了中斷延時(shí)和處理時(shí)間。

2.4 Bootloader技術(shù)

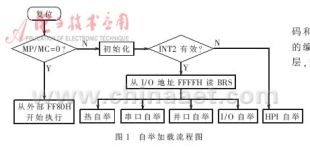

??? C54x DSP芯片一般都在片內(nèi)設(shè)置有BOOT程序,其主要功能是:在上電時(shí)將用戶程序代碼從外部存儲(chǔ)器加載到程序存儲(chǔ)器并執(zhí)行。加載程序途徑有從外部8位或16位EPROM加載,由主機(jī)通過8位或16位并行I/O口、串口、HPI以及自定義的自舉" title="自舉">自舉加載。其中自舉加載的過程如圖1所示。

?

??? 本文介紹的代碼實(shí)現(xiàn)過程用到了外部FLASH的并口自舉。并口自舉檢測(cè)過程如下:DSP首先從I/O空間的0xFFFFH位置讀取自舉表的起始地址,如果低8位地址有效,則并行加載;如果低8位數(shù)據(jù)無效,則DSP將從數(shù)據(jù)空間0xFFFFH位置讀取自舉表的起始地址,同樣低8位有效則并行加載,否則轉(zhuǎn)串行檢測(cè)。

3 編解碼算法的實(shí)時(shí)實(shí)現(xiàn)[9][10]

??? 匯編語言程序設(shè)計(jì)是TMS320VC5416應(yīng)用軟件設(shè)計(jì)的基礎(chǔ),其主要任務(wù)是利用DSP芯片提供的匯編指令和偽指令編寫源程序完成指定的功能。開發(fā)環(huán)境是TI公司的集成DSP軟件開發(fā)環(huán)境CCS,開發(fā)語言是匯編語言和C語言的混合編程。

??? 由于G.722.2是多速率語音編碼,所以在編碼解碼前要確定編碼模式,在硬件平臺(tái)實(shí)現(xiàn)時(shí),通過修改C源代碼的編碼模式提取部分函數(shù),從而給定每次編碼的速率模式,使代碼的實(shí)現(xiàn)不需要考慮信道傳輸情況,只專注于編解碼的算法實(shí)現(xiàn)。

3.1 C語言和匯編的混合編程

??? 采用C語言與匯編的混合編程實(shí)現(xiàn)G.722.2標(biāo)準(zhǔn)的代碼。為了不破壞C環(huán)境,改寫的匯編函數(shù)必須符合C函數(shù)的參數(shù)傳遞規(guī)則。在匯編程序設(shè)計(jì)時(shí),參數(shù)的傳遞主要遵循以下規(guī)則:

??? (1)函數(shù)的第一個(gè)參數(shù)存放在A寄存器,后面的參數(shù)以逆序壓入堆棧;如果參數(shù)有結(jié)構(gòu)體,則將結(jié)構(gòu)體的地址保存在A寄存器中。

??? (2)如果參數(shù)中存在長操作數(shù),則應(yīng)按照低位字先壓棧、高位字后壓棧的順序保存,否則容易出錯(cuò)。

在編寫匯編函數(shù)時(shí),除了遵循匯編函數(shù)的調(diào)用規(guī)則外,還必須對(duì)函數(shù)中用到的輔助寄存器進(jìn)行存放堆棧的保護(hù),防止調(diào)用時(shí)修改被調(diào)用函數(shù)中使用的輔助寄存器。

3.2 系統(tǒng)軟件結(jié)構(gòu)

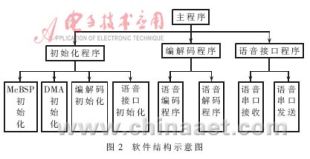

??? 整個(gè)系統(tǒng)軟件主要包括以下三個(gè)部分:初始化程序、語音編碼解碼部分和語音接口程序部分,整個(gè)軟件體系結(jié)構(gòu)如圖2所示。

??? 軟件各模塊的主要功能:(1)初始化部分完成編碼解碼和外設(shè)的初始化;(2)語音編碼解碼部分進(jìn)行語音信號(hào)的編碼和解碼處理;(3)語音接口部分是整個(gè)系統(tǒng)的最底層,完成語音信號(hào)在串口上的接收與發(fā)送。

??? G.722.2語音編碼解碼實(shí)現(xiàn)軟件中,主函數(shù)包含在main.c文件中。主程序的處理過程為:首先對(duì)DSP芯片、A/D(D/A)芯片以及McBSP、DMA初始化,然后打開中斷屏蔽控制器(IMR),允許中斷請(qǐng)求,進(jìn)入等

??? 待主循環(huán)啟動(dòng)DMA,同時(shí)串口開始接收數(shù)據(jù)。在接收過程中每接收完一幀數(shù)據(jù)時(shí),DMA向CPU產(chǎn)生一次中斷,將一幀數(shù)據(jù)從中取出,DMA緩沖區(qū)計(jì)數(shù)器清零以重新開始填充接收緩沖區(qū)。同時(shí)開始調(diào)用編碼解碼子程序?qū)ψx入的語音數(shù)據(jù)進(jìn)行壓縮處理,存儲(chǔ)處理后的輸出數(shù)據(jù)等待發(fā)送;當(dāng)發(fā)送完一幀數(shù)據(jù)時(shí),DMA向CPU產(chǎn)生一次中斷,緩沖區(qū)計(jì)數(shù)器清零,并將已存儲(chǔ)的待輸出數(shù)據(jù)填入發(fā)送緩沖區(qū),然后繼續(xù)對(duì)接收和發(fā)送緩沖區(qū)進(jìn)行檢測(cè),重復(fù)上述循環(huán)過程。程序設(shè)計(jì)了兩個(gè)獨(dú)立并行的DMA通道,分別負(fù)責(zé)語音數(shù)據(jù)的發(fā)送和接收,在不影響CPU的情況下可同時(shí)收發(fā)數(shù)據(jù),每發(fā)送或接收完一幀數(shù)據(jù)產(chǎn)生一次DMA中斷。

重建語音的質(zhì)量是評(píng)價(jià)編碼解碼算法和系統(tǒng)性能的關(guān)鍵指標(biāo)之一,可分為客觀評(píng)測(cè)和主觀評(píng)測(cè)標(biāo)準(zhǔn)。其中客觀評(píng)測(cè)標(biāo)準(zhǔn)主要是以3GPP提供的一套測(cè)試文件為DSP匯編程序正確性檢驗(yàn)的標(biāo)準(zhǔn);主觀評(píng)測(cè)一般采用的是平均判分法(MOS)。本文的主觀評(píng)測(cè)是邀請(qǐng)少量人員進(jìn)行實(shí)驗(yàn),實(shí)驗(yàn)結(jié)果具有一定的可參考性。實(shí)際測(cè)試時(shí),利用導(dǎo)線將硬件平臺(tái)上的Mic接口和各種聲音源相連,耳機(jī)插孔輸出編碼解碼后的語音,對(duì)解碼后的語音進(jìn)行試聽測(cè)試。實(shí)驗(yàn)表明,以男生、女生、音樂等多種音源作為Mic輸入,系統(tǒng)具有良好的適應(yīng)性。非正式試聽測(cè)試,恢復(fù)語音保留了較好的說話人特征。通過對(duì)不同編碼速率的比較可知,高速率語音編碼方式語音質(zhì)量明顯優(yōu)于低速率語音編碼方式。

參考文獻(xiàn)

[1] 王炳錫.變速率語音編碼[M].西安:西安電子科技大學(xué)出版社,2004,7.

[2] 程佩青.數(shù)字信號(hào)處理教程[M].北京:清華大學(xué)出版社,2002,2.

[3] 3GPP,TS 26.091:AMR Speech Codec;Error concealment of lost frames[S].2002,6.

[4] 3GPP,TS 26.092:AMR Speech Codec;Comfort noise for AMR speech traffic channels[S].2002,6.

[5] 3GPP,TS 26.093:AMR Speech Codec;Source controlled rate operation[S].2004,4.

[6] 3GPP,TS 26.094:AMR Speech Codec;Voice activity?detector for AMR speech traffic channels[S].2002,6.

[7] 3GPP,TS 26.101:Mandatory speech codec speech processing functions;Adaptive Multi-Rate(AMR) speech codec?frame structure[S].2004,9.

[8] TMS320VC5416 Fixed-Point digital signal processor data?manual[Z],March 1999,Revised January 2005.

[9] 戴明禎.TMS320C54x數(shù)字信號(hào)處理器原理、結(jié)構(gòu)及應(yīng)用[M].北京:北京航空航天大學(xué)出版社,2001

[10] 宗戰(zhàn)華,鄭建生.TMS320VC5416并行自舉的巧妙實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2004(12):77-80