摘 要: 介紹了一種基于計(jì)算機(jī)ISA總線、三路" title="三路">三路同步的DDS信號(hào)源的設(shè)計(jì)。對(duì)信號(hào)源與ISA總線的接口關(guān)系以及多路" title="多路">多路DDS的同步問(wèn)題進(jìn)行了討論。測(cè)試結(jié)果表明,該信號(hào)源的各路DDS具有較好的同步關(guān)系和相位噪聲指標(biāo)。

關(guān)鍵詞: 頻率合成 DDS ISA總線 同步 信號(hào)源

直接數(shù)字頻率合成(Direct Digital Frequency Synthesis)技術(shù)是近年來(lái)隨著數(shù)字集成電路和微電子技術(shù)的發(fā)展而迅速發(fā)展起來(lái)的一種新的頻率合成技術(shù)。直接數(shù)字式頻率合成器以其極高的頻率分辨率、極短的頻率轉(zhuǎn)換時(shí)間、相位精確可調(diào)、設(shè)備結(jié)構(gòu)簡(jiǎn)單、易集成、體積小及成本低等優(yōu)點(diǎn),在高分辨雷達(dá)系統(tǒng)、寬帶擴(kuò)頻通信系統(tǒng)以及現(xiàn)代測(cè)控系統(tǒng)中得到廣泛的應(yīng)用。為了便于信息的采集、處理和操作控制,常常要求信號(hào)源基于PC機(jī)平臺(tái)設(shè)計(jì)。PC機(jī)內(nèi)部有兩種常用的總線,即PCI總線和ISA總線。ISA總線接口關(guān)系簡(jiǎn)單,操作控制方便,既避免了PCI總線繁瑣的時(shí)序關(guān)系和各種苛刻的規(guī)范,又具有適中的傳輸速率,能夠滿足系統(tǒng)要求,是比較理想的DDS與計(jì)算機(jī)的接口總線。隨著電子系統(tǒng)復(fù)雜性的不斷增加,單路DDS已經(jīng)不能夠滿足系統(tǒng)需求,多路DDS系統(tǒng)的設(shè)計(jì)開始成為研究的熱點(diǎn)。

1 系統(tǒng)工作原理

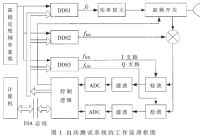

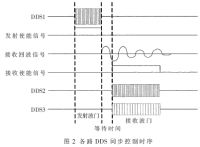

圖1是某自動(dòng)測(cè)試系統(tǒng)的工作原理框圖。圖中的高穩(wěn)定度頻率基準(zhǔn)為整個(gè)系統(tǒng)提供頻率為50MHz的參考時(shí)鐘。系統(tǒng)的控制命令由計(jì)算機(jī)發(fā)出,經(jīng)過(guò)ISA總線傳輸,送到FPGA進(jìn)行緩存、譯碼,同步控制三路DDS產(chǎn)生需要的信號(hào)。其中,DDS1的輸出信號(hào)為初始相位可變,脈沖寬度、脈沖周期、脈沖個(gè)數(shù)等由計(jì)算機(jī)編程設(shè)定的射頻脈沖序列。脈沖的載波頻率在fT=21MHz附近可調(diào)。該射頻脈沖經(jīng)過(guò)功率放大、低通濾波后,在高頻開關(guān)的控制下發(fā)射出去。接收到的反射回波由高頻開關(guān)選通,與DDS2產(chǎn)生的20MHz第一本振fLO1混頻,得到頻率為1MHz的中頻脈沖調(diào)制正弦信號(hào)。該中頻信號(hào)再分成兩路,分別與DDS3輸出的頻率為1MHz二本振fLO2的I支路和Q支路兩路脈沖調(diào)制正交信號(hào)進(jìn)行相位檢波,得到的信號(hào)經(jīng)低通濾波、模數(shù)轉(zhuǎn)換,送到計(jì)算機(jī)進(jìn)行數(shù)據(jù)處理。為保證收發(fā)信號(hào)有效可靠地隔離,在發(fā)射波門和接收波門之間插入等待時(shí)間。各路信號(hào)之間的關(guān)系如圖2所示。為簡(jiǎn)便起見(jiàn),圖中只畫出了DDS3輸出的I、Q兩路信號(hào)中的一路,這不影響對(duì)信號(hào)控制時(shí)序的理解。

?

為了便于信號(hào)處理,該系統(tǒng)對(duì)各路DDS輸出信號(hào)的時(shí)間關(guān)系提出了嚴(yán)格的要求:(1)相位檢波器的兩路正交參考信號(hào)相位應(yīng)嚴(yán)格控制在90°相差上,以保證正交檢波器的性能。(2)其初始相位可以通過(guò)計(jì)算機(jī)控制調(diào)整。(3)DDS2的輸出信號(hào)和DDS3的I支路輸出信號(hào)必須同步,以保證在DDS3同相支路上的信號(hào)相位與中頻信號(hào)的相位保持同步;同時(shí)Q路信號(hào)必須保持相位的正交。(4)每個(gè)射頻脈沖周期,各路DDS輸出信號(hào)的初始相位嚴(yán)格同步,保證回波信號(hào)的相參積累。

2 多路同步設(shè)計(jì)

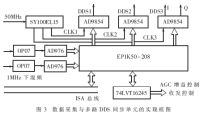

圖3是該自動(dòng)測(cè)試系統(tǒng)的數(shù)據(jù)采集、多路DDS同步單元的實(shí)現(xiàn)框圖。經(jīng)過(guò)相位檢波、低通濾波的I、Q兩路信號(hào)輸入到該單元電路中,經(jīng)OP-07放大、AD976采集后,再經(jīng)FPGA由ISA總線送入到計(jì)算機(jī)中。OP-07具有低偏移、高開環(huán)增益的特點(diǎn),適合于高增益的測(cè)試系統(tǒng)應(yīng)用。AD976是采樣速率為200ksps的高速16位低功耗模數(shù)轉(zhuǎn)換器。FPGA芯片采用Altera公司的ACEX系列芯片EP1K50,實(shí)現(xiàn)ISA總線與三路DDS及數(shù)據(jù)采集的接口。其靈活的可重新配置特性為實(shí)現(xiàn)接口電路提供了極大的方便,片上集成有40Kbit的RAM,便于緩存計(jì)算機(jī)的控制信息。DDS芯片選擇美國(guó)模擬器件公司的AD9854。它的相位累加器為48位,利用片上PLL可實(shí)現(xiàn)4~20倍的可編程倍頻,內(nèi)部最高時(shí)鐘可達(dá)300MHz,尤為突出的優(yōu)勢(shì)在于具有100MHz的高速并行配置接口,內(nèi)置最大相位誤差小于1°的I、Q兩路的DAC輸出,便于產(chǎn)生1MHz的正交信號(hào)。對(duì)于該自動(dòng)測(cè)試系統(tǒng),各路DDS之間的同步關(guān)系是電路設(shè)計(jì)的核心問(wèn)題。AD9854芯片本身沒(méi)有同步信號(hào),要實(shí)現(xiàn)各路的精確同步,必須對(duì)電路進(jìn)行優(yōu)化設(shè)計(jì)。為分析方便,分別從參考時(shí)鐘、刷新時(shí)鐘和內(nèi)部鎖相倍頻三部分進(jìn)行討論。

2.1 參考時(shí)鐘

成功的同步設(shè)計(jì)要求各路DDS的參考時(shí)鐘之間的相位差最小。參考時(shí)鐘邊沿的時(shí)間差會(huì)使各路DDS輸出信號(hào)產(chǎn)生相應(yīng)比例的相位差。參考時(shí)鐘的邊沿抖動(dòng)要足夠小,上升/下降時(shí)間要短,以免增加時(shí)鐘信號(hào)" title="時(shí)鐘信號(hào)">時(shí)鐘信號(hào)的相位誤差。數(shù)據(jù)采集與多路DDS單元電路首先把外部送來(lái)的50MHz高精度、高穩(wěn)定度的正弦信號(hào)轉(zhuǎn)換成方波,送給各路DDS作參考時(shí)鐘。時(shí)鐘轉(zhuǎn)換功能利用1:4的PECL時(shí)鐘分配器SY100EL15實(shí)現(xiàn)。ECL電路是現(xiàn)有各種實(shí)用數(shù)字邏輯集成電路中速度最快的一種, 也是目前惟一能夠提供亞毫微秒開關(guān)時(shí)間的實(shí)用數(shù)字邏輯電路。SY100EL15最高可以工作在1.25GHz頻率上,器件間的最大偏斜為200ps,單個(gè)器件的最大偏斜為50ps,時(shí)鐘均方抖動(dòng)僅為2.6ps,上升時(shí)間介于325ps和575ps之間。AD9854的參考時(shí)鐘能夠兼容PECL邏輯。射頻信號(hào)在長(zhǎng)線傳輸過(guò)程中,為了抑制由此產(chǎn)生的反射和串?dāng)_,SY100EL15的輸出與AD9854參考時(shí)鐘之間的PECL邏輯電路必須良好地匹配。圖4的匹配方式是一種比較好的方案。圖中:

R2=Z0(VCC-VEE)/(VCC-VTT)

R1=R2(VCC-VTT)/(VTT-VEE)

式中,VTT=VCC-2.0, Z0=50Ω。對(duì)于3.3V供電的LVPECL電路,R1取126Ω,R2取82.5Ω。AD9854的時(shí)鐘輸入電路有單端方式和差分方式兩種,采用差分方式有利于抑制電路產(chǎn)生共模噪聲。時(shí)鐘分配網(wǎng)絡(luò)布線時(shí),要保證每一路差分時(shí)鐘信號(hào)的走線等長(zhǎng),并且各路DDS時(shí)鐘信號(hào)之間的走線也應(yīng)當(dāng)?shù)乳L(zhǎng)。電路板應(yīng)該按照微帶線設(shè)計(jì)。不同的微帶線結(jié)構(gòu)將導(dǎo)致信號(hào)傳輸常數(shù)有所差異。

2.2 刷新時(shí)鐘

AD9854芯片引腳中與配置內(nèi)核密切相關(guān)的信號(hào)除了數(shù)據(jù)線、地址線、寫信號(hào)以外,還有刷新時(shí)鐘。寫信號(hào)的作用是將I/O口上的數(shù)據(jù)傳送到AD9854芯片內(nèi)部的緩沖區(qū)中,而刷新時(shí)鐘則用于配置AD9854內(nèi)核的相應(yīng)寄存器。刷新時(shí)鐘引腳既可以作為輸入信號(hào),工作于外部刷新模式;又可以作為輸出信號(hào),工作于內(nèi)部刷新模式。鑒于多路同步原因,通常工作于外部刷新模式。刷新信號(hào)的時(shí)序如圖5所示。從AD9854內(nèi)部看,刷新時(shí)鐘UPDATE實(shí)際上是電平有效信號(hào)。在該信號(hào)出現(xiàn)于AD9854引腳后的第一個(gè)系統(tǒng)時(shí)鐘" title="系統(tǒng)時(shí)鐘">系統(tǒng)時(shí)鐘上升沿" title="上升沿">上升沿,即A時(shí)刻,系統(tǒng)時(shí)鐘識(shí)別到刷新時(shí)鐘。在第三個(gè)系統(tǒng)時(shí)鐘的上升沿,產(chǎn)生AD9854芯片DDS內(nèi)核的內(nèi)部刷新時(shí)鐘。該信號(hào)與系統(tǒng)刷新時(shí)鐘同步,作為將I/O口上的數(shù)據(jù)配置到AD9854內(nèi)部配置寄存器的時(shí)鐘信號(hào)。在第四個(gè)系統(tǒng)時(shí)鐘的上升沿,完成對(duì)內(nèi)部寄存器的配置。在第五個(gè)時(shí)鐘的上升沿,產(chǎn)生內(nèi)部刷新時(shí)鐘信號(hào)的下降沿,配置過(guò)程結(jié)束。以圖5為例,為使該過(guò)程工作可靠,應(yīng)當(dāng)保證三路DDS芯片的刷新時(shí)鐘必須超前于相同的系統(tǒng)時(shí)鐘,即時(shí)鐘0,否則會(huì)導(dǎo)致各路DDS的輸出相差一個(gè)AD9854的系統(tǒng)時(shí)鐘。

2.3 鎖相倍頻

根據(jù)數(shù)模轉(zhuǎn)換的數(shù)學(xué)模型,DDS輸出信號(hào)的頻率通常不得超過(guò)系統(tǒng)時(shí)鐘頻率的40%。以50MHz作為參考時(shí)鐘產(chǎn)生頻率為20MHz的信號(hào)會(huì)給濾波帶來(lái)困難。AD9854內(nèi)部集成了鎖相倍頻電路,可以將50MHz的參考時(shí)鐘倍頻至200MHz。片上鎖相倍頻電路帶來(lái)的問(wèn)題是環(huán)路建立時(shí)間會(huì)隨著AD9854及片外環(huán)路濾波器的器件不同而產(chǎn)生差異。這將導(dǎo)致在鎖相環(huán)路的建立過(guò)程中,送給AD9854相位累加器的系統(tǒng)時(shí)鐘周期數(shù)目無(wú)法準(zhǔn)確預(yù)測(cè)。因此在環(huán)路建立過(guò)程中,相位控制字的值必須為零以避免相位累加器的值不斷累加。DDS芯片內(nèi)部集成鎖相環(huán)路的建立時(shí)間典型值約為400μs。為了保證各路DDS的同步,在起始10ms讓AD9854輸出的頻率控制字和相位控制字始終為零。10ms以后,才啟動(dòng)AD9854的輸出相位累加過(guò)程。待PLL建立起來(lái)以后,再改變各路DDS芯片相應(yīng)的控制字。

計(jì)算機(jī)的主控軟件用VB語(yǔ)言編寫,系統(tǒng)FPGA軟件用VHDL語(yǔ)言編寫。FPGA內(nèi)部設(shè)計(jì)了一個(gè)基于FIFO技術(shù)的緩沖區(qū),將主控計(jì)算機(jī)發(fā)送過(guò)來(lái)的各類控制命令暫存。為了簡(jiǎn)化控制時(shí)序,采用的方法是利用ISA總線的數(shù)據(jù)線依次傳輸各路AD9854的配置數(shù)據(jù)和寄存器地址,并且暫時(shí)存放在緩沖區(qū)中;而后利用ISA總線的寫信號(hào)作為各路AD9854的刷新時(shí)鐘信號(hào),完成對(duì)DDS芯片的同步配置。

3 測(cè)試結(jié)果

ISA總線信號(hào)源采用四層印刷電路板設(shè)計(jì)。布線時(shí),采取電源退耦濾波、合理分割內(nèi)電層、隔離數(shù)字地和模擬地等措施,有效地克服了計(jì)算機(jī)內(nèi)部復(fù)雜的電磁干擾環(huán)境,得到了較好的測(cè)試結(jié)果。用Agilent公司頻譜儀8563EC測(cè)試了DDS輸出的頻譜。用Tektronix公司的示波器TDS3032B測(cè)試了三路DDS輸出的時(shí)間關(guān)系。結(jié)果表明,信號(hào)在20MHz處的相位噪聲優(yōu)于-100dBc@1kHz,在0~0.5fs范圍內(nèi)的雜散抑制優(yōu)于-55dBc。以DDS的刷新信號(hào)作為同步參考信號(hào),三路DDS(包括DDS3的I/Q兩路),從刷新時(shí)鐘上升沿到DDS有信號(hào)輸出,時(shí)間間隔均為305ns,能夠?qū)崿F(xiàn)精確的同步。

為了保證頻率合成器的性能指標(biāo),抑制電磁干擾,DDS通常都是單獨(dú)安裝在密閉的屏蔽盒中。從目前的應(yīng)用情況看,越來(lái)越多的基于計(jì)算機(jī)的電子系統(tǒng)要求利用DDS技術(shù)實(shí)現(xiàn)各種精確、使用靈活的信號(hào)源。這使得DDS很難實(shí)現(xiàn)單獨(dú)屏蔽。計(jì)算機(jī)系統(tǒng)內(nèi)部的電磁泄漏非常嚴(yán)重。信號(hào)走向、各種時(shí)鐘和時(shí)鐘發(fā)生器、CPU等都會(huì)對(duì)處于計(jì)算機(jī)內(nèi)部的DDS產(chǎn)生干擾。本文對(duì)基于計(jì)算機(jī)的DDS技術(shù)做了嘗試。在沒(méi)有增加屏蔽結(jié)構(gòu)的條件下,頻率合成器的相位噪聲和雜散指標(biāo)都滿足系統(tǒng)要求,針對(duì)AD9854,通過(guò)精心設(shè)計(jì),實(shí)現(xiàn)了多路DDS的同步和IQ正交輸出。

參考文獻(xiàn)

1 Brandon D. Synchronizing multiple AD9852 DDS-based synthesizers. Analog Devices Inc, 2003

2 A technical tutorial on digital signal synthesis.Analog Devices Inc.,1999

3 Shockman P. Termination of ECL logic devices. Onsemi Semiconductor,1999

4 Kenneth M. True. Long transmission lines and data signal quality. National Semiconductor, March 1992

5 李家濱. 微機(jī)系統(tǒng)硬件教程. 北京:海洋出版社, 1993

6 王 峰,鄒 澎.計(jì)算機(jī)主板電磁泄漏的分析與測(cè)量.計(jì)算機(jī)工程,2003;(9)