蓄電池在電力系統(tǒng)中是一種必備的后備電源且數(shù)量較多, 其使用壽命和安全可靠性倍受用戶關(guān)注。但由于使用不當(dāng)或者不能及時(shí)維護(hù),經(jīng)常會(huì)導(dǎo)致蓄電池組中個(gè)別蓄電池的過(guò)放電或者早期失效。過(guò)放電或者早期失效的個(gè)別蓄電池在后備電源投入使用時(shí),會(huì)嚴(yán)重影響整個(gè)電池組的放電容量,甚至?xí)?dǎo)致整個(gè)供電系統(tǒng)的崩潰。因此,為保證在市電被切斷時(shí)用電設(shè)備能夠安全可靠運(yùn)行,避免蓄電池在長(zhǎng)期使用過(guò)程中因個(gè)別電池過(guò)放電或者失效而引發(fā)事故帶來(lái)經(jīng)濟(jì)損失,對(duì)蓄電池進(jìn)行實(shí)時(shí)在線監(jiān)測(cè)和及時(shí)的故障診斷成為蓄電池維護(hù)工作的一個(gè)極為重要 方面。本文介紹的基于STC89C58RD+微控制器的蓄電池在線監(jiān)測(cè)系統(tǒng),能實(shí)現(xiàn)對(duì)蓄電池?zé)o論在閑置狀態(tài)還是充、放電動(dòng)態(tài)過(guò)程中的狀態(tài)監(jiān)測(cè);對(duì)蓄電池內(nèi) 部開路、短路、過(guò)壓、欠壓及過(guò)度放電等異常狀態(tài)及時(shí)報(bào)警并存儲(chǔ)數(shù)據(jù)以備查詢;能對(duì)2V、6V和12V多種多節(jié)電池電壓在線測(cè)量;提高了對(duì)蓄電池監(jiān)測(cè)的準(zhǔn)確 性、自動(dòng)化和智能化程度。本文具體介紹了系統(tǒng)的硬件設(shè)計(jì)和軟件實(shí)現(xiàn)。

系統(tǒng)硬件設(shè)計(jì)

系統(tǒng)硬件結(jié)構(gòu)

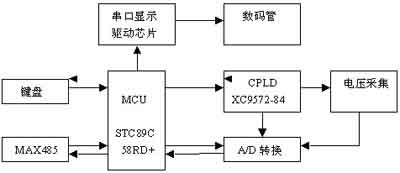

蓄電池在線監(jiān)測(cè)系統(tǒng)是以STC89系列的STC89C58RD+微控制器、XILINX的XC9572-84為核心,外圍電路主要由電壓采集電路、 A/D轉(zhuǎn)換電路、顯示驅(qū)動(dòng)電路及鍵盤電路等幾部分組成的,如圖1所示。A/D轉(zhuǎn)換芯片采用10位ADC TLC1549。顯示驅(qū)動(dòng)芯片采用MC14489B,它可以驅(qū)動(dòng)5位共陰極數(shù)碼管,微控制器的P1口的低5位作為鍵盤輸入口,擴(kuò)展的RS485接口用于多 機(jī)通信 。下面詳細(xì)介紹系統(tǒng)中STC89C58RD+、XC9572-84器件和電壓采集電路、A/D轉(zhuǎn)換電路的設(shè)計(jì)與實(shí)現(xiàn)。

圖1 系統(tǒng)硬件結(jié)構(gòu)框圖

微控制器STC89C58RD+簡(jiǎn)介

STC89C58RD+是STC89系列的微控制器,它不但與80C51完全兼容,而且還有新的特點(diǎn):片內(nèi)含有Flash程序存儲(chǔ)器32Kb, DataFlash數(shù)據(jù)存儲(chǔ)器32Kb,RAM數(shù)據(jù)存儲(chǔ)器1208B,同時(shí)內(nèi)部還有看門狗(WDT);由于ALE信號(hào)開關(guān)狀態(tài)可設(shè)置,從而降低了EMI; 具有可編程的8級(jí)中斷源4種優(yōu)先級(jí),具有系統(tǒng)可編程(ISP)和應(yīng)用可編程(IAP)等特點(diǎn),片內(nèi)資源豐富、集成度高、使用方便。STC89C58RD+ 對(duì)系統(tǒng)的工作進(jìn)行實(shí)施調(diào)度,實(shí)現(xiàn)外部輸入?yún)?shù)的設(shè)置、電池電壓的測(cè)試和顯示、電池工作狀態(tài)的指示。

邏輯編程器件XC9572-84(CPLD)

由于監(jiān)測(cè)的電池節(jié)數(shù)較多,所需要I/O口較多,用傳統(tǒng)的設(shè)計(jì)方法,需要74HC273、74HC00、74HC138、CD4514等多種芯片來(lái)實(shí) 現(xiàn),器件種類和數(shù)量多,使PCB的尺寸加大,也增加了系統(tǒng)的不穩(wěn)定因素。本系統(tǒng)選用XILINX系列的CPLD器件XC9572-84,其共有72個(gè)宏單 元,69個(gè)I/O口,1600個(gè)門,72個(gè)寄存器,可以對(duì)上述多種芯片進(jìn)行集成。該器件具有在系統(tǒng)可編程能力,含有先進(jìn)的數(shù)據(jù)保密特性,它可以完全保護(hù)編 程數(shù)據(jù)不被非法讀取和擦除,每個(gè)I/O口都有一個(gè)可編程輸出擺率控制位從而可減小系統(tǒng)噪聲,采用具有較低功耗的快速閃存技術(shù),每個(gè)I/O口的驅(qū)動(dòng)能力強(qiáng), 負(fù)載電流可達(dá)24mA。XC9572-84接收單片機(jī)傳來(lái)的數(shù)據(jù)和地址,控制各個(gè)固態(tài)繼電器(G3VM-402C)的選通以及A/D轉(zhuǎn)換的進(jìn)行,達(dá)到采集 電壓的功能。采用了CPLD器件后,減少了系統(tǒng)所需器件的數(shù)量和種類,簡(jiǎn)化了PCB的排版和布線,減小了系統(tǒng)體積和節(jié)約成本,方便了系統(tǒng)調(diào)試,有利于批量化生產(chǎn)。

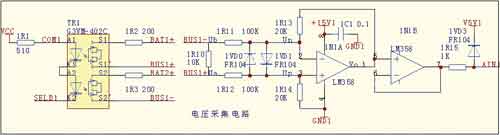

圖2 電壓采集電路

電壓采集電路

電壓采集電路直接影響到電壓測(cè)試的精確程度,因而采集電路設(shè)計(jì)得是否適當(dāng)對(duì)整個(gè)系統(tǒng)至關(guān)重要。對(duì)每節(jié)電池電壓進(jìn)行測(cè)量,有兩種方法:①對(duì)每節(jié)電池電 壓直接采集。②采集(n+1)節(jié)電池的總電壓,減去n節(jié)電池的總電壓得第n+1節(jié)電池電壓。第一種電壓采集精確而且安全。第二種雖然電路比較簡(jiǎn)單但是當(dāng)電 池節(jié)數(shù)多時(shí)采集的電壓太高,不安全而且會(huì)出現(xiàn)較大的誤差。因此選用第一種方法。電壓采集電路要求要安全,采集的電壓要足夠的穩(wěn)定。本系統(tǒng)的蓄電池組采用串 接方式,BAT1+接第一節(jié)電池的正極,BAT2+接第二節(jié)的正極(第一節(jié)的負(fù)極),如此依次連接,最多可達(dá)41節(jié)。經(jīng)過(guò)XC9572-84模擬開關(guān)選通 G3VM-402C后,將1~n節(jié)電池電壓依次釋放到電壓總線BUS1+、BUS1-上,電路選用運(yùn)算放大器LM358作為信號(hào)放大器件,它的前級(jí)為差分 式放大器,后級(jí)為電壓跟隨器,使TLC1549得到一個(gè)穩(wěn)定的采樣電壓,如圖2所示。1VD0和1VD1采用FR104高速開關(guān)管來(lái)保護(hù)運(yùn)算放大器的內(nèi)部 電路。差分式放大倍數(shù)為A=0.2,具體推導(dǎo)如下:

(Ua-Up)/1R12=Up/1R14; ①

(Ub-Un)/1R11=(Un-Vo)/1R13;②

注意運(yùn)放的“虛短”特點(diǎn),有Up=Un;結(jié)合①、②兩式得到Vo=((1R11+1R13)/1R11)·(1R14/(1R12+1R14))·Ua-1R13/1R11·Ub;選取電阻滿足:1R13/1R11=1R14/1R12的關(guān)系,輸出電壓可簡(jiǎn)化為:Vo=1R13/1R11·(Ua-Ub),故電壓放大倍數(shù)A=Vo/(Ua-Ub)=1R13/1R11=0.2。

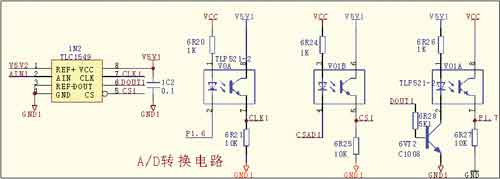

A/D轉(zhuǎn)換電路

本系統(tǒng)A/D轉(zhuǎn)換采用片外串行總線10位高速高精度專用集成電路TLC1549,其功耗低、體積小、占用單片機(jī)的資源少,具有連接方便、編程簡(jiǎn)單的 特點(diǎn)。電壓采集電路的輸出電壓與TLC1549的A/D轉(zhuǎn)換通道相連接,在時(shí)鐘脈沖信號(hào)作用下,TLC1549將電壓轉(zhuǎn)換成10位二進(jìn)制數(shù)字信號(hào),并把上 次A/D轉(zhuǎn)換的結(jié)果以10位二進(jìn)制數(shù)的形式依次輸出,再通過(guò)光電隔離傳送到單片機(jī)進(jìn)行處理,如圖3所示。

圖3 A/D轉(zhuǎn)換電路

硬件設(shè)計(jì)過(guò)程中的注意點(diǎn)

1 系統(tǒng)用多路電源,要考慮系統(tǒng)的功耗選擇適當(dāng)?shù)碾娫矗娫措妷簯?yīng)比較穩(wěn)定。

2 電壓采集部分使用固態(tài)繼電器(G3VM-402C),由于電池節(jié)數(shù)較多,電壓比較高,故應(yīng)注意對(duì)內(nèi)部電路的保護(hù),可以采用適當(dāng)功率的電阻。對(duì)放大電路的電 阻精度要求較高,可選用精度為1%的金屬膜電阻;電路設(shè)計(jì)應(yīng)避免出現(xiàn)因多個(gè)固態(tài)繼電器同時(shí)開通的直通現(xiàn)象,這樣會(huì)使多節(jié)蓄電池短路,造成電壓采集電路的損 壞。

3 A/D轉(zhuǎn)換芯片的基準(zhǔn)電源要十分穩(wěn)定,基準(zhǔn)電源與芯片工作電源應(yīng)采用不同的共地電源,以保證A/D轉(zhuǎn)換芯片基準(zhǔn)電源的穩(wěn)定性。為了減少干擾,時(shí)鐘和片選信號(hào)與單片機(jī)、CPLD之間進(jìn)行光電隔離。

4 器件的布局和PCB圖的布線采用模塊化,交流與直流分離,強(qiáng)電與弱電分離,數(shù)字地和模擬地分開,注意電源線和地線的布局。

系統(tǒng)軟件設(shè)計(jì)

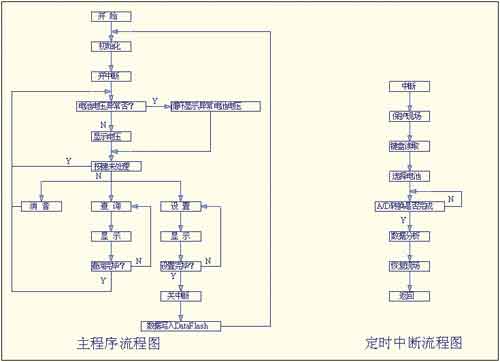

在單片機(jī)的軟件編程上,以Keil C編譯器的Windows集成開發(fā)環(huán)境 μvision2作為軟件開發(fā)平臺(tái),采用C51高級(jí)語(yǔ)言編寫。該語(yǔ)言是80C51系列單片機(jī)的專門的高性能的程序設(shè)計(jì)語(yǔ)言。它采用符合ANSI標(biāo)準(zhǔn)的C語(yǔ) 言編程,便于改進(jìn)、擴(kuò)充和移植,可以對(duì)硬件進(jìn)行操作,能夠產(chǎn)生極高速和極其簡(jiǎn)潔形式的目標(biāo)代碼,在代碼的效率和執(zhí)行速度上完全可以和匯編語(yǔ)言相媲美,并且 有十分豐富的庫(kù)函數(shù)可以供用戶直接調(diào)用,從而極大地提高了程序的編寫效率,能提供給用戶高質(zhì)量的程序代碼。采用硬件描述語(yǔ)言Verilog HDL對(duì)CPLD進(jìn)行編程。

單片機(jī)軟件編程注意點(diǎn)

1 鍵盤在定時(shí)中斷服務(wù)程序中讀取,用中斷間隔時(shí)間實(shí)現(xiàn)鍵盤的去抖,不必編寫另外的延時(shí)程序,提高了CPU的利用效率。鍵盤值存入數(shù)據(jù)緩沖區(qū),在主程序中讀數(shù)據(jù)緩沖區(qū)的內(nèi)容,執(zhí)行鍵盤功能散轉(zhuǎn)子程序。

2 電池電壓的采集在中斷程序中執(zhí)行,因固態(tài)繼電器的開通與關(guān)斷時(shí)間均需1ms,故通道選通時(shí)要有一定的延時(shí),使電池采集電壓建立并穩(wěn)定后再啟動(dòng)A/D轉(zhuǎn)換。

3 根據(jù)A/D轉(zhuǎn)換芯片TLC1549的工作原理,當(dāng)前輸出的數(shù)據(jù)是上一次A/D轉(zhuǎn)換的結(jié)果, 故對(duì)一節(jié)電池電壓采樣的首次A/D轉(zhuǎn)換結(jié)果應(yīng)丟棄,其余幾次轉(zhuǎn)換結(jié)果保留并加以處理。

圖4 單片機(jī)軟件編程流程圖

4 根據(jù)STC89C58RD+的DataFlash 的特點(diǎn),數(shù)據(jù)寫入時(shí)必須啟動(dòng)ISP/IAP命令,CPU等待IAP動(dòng)作定時(shí)后,才繼續(xù)執(zhí)行程序,要先關(guān)斷中斷(EA)。要使數(shù)據(jù)寫入DataFlash存 儲(chǔ)器,不能跨越扇區(qū),如果要對(duì)某個(gè)扇區(qū)進(jìn)行擦除,而其中有些字節(jié)的內(nèi)容需要保護(hù),則需將其先讀到單片機(jī)內(nèi)部的RAM中保存,再將該扇區(qū)擦除,然后再將保存 的數(shù)據(jù)寫回該扇區(qū)。

CPLD的Verilog HDL編程

用硬件描述語(yǔ)言Verilog HDL的程序設(shè)計(jì)硬件的好處在于易于理解、易于維護(hù)、調(diào)試電路速度快、有許多易于掌握的仿真、綜合和布局布線的工具,還可以用C語(yǔ)言配合Verilog HDL來(lái)做邏輯設(shè)計(jì)的布線前和布線后仿真,驗(yàn)證功能是否正確。限于篇幅,下面給出部分模塊的Verilog HDL程序

module REG8 ( CLRB, D, CLK, Q ); //8位數(shù)據(jù)鎖存

input CLRB, CLK;

input [7:0] D;

output [7:0] Q;

reg [7:0] Q;

always @( posedge CLK or negedge CLRB )

Q <= ( !CLRB )? 0: D;

endmodule

module DECODE4_16( E1,A,Y ); //4-16譯碼

input E1;

input [3:0] A;

output [15:0] Y;

reg [15:0] Y;

always @( E1 or A )

if(E1==0 )

begin

case(A)

0:Y=16'b1111111111111110;

1:Y=16'b1111111111111101;

2:Y=16'b1111111111111011;

3:Y=16'b1111111111110111;

4:Y=16'b1111111111101111;

5:Y=16'b1111111111011111;

6:Y=16'b1111111110111111;

7:Y=16'b1111111101111111;

8:Y=16'b1111111011111111;

9:Y=16'b1111110111111111;

10:Y=16'b1111101111111111;

11:Y=16'b1111011111111111;

12:Y=16'b1110111111111111;

13:Y=16'b1101111111111111;

14:Y=16'b1011111111111111;

15:Y=16'b0111111111111111;

endcase

end

else

Y=16'b1111111111111111;endmodule