摘 要: 設(shè)計了一套基于FPGA的通用離線開關(guān)電源" title="開關(guān)電源">開關(guān)電源硬件模擬" title="硬件模擬">硬件模擬開發(fā)平臺" title="開發(fā)平臺">開發(fā)平臺,并對此硬件開發(fā)平臺的硬件組成及工作原理進行了分析。利用此硬件開發(fā)平臺對開關(guān)電源控制器進行硬件模擬,可以彌補控制芯片" title="控制芯片">控制芯片設(shè)計過程中軟件仿真的不足,大大縮短控制芯片開發(fā)周期。

關(guān)鍵詞: FPGA 離線開關(guān)電源 開關(guān)電源控制器 硬件模擬

隨著電力電子技術(shù)的發(fā)展,離線開關(guān)電源在人們的日常生活中得到了日益廣泛的應(yīng)用。在開關(guān)電源領(lǐng)域,各大半導(dǎo)體廠商對開關(guān)電源控制芯片的競爭也日趨激烈。因此,縮短控制芯片的開發(fā)周期及新產(chǎn)品的上市時間,是提高其競爭力的關(guān)鍵因素。

在開關(guān)電源控制芯片的設(shè)計過程中,軟件仿真是系統(tǒng)方案論證的一個重要手段。而控制芯片的硬件模擬,因其能夠克服軟件仿真的一些缺點,日益受到人們關(guān)注。為此,筆者設(shè)計并開發(fā)了一套基于FPGA的通用開關(guān)電源控制器硬件模擬平臺。控制器的邏輯電路通過FPGA編程實現(xiàn);控制器的模擬電路通過比較器、放大器等實現(xiàn)。通過此平臺對開關(guān)電源控制芯片進行硬件模擬,直接從硬件對控制器設(shè)計的技術(shù)方案進行論證確認,提高了控制器設(shè)計的可靠性,從而大大縮短其設(shè)計周期。

1 通用硬件模擬開發(fā)平臺的組成

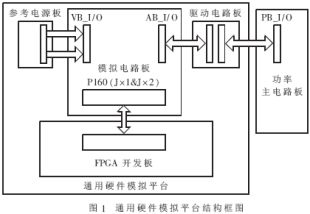

此通用IC控制器硬件模擬開發(fā)平臺主要由兩部分組成:數(shù)字電路部分(包括一塊FPGA開發(fā)板)和模擬電路部分(包括一塊模擬電路板、一塊參考電源板和一塊驅(qū)動電路板)。此平臺的結(jié)構(gòu)框圖如圖 1所示。

1.1 數(shù)字電路部分

數(shù)字電路部分由Memec公司的Spartan-3 LC開發(fā)板組成。此開發(fā)板基于Xilinx公司的Spartan-3系列FPGA XC3S400,主要包含有:1個50MHz的時鐘晶振、1個RS-232接口、1個USB 2.0接口、4個LED、8個滑動開關(guān)、2個按鈕式開關(guān)、1個七段顯示器以及2個可擴展至109個用戶I/O的接口。

Spartan-3系列FPGA XC3S400采用90nm工藝技術(shù),包含有40萬個系統(tǒng)門(System gates)、8064個等效邏輯單元(Equivalent logic cells)、16個18×18專用乘法器、4個片上時鐘管理模塊(DCM)以及多達141個用戶I/O引腳。

此開發(fā)板提供了強大的可編程數(shù)字邏輯功能。通過對FPGA的編程,可以實現(xiàn)各種所需的數(shù)字邏輯策略,從而可以很好地對PWM控制器的數(shù)字邏輯部分進行硬件模擬。

1.2 模擬電路部分

模擬電路部分主要包括以下功能模塊:5V電源模塊、參考電壓模塊、通用加法電路模塊、通用放大電路模塊、通用比較電路模塊、數(shù)字軟啟動" title="軟啟動">軟啟動單元模塊、模擬軟啟動單元模塊、A/D模塊、驅(qū)動電路模塊等。

通過對這些通用模塊及其他功能模塊的組合,可以實現(xiàn)對PWM控制器各種模擬電路單元的硬件仿真。

限于文章篇幅,各個功能模塊的具體組成將不在此介紹。

2 開關(guān)電源控制器硬件模擬的實現(xiàn)

通過對FPGA的邏輯功能編程以及模擬電路功能模塊的組合,可以實現(xiàn)開關(guān)電源PWM控制器各個功能模塊的硬件模擬,如振蕩器模塊、軟啟動模塊、PWM生成模塊以及保護電路模塊等。

2.1 振蕩器模塊的實現(xiàn)

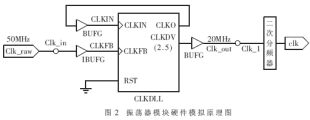

振蕩器模塊用來產(chǎn)生一定頻率的觸發(fā)脈沖,此模塊可以直接由FPGA得到,其原理圖如圖2所示。

由外部晶振產(chǎn)生的50MHz時鐘信號經(jīng)過一次分頻模塊CLKDLL得到20MHz的時鐘信號,然后再經(jīng)過一個可以自由設(shè)定參數(shù)的二次分頻器,得到所需要的時鐘頻率信號。其中,一次分頻模塊CLKDLL為Xilinx公司的標準庫函數(shù);二次分頻模塊利用VHDL語言編寫邏輯程序予以實現(xiàn)。

2.2 軟啟動模塊的實現(xiàn)

為避免開關(guān)電源開啟時在輸入端產(chǎn)生過大的沖擊電流,其控制芯片內(nèi)部集成有軟啟動模塊。軟啟動電路有多種實現(xiàn)方法,利用通用硬件模擬平臺可以模擬出相應(yīng)的軟啟動電路。

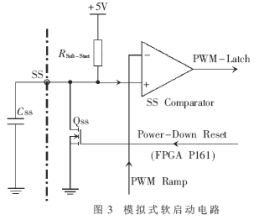

2.2.1 模擬式軟啟動電路

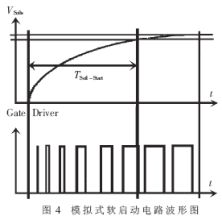

此模式的軟啟動電路如圖3所示,由上拉電阻RSoft-Start和外加電容Css實現(xiàn)。當(dāng)模擬平臺開啟時,5V基準源通過上拉電阻RSoft-Start向Css充電,軟啟動時間由時間常數(shù)決定,TSoft-Start=2τ=2RSoft-StartCss;當(dāng)模擬平臺關(guān)閉時,由FPGA產(chǎn)生Reset信號,開通Qss,使Css放電,以保證下次重新啟動模擬平臺時,Css的電壓從零開始上升。啟動過程的波形如圖4所示。

?

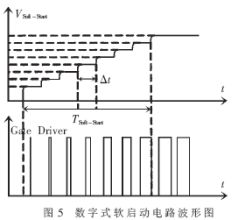

2.2.2 數(shù)字式軟啟動電路

另一種軟啟動模式為數(shù)字式軟啟動模式。其設(shè)計思想是通過控制三個開關(guān)管的開通順序,得到一逐次上升的階梯形電壓VSofts,從而達到軟啟動的目的。軟啟動的時間可以通過切換時間△t確定,即TSoft-Start=7△t。啟動過程的波形如圖5所示。

2.3 PWM生成模塊的實現(xiàn)

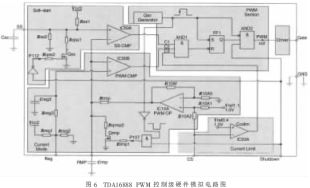

此硬件模擬平臺可以實現(xiàn)電壓型及電流型脈寬調(diào)制方式。電流型PWM發(fā)生器的實現(xiàn)電路如圖6所示,其開通信號由時鐘脈沖觸發(fā);關(guān)斷信號由變壓器原邊電流信號和輸出電壓反饋信號決定。變壓器原邊的電流反饋信號(由采樣電阻經(jīng)CS端得到)放大后,與輸出電壓反饋信號(Reg)比較,當(dāng)二者電壓信號相等時,PWM比較器翻轉(zhuǎn),關(guān)斷PWM輸出脈沖信號。輸出脈沖的最大占空比由CLK信號的占空比決定。

2.4 保護電路模塊的實現(xiàn)

為提高系統(tǒng)的可靠性,控制電路需要各種保護功能,如輸入過壓保護、輸入欠壓保護、開環(huán)狀態(tài)保護、過載保護以及峰值電流限幅保護等。保護功能模塊可以由比較電路實現(xiàn)。將監(jiān)測信號(如電源電壓Vcc、輸出電壓反饋信號VFB及電流反饋信號isense等)分別與給定的參考電壓進行比較,當(dāng)被監(jiān)測信號超過參考電壓值時,錯誤比較器(Error CMP)將立即翻轉(zhuǎn),并通過錯誤鎖存器(Error Latch)鎖定PWM輸出信號,從而達到保護功能。

3 實驗驗證及結(jié)果分析

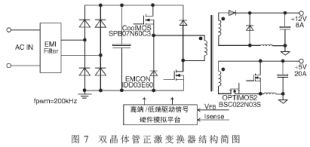

為了驗證此方法的可行性,筆者以Infineon公司的TDA16888 開關(guān)電源Demo板為基礎(chǔ),利用通用硬件模擬平臺模擬控制芯片TDA16888 PWM控制級的功能,并對其部分控制策略進行相應(yīng)的改進。TDA16888 PWM控制級的硬件模擬電路如圖6所示。功率電路板為200瓦多路輸出雙晶體管正激變換器,其結(jié)構(gòu)簡圖如圖7所示。

圖8和圖9為實驗波形圖。其中,圖8為軟啟動狀態(tài)的波形圖,通道1為CoolMOS門驅(qū)動信號,通道2為軟啟動電壓VSoftStart,通道3為反饋電壓Vrge,通道4為放大后的電流反饋信號Vrmp。從此波形可以看出,軟啟動過程大約為90ms。

?

圖9為正常工作狀態(tài)的波形圖,通道1至通道4的信號與圖9相同。從此波形可以看出,門驅(qū)動信號的下降沿由反饋電壓Vreg和放大后的電流反饋信號Vrmp決定;其上升沿由固定頻率的時鐘脈沖決定。

實驗證明,此硬件模擬開發(fā)平臺可以很好地模擬電流型PWM控制器。

針對開關(guān)電源控制器開發(fā)過程中軟件仿真的不足,本文提出并設(shè)計了一套基于FPGA的通用IC控制器硬件模擬開發(fā)平臺。此平臺充分利用FPGA的通用性和靈活性,在IC開發(fā)過程中對其進行硬件模擬,直接從硬件對技術(shù)方案進行論證,大大提高了IC控制器的開發(fā)周期。實驗結(jié)果表明,此方案確實可行,并具有廣泛的實用價值。

參考文獻

1 Memec Design.Memec Spartan-3 LC User′s Guide,V2.0.Memec Design,2004;(6)

2 Xilinx.Spartan-3 FPGA Family:Complete Data Sheet,V1.6.Xilinx,January 17,2005

3 Xilinx.Libraries Guide ISE6.3i.February 25,2003

4 Infineon Technologies.TDA16888 Data Sheet.Infineon Tech-nologies AG,F(xiàn)ebruary 28,2000

5 Infineon Technologies.TDA16888 Application Note:200W SMPS Demonstration Board II.Infineon Technologies AG,V1.0.September,2004