0 引言

近年來(lái),隨著數(shù)字信號(hào)" target="_blank">數(shù)字信號(hào)處理技術(shù)的迅猛發(fā)展,數(shù)字信號(hào)處理技術(shù)廣泛地應(yīng)用于各個(gè)領(lǐng)域。因此對(duì)作為模擬和數(shù)字系統(tǒng)之間橋梁的模數(shù)轉(zhuǎn)換器" target="_blank">模數(shù)轉(zhuǎn)換器(ADC)的性能也提出了越來(lái)越高的要求。低電壓高速ADC在許多的電子器件的應(yīng)用中是一個(gè)關(guān)鍵部分。由于其他結(jié)構(gòu)諸如兩步快閃結(jié)構(gòu)或內(nèi)插式結(jié)構(gòu)都很難在高輸入頻率下提供低諧波失真,因此流水線結(jié)構(gòu)在高速低功耗的ADC應(yīng)用中也成為一個(gè)比較常用的結(jié)構(gòu)。

作為流水線ADC前端的采樣保持電路是整個(gè)系統(tǒng)的關(guān)鍵模塊電路之一。設(shè)計(jì)一個(gè)性能優(yōu)異的采樣保持電路是避免采樣歪斜(timing skew)最直接的方法。

本文基于TSMC 0.25μm CMOS工藝,設(shè)計(jì)了一個(gè)具有高增益、高帶寬的OTA,并且利用該OTA構(gòu)造一個(gè)適用于10位,100 MS/s的流水線ADC的采樣保持電路。文章討論了適宜采用的跨導(dǎo)運(yùn)算放大器的結(jié)構(gòu)以及對(duì)其性能產(chǎn)生影響的因素和采樣保持電路的結(jié)構(gòu),最后給出了仿真結(jié)果。

1 OTA的設(shè)計(jì)

1.1 OTA結(jié)構(gòu)

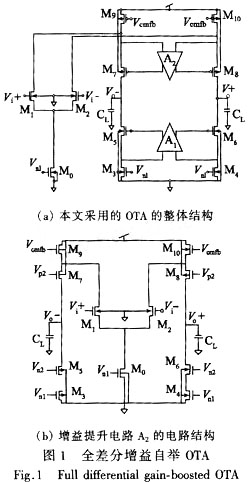

在2.5 V的電源電壓下,雖然套筒式共源共柵結(jié)構(gòu)具有高速、高頻、低功耗的特點(diǎn),但由于套筒式結(jié)構(gòu)的輸出擺幅低,不太適合低壓下的設(shè)計(jì)。因此折疊式共源共柵的運(yùn)放結(jié)構(gòu)是一個(gè)較好的選擇,如圖1(a)所示。由于該OTA將用于閉環(huán)結(jié)構(gòu),為了減少輸入端的寄生電容,采用了NMOS管作為輸入管。

本文采用如圖1(b)所示的增益自舉電路結(jié)構(gòu)。放棄使用四個(gè)單端輸入-單端輸出的運(yùn)放是因?yàn)楹笳卟粌H會(huì)增加功耗和面積,而且由于不可避免地采用電流鏡結(jié)構(gòu)會(huì)引入鏡像極點(diǎn),限制了OTA的頻率特性,使其單位增益帶寬變小。為了提供最大的輸出擺幅,放大器A2必須采用NMOS的輸入差動(dòng)對(duì)。同理,放大器A1必須采用PMOS作為輸入差動(dòng)對(duì)。

由于該OTA將應(yīng)用到10位,100 MS/s流水線ADC的采樣保持電路中,其增益A0應(yīng)滿足式中,

![]()

N為ADC的分辨率,B為每級(jí)的有效位數(shù)。對(duì)于本例,N=10,B=1,則A0>72.25 dB。對(duì)于如此大的直流增益,即使采用了增益自舉電路結(jié)構(gòu),主運(yùn)放和輔助運(yùn)放的增益還是要達(dá)到40 dB以上。以圖1(b)為例,提高折疊式共源共柵運(yùn)放的直流增益的方法有:①增加M7和M8管的跨導(dǎo)和溝道長(zhǎng)度,但是會(huì)增大寄生電容,降低運(yùn)放的次極點(diǎn)頻率。②增大M1和M2管的跨導(dǎo)和溝道長(zhǎng)度,由于次極點(diǎn)處在折疊點(diǎn)處,因此會(huì)降低運(yùn)放的次極點(diǎn)頻率。③可以增加M5和M6管的溝道長(zhǎng)度,由于信號(hào)不經(jīng)過(guò)這幾個(gè)管子,因此不會(huì)降低工作速度。

為滿足設(shè)計(jì)要求,該OTA的單位增益帶寬至少要達(dá)到800 MHz以上。根據(jù)文獻(xiàn)[4],單位增益帶寬GBW滿足

![]()

式中:K=μ0Cox,μ0是電子遷移率;Cox是單位面積的柵氧化層電容;Id1是尾電流;W1和L1分別是M1管的寬和長(zhǎng);CL是負(fù)載電容。根據(jù)式(2),提高單位增益帶寬可以通過(guò):增加尾電流,但這樣會(huì)增加功耗;增大W1,但會(huì)增大折疊點(diǎn)處的寄生電容,減小相位裕度。

同時(shí),OTA的有限增益和有限的穩(wěn)定時(shí)間會(huì)使采樣保持的實(shí)際結(jié)果與理想情況之間出現(xiàn)偏差,例如信號(hào)失真,低信噪比(SNR)等。因此需要一個(gè)快速穩(wěn)定的高直流增益OTA。為了達(dá)到設(shè)計(jì)要求,需要反復(fù)進(jìn)行模擬和折中,進(jìn)行優(yōu)化。

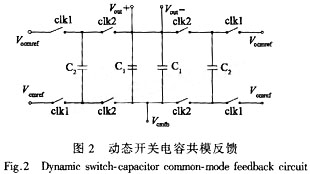

該OTA采用如圖2所示的動(dòng)態(tài)開關(guān)電容共模反饋。選擇這種共模反饋的原因是:首先,由于此共模反饋電路是離散型共模反饋結(jié)構(gòu),所以不會(huì)浪費(fèi)功耗。其次,這種共模反饋結(jié)構(gòu)也不會(huì)限制OTA的輸出擺幅。OTA的主運(yùn)放和兩個(gè)輔助運(yùn)放將采用同一個(gè)偏置電路。

1.2頻率特性與建立時(shí)間

為了使放大器穩(wěn)定,輔助運(yùn)放的單位增益帶寬必須要小于主運(yùn)放的次極點(diǎn)頻率,但要大于其主極點(diǎn)的頻率。即

式中:ω3是主運(yùn)放的-3 dB帶寬;ω4是輔助運(yùn)放的單位增益帶寬;ω6是主運(yùn)放的次極點(diǎn)。

除了對(duì)于放大器穩(wěn)定性的考慮之外,還需要對(duì)OTA的建立時(shí)間進(jìn)行考慮。減少OTA建立時(shí)間最有效的方法是減小doublets的影響。

因此,式(3)的范圍就顯得太大了,根據(jù)文獻(xiàn)[5],輔助運(yùn)放的單位增益極點(diǎn)應(yīng)該大于整個(gè)閉環(huán)回路的-3 dB帶寬,即

![]()

式中βω5是整個(gè)閉環(huán)回路的-3 dB帶寬。需要注意的是,ω4不必比βω5大太多,因?yàn)檫^(guò)分增大ω4的代價(jià)是使OTA的功耗變大。

2 采樣保持電路的結(jié)構(gòu)

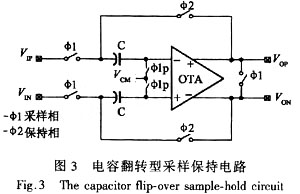

本文的采樣保持電路采用電容翻轉(zhuǎn)型結(jié)構(gòu)。如圖3所示。該結(jié)構(gòu)具有實(shí)現(xiàn)面積小、噪聲低、功耗低、保持相穩(wěn)定時(shí)間短等優(yōu)點(diǎn)。適用于高速的流水線ADC。同時(shí)采用了下極板采樣技術(shù)和全差分結(jié)構(gòu)。全差分結(jié)構(gòu)可以消除電路的共模失調(diào)誤差,抑制襯底噪聲。下極板采樣技術(shù)的應(yīng)用則可以幾乎完全抑制了在采樣時(shí)刻由于開關(guān)的電荷注入和時(shí)鐘饋通引入的非線性誤差。

3 仿真結(jié)果

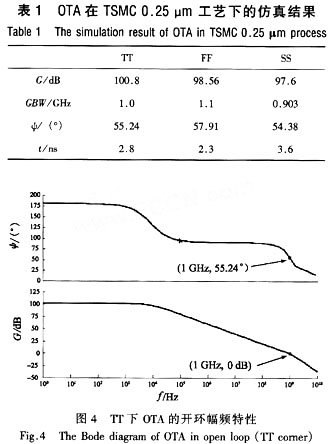

采用Cadence Spectre作為仿真工具。電源電壓為2.5 V,采用TSMC 0.25 μm CMOS工藝,在各個(gè)工藝角下對(duì)OTA進(jìn)行AC分析,仿真結(jié)果如表1所示,在TT工藝角下的波特圖如圖4所示。

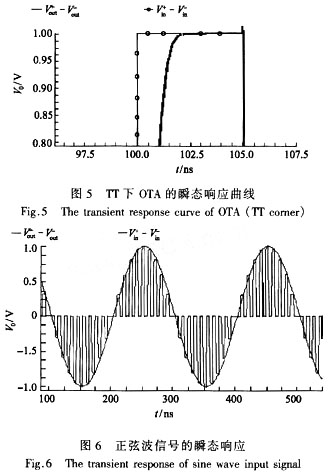

表中的建立時(shí)間t是以達(dá)到0.05%精度的建立時(shí)間進(jìn)行計(jì)算的。將OTA接成單位增益放大器,輸入幅值為1 V的差分階躍信號(hào),得到如圖5所示的瞬態(tài)響應(yīng)曲線。

在電路的輸入端加一個(gè)正弦波信號(hào)(Vpp為2 V,頻率為10 MHz),輸出端在保持相時(shí)能在4 ns內(nèi)穩(wěn)定到1 V,這滿足100 MHz采樣頻率的要求。