摘 要: 結合FPGA的結構,針對高速數(shù)據(jù)采集系統(tǒng)" title="高速數(shù)據(jù)采集系統(tǒng)">高速數(shù)據(jù)采集系統(tǒng)中觸發(fā)控制單元" title="控制單元">控制單元的特點,提出了采用優(yōu)化結構的可變長度移位寄存器" title="移位寄存器">移位寄存器改進基于FPGA的觸發(fā)控制單元的方法,同時從器件的搭配和寄存器結構兩方面探討了可變長度移位寄存器的優(yōu)化方案,并給出了應用示例。

關鍵詞: 觸發(fā)控制單元 可變長度移位寄存器 FPGA

觸發(fā)控制單元是高速數(shù)據(jù)采集系統(tǒng)的重要組成部分,而可變長度移位寄存器在觸發(fā)控制單元中起彈性緩存、數(shù)控延遲等作用。觸發(fā)控制單元根據(jù)不同的條件設置時間窗口,并對窗口內(nèi)的數(shù)據(jù)進行操作,在線完成實時事例選判和控制。由于高速數(shù)據(jù)采集系統(tǒng)的采樣頻率高,單位時間內(nèi)產(chǎn)生的數(shù)據(jù)和事件多,不同時間窗口所需的移位寄存器的長度變化會很大。一方面,觸發(fā)控制單元作為高速數(shù)據(jù)采集系統(tǒng)的一個組成部分,常常與系統(tǒng)的其他組成部分共享有限的FPGA資源;另一方面,一個數(shù)據(jù)采集系統(tǒng)往往有多路數(shù)據(jù)采集通道,需多個觸發(fā)控制單元支持。因此,提高資源利用率對構建用于觸發(fā)控制的可變長度移位寄存器來說非常重要。

本文以最大可變長度為N、寬度為1bit的移位寄存器為模型,討論如何從結構上優(yōu)化可變長度移位寄存器和有效的FPGA實現(xiàn)。至于寬度不為1bit的情況,可以此類推。

1 可變長度移位寄存器的常用結構

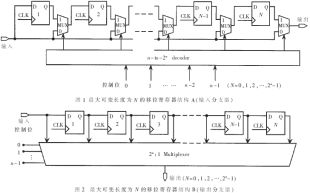

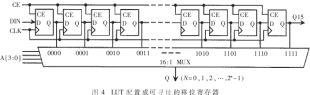

通常可變長度移位寄存器的結構可分為兩種:一種是輸入分支型(結構A),如圖1所示;另一種是輸出分支型(結構B),如圖2所示。

結構A與結構B有兩個共同點:第一,都是由觸發(fā)器鏈路加數(shù)據(jù)流向控制邏輯組成;第二,每級觸發(fā)器的輸入輸出都是信號節(jié)點,因而各級都需要對本級節(jié)點的信號流向進行控制。結構A用n-to-2n譯碼器來控制信號流向,結構B則用2n:1多路復用器" title="多路復用器">多路復用器控制信號流向。對于基本邏輯單元" title="邏輯單元">邏輯單元為查找表(LUT)+觸發(fā)器(FF)+多路復用器(MUX)結構的FPGA來說,直接采用結構A與結構B構造較長的移位寄存器時,觸發(fā)器鏈和復雜的組合邏輯會消耗很多資源,即這兩種結構不宜用于較長的可變長度移位寄存器。

2 解決方案

為解決上述問題,可以采用如下兩個方法:

(1)優(yōu)化功能結構與硬件結構的搭配。根據(jù)移位寄存器結構類型,選擇適宜的FPGA芯片以提高資源利用率,降低資源消耗。

(2)優(yōu)化移位寄存器結構。采用FPGA片內(nèi)RAM來實現(xiàn)移位寄存器,利用片內(nèi)RAM速度快、數(shù)量大的優(yōu)點,直接減少基本邏輯單元的消耗,提高資源利用率。

2.1 優(yōu)化功能結構與硬件結構的搭配

通過調(diào)整FPGA芯片類型與移位寄存器結構類型的搭配,可以提高資源利用率,降低資源消耗。下面以結構B為例,闡述如何應用Xilinx公司的Spartan-3系列芯片高效地實現(xiàn)N=128的可變長度移位寄存器。

2.1.1 實現(xiàn)原理

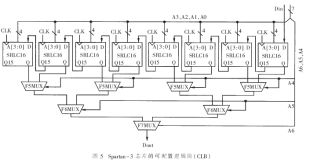

Spartan-3系列芯片的每個可配置邏輯塊CLB[1]如圖3所示,包含8個LUT、8個DFF和8個2:1多路復用器(4個F5MUX,2個F6MUX,1個F7MUX,1個F8MUX),而每個LUT都能配置成移位寄存器模式(SRL),相當于一個16級的可逐級尋址的移位寄存器。如圖4所示,一個LUT就包含了構成結構B所需的全部要素,從而有效地實現(xiàn)N=16的可變長度移位寄存器[2]。Q15是用于多級級聯(lián)實現(xiàn)N>16的移位寄存器的進位輸出。

?

2.1.2 應用示例

利用Spartan-3系列芯片的一個CLB(相當于8個基本邏輯單元)就可以構成N=128的可變長度移位寄存器,如圖5所示。作為對比,如果不調(diào)整FPGA芯片類型與移位寄存器結構類型的搭配,比如直接采用Altera Cyclone II芯片,按結構A實現(xiàn)N=128的可變長度移位寄存器,則需消耗169個基本邏輯單元(由Quartus II編譯)。

?

2.2 優(yōu)化移位寄存器結構

通過優(yōu)化移位寄存器結構,采用FPGA片內(nèi)RAM來實現(xiàn)移位寄存器,利用片內(nèi)RAM速度快、數(shù)量大的優(yōu)點,直接減少基本邏輯單元的消耗,提高資源利用率。

2.2.1 實現(xiàn)原理

FPGA片內(nèi)RAM常見有兩種,一種是分布式RAM(Distributed RAM),如Xilinx Spartan-3的LUT,每個LUT都可作為16位的RAM使用;另一種是嵌入式塊RAM(Block RAM),如Xilinx Spartan-3的18KB塊RAM、Altera Cyclone II的4KB塊RAM(M4K)。結構A與結構B中,各級都需要對本級節(jié)點的信號流向進行控制,這種形式限制了FPGA嵌入式塊RAM的使用。為此,設計了結構C——梯級組合型,如圖6所示,這種結構非常利于采用片內(nèi)RAM來實現(xiàn)移位寄存器。

分析結構C,梯級組合型有兩個要素:一是2:1多路復用器,每個都有單獨的控制位,共n個,而且n〈〈N,二者呈指數(shù)關系;二是不同長度的移位寄存器組成的梯級,初級(第0級)由20=1個觸發(fā)器組成,第1級由21=2個觸發(fā)器鏈接組成,第2級由22=4個觸發(fā)器鏈接組成,...,第N級由2N個觸發(fā)器鏈接組成。在梯級組合型的結構中,不需要對每個觸發(fā)器的輸入輸出都控制,只需通過控制位BI對各個梯級的輸入輸出控制就可以實現(xiàn)分辨率為1的長度連續(xù)變化,寄存器的長度N=BN×2N+…+B2×22+B1×21+B0×20。

例如,對于最大N=255(控制字為8位)且采用結構C的可變長度移位寄存器,要實現(xiàn)長度為5的移位寄存器,只需設置控制字為00000101B即可;要實現(xiàn)長度為255的移位寄存器,只需設置控制字為1111111B即可。由于同一個梯級里,除頭尾兩級外,其他各級不再有信號流向控制,且各梯級觸發(fā)器鏈的長度為2n,可以方便地利用FPGA嵌入式塊RAM和廠商提供的經(jīng)過優(yōu)化的宏功能模塊來實現(xiàn)長度較大的梯級,從而提高資源利用率。

2.2.2 應用示例

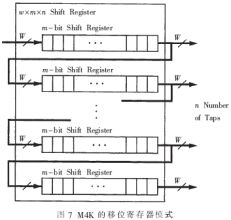

以Altera Cyclone II[3]的M4K為例,每個M4K塊RAM有4 608個存儲位(其中包括512個奇偶位),操作頻率高達250MHz,M4K工作于移位寄存器模式時的結構如圖7所示,數(shù)據(jù)寬度(w)、每段長度(m)、抽頭數(shù)(n)的關系可方便地在廠商提供的基于RAM的移位寄存器宏模塊“altshift_taps”中設置。當w×m×n不大于4 608且w×m不大于36時,消耗一個M4K和少量基本邏輯單元;當不能滿足上述兩項中任意一項,開發(fā)工具會自動連接多個M4K。通過調(diào)整w、m、n的組合,M4K能以多種方式高效實現(xiàn)結構C的梯級。

例如,構造一個1024位的梯級,可以設置w=1、m=256、n=4,占用13個LUT,8個寄存器,1個M4K;構造一個4 096位的梯級,可以設置w=1、m=256、n=16,依然只占用13個LUT,8個寄存器,1個M4K。為進一步提高M4K的利用率,可以設置w=32、m=128、n=1,只占用12個LUT,7個寄存器,1個M4K就能得到32個長度為128位的移位寄存器段,將這些寄存器段自行連接,用一個M4K能同時得到如下的梯級:128位、256位(2段串連)、512位(2段串連)、1024位(8段串連)、2048位(16段串連),最大限度地利用了M4K的RAM資源。

作為對比,仍以Altera Cyclone II芯片為例,如果用基于基本邏輯單元的移位寄存器宏模塊“LPM_SHIFTREG”來實現(xiàn)1 024位的梯級和4096位的梯級,則分別需1 024(256×4)個LUT和4096(256×16)個LUT,資源開銷較大。可見,結構C非常利于實現(xiàn)可變長度較長的移位寄存器。

可變長度移位寄存器是非常有用的邏輯結構。對高速數(shù)據(jù)采集系統(tǒng)觸發(fā)控制單元來說,應用優(yōu)化后的可變長度移位寄存器可以提高其信噪比,改善其可靠性和靈活性。另外,采用可變長度移位寄存器可以減小死區(qū)時間,從而改善觸發(fā)控制單元重復觸發(fā)的性能。這些改善在本單位設備的實際應用中起到了良好的作用。

參考文獻

1 Spartan-3 FPGA family:complete data sheet. XILINX, 2004;3(8)

2 Using look-up tables as shift registers(SRL16) in Spartan-3 generation FPGAs. XILINX, 2005;1(5)

3 Cyclone II device handbook. Altera Corporation, 2005;1(11)