與其他常用的自動(dòng)識(shí)別技術(shù)如條形碼和磁條一樣,,無線射頻識(shí)別(RFID)技術(shù)也是一種自動(dòng)識(shí)別技術(shù),。每一個(gè)目標(biāo)對象在射頻讀卡器中對應(yīng)唯一的電子識(shí)別碼(UID),,或者“電子標(biāo)簽”。標(biāo)簽附著在物體上標(biāo)識(shí)目標(biāo)對象,如紙箱、貨盤或包裝箱等,。射頻讀卡器(應(yīng)答器)從電子標(biāo)簽上讀取識(shí)別碼。

基本的RFID系統(tǒng)由三部分組成:天線或線圈,、帶RFID解碼器的收發(fā)器和RFID電子標(biāo)簽(每個(gè)標(biāo)簽具有唯一的電子識(shí)別碼),。表1顯示了常用的四個(gè)RFID頻率及其潛在的應(yīng)用領(lǐng)域。其中,,目前商業(yè)上應(yīng)用最廣的是超高頻(UHF),,它在供應(yīng)鏈管理中有可能得到廣泛的應(yīng)用,。

EPC電子標(biāo)簽

EPC表示電子產(chǎn)品代碼,是RFID電子標(biāo)簽的標(biāo)準(zhǔn),,它包括電子標(biāo)簽的數(shù)據(jù)內(nèi)容和無線通信協(xié)議,。EPC標(biāo)準(zhǔn)將條形碼規(guī)范中的數(shù)據(jù)信息標(biāo)準(zhǔn)與ANSI或其他標(biāo)準(zhǔn)化組織(802.11b)制定的無線數(shù)據(jù)通信標(biāo)準(zhǔn)結(jié)合在一起,。目前應(yīng)用在供應(yīng)鏈管理中的EPC標(biāo)準(zhǔn),,屬于第二代EPC Class-1標(biāo)準(zhǔn)。

Class-1標(biāo)簽在出廠時(shí)已經(jīng)被寫入

,,但也是可以現(xiàn)場下載,。通常情況下,一旦標(biāo)簽已被寫入,,內(nèi)存即被鎖定不可再次寫入信息,。Class-1標(biāo)簽采用常規(guī)的分組傳輸協(xié)議—讀卡器發(fā)送包含相關(guān)命令和數(shù)據(jù)的數(shù)據(jù)包,標(biāo)簽隨后做出響應(yīng),。

惡劣的讀卡器應(yīng)用環(huán)境

RFID的應(yīng)用環(huán)境可能非常惡劣,。信道的工作頻率是免許可的工業(yè)、科技與醫(yī)藥(ISM)頻帶,。此頻帶中的RFID讀卡器受到來自無繩電話,、無線耳麥、無線數(shù)據(jù)網(wǎng)絡(luò)以及其他臨近讀卡器的干擾,。必須將每一讀卡器的RF接收器前端設(shè)計(jì)為能夠抵御強(qiáng)干擾信號(hào),,避免產(chǎn)生可導(dǎo)致詢問錯(cuò)誤的失真。接收器的噪聲必須保持在較低的水平,,以便具備足夠的動(dòng)態(tài)范圍,,從而以無錯(cuò)方式檢測出低電平標(biāo)簽響應(yīng)信號(hào)。

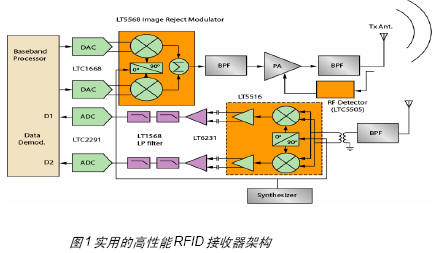

圖1中所示的讀卡器RF射頻收發(fā)器,,是一個(gè)成熟的設(shè)計(jì),,能夠在存在大量干擾源的惡劣環(huán)境中穩(wěn)定地工作。發(fā)射器和接收器都帶有一個(gè)高動(dòng)態(tài)范圍直接轉(zhuǎn)換調(diào)制器和解調(diào)器,,因此最大限度地提高了穩(wěn)定性并降低了成本,。

實(shí)用和可靠的射頻接收器設(shè)計(jì)

接收器的核心是Linear公司的LT5516,這是一種高度集成化的直接轉(zhuǎn)換正交解調(diào)器,,芯片上提供了一個(gè)精確正交移相器(0度至90度),。來自天線的信號(hào)在通過射頻濾波器之后,通過一個(gè)不平衡變壓器直接輸入到解調(diào)器輸入端口,。由于LT5516的噪聲系數(shù)很低,,在不需要低噪放大器(LNA)的情況下,仍能保持其21.5dBm IIP3和9.7dB P1dB的性能,。

在接收數(shù)據(jù)時(shí),,讀卡器發(fā)射連續(xù)載波(未調(diào)制),,以便為標(biāo)簽提供電源。在收到請求后,,電子標(biāo)簽通過對載波進(jìn)行調(diào)幅,,響應(yīng)一個(gè)碼流。所采用的調(diào)制方式為幅移鍵控(ASK)或者反相-幅移鍵控鍵控(PR-ASK),。解調(diào)器帶有兩個(gè)正交移相檢出式輸出端口,,因此具備天然的分集接收功能。如果由于多路或相位取消導(dǎo)致某個(gè)通道無法接收信號(hào),,另一條通道(移相90度)就可接收較強(qiáng)的信號(hào),,反之亦然。這樣,,整體接收可靠性就得以提高,。

一旦解調(diào)完成,即可將I(相內(nèi))和Q(正交相位)差分輸出信號(hào)以AC方式耦合至一個(gè)運(yùn)算放大器(被配置為一個(gè)差分放大器),,隨后被轉(zhuǎn)換為單端輸出信號(hào),。這個(gè)時(shí)候應(yīng)將高通角頻率設(shè)置為5KHz,低于接收數(shù)據(jù)流的最小信號(hào)頻率,,高于最大多普勒頻率(可能被運(yùn)動(dòng)標(biāo)簽采用),,同時(shí)保持高于電力線頻率(60Hz)。這樣,,輸出信號(hào)就能利用被配置為四階低通的LT1568順利穿過低通濾波器,。低通角頻率應(yīng)被設(shè)置為5MHz,以便最大碼流信號(hào)穿過濾波器,,達(dá)到基帶,。

基帶信號(hào)然后被一個(gè)雙路低功耗模數(shù)轉(zhuǎn)換器(LTC2291,分辨率為12位)進(jìn)行數(shù)字化處理,。由于標(biāo)簽碼流的帶寬為5KHz至5MHz,,LTC2291能夠以25MSps的速率進(jìn)行充分的采樣,從而精確地捕獲解調(diào)信號(hào),。在需要的時(shí)候,,還可在基帶DSP中實(shí)現(xiàn)額外的數(shù)字濾波。這樣,,接收器就能具備最大的邏輯閾值設(shè)置靈活性,,該設(shè)置可由基帶處理器以數(shù)字化方式執(zhí)行。

基帶任務(wù)和數(shù)字化射頻信道化處理,,可提高用全FPGA解決方案實(shí)現(xiàn)的吸引力和集成度,。

高動(dòng)態(tài)范圍射頻發(fā)射器設(shè)計(jì)

發(fā)射器集成了一個(gè)鏡像抑制直接轉(zhuǎn)換式調(diào)制器。LT5568具備很高的線性度和較低的背景噪聲,,因此能夠?yàn)樗l(fā)射的信號(hào)提供出色的動(dòng)態(tài)范圍性能,。調(diào)制器能夠從數(shù)模轉(zhuǎn)換器(DAC)接收正交式基帶I和Q信號(hào),,然后直接調(diào)制至900MHz發(fā)射頻率。

在內(nèi)部,,LO(本地振蕩器)被精確正交移相器分割,。經(jīng)調(diào)制的射頻信號(hào)被合并為一個(gè)單端、單邊帶射頻輸出信號(hào)(鏡像被抑制了46dBc),。此外,,調(diào)制器還帶有匹配的I和Q混合器,從而最大限度地抑制了LO載波信號(hào)(至-43dBm),。

復(fù)合調(diào)制電路具備出色的鄰道功率比(ACPR),,有助于滿足發(fā)射頻率屏蔽要求。例如,,當(dāng)調(diào)制器射頻輸出電平為-8dBm時(shí),ACPR指標(biāo)優(yōu)于-60dBc,。由于具備更出色的ACPR性能,,信號(hào)可被放大至許可的1w功率(在美國為+30dBm),或者放大至2w,,以符合歐盟規(guī)范,。在上述兩種情況下,重要的是保持電平固定,,因?yàn)樵撾娖接糜谙螂娮訕?biāo)簽提供電源,,并最大化讀卡距離。LTC5505型射頻功率檢測器的內(nèi)部溫度補(bǔ)償功能,,可準(zhǔn)確地測定功率,,提供穩(wěn)定的反饋信號(hào),以調(diào)節(jié)射頻功率放大器的輸出功率,。

基帶處理和網(wǎng)絡(luò)接口

在基帶頻率上,,F(xiàn)PGA執(zhí)行發(fā)送至DAC和來自模數(shù)轉(zhuǎn)換器(ADC)的波形的信道化任務(wù)。這一過程也被稱為數(shù)字中頻處理,,涉及濾波,、增益控制、頻率轉(zhuǎn)換和采樣率變化等,。F

PGA甚至可以并行處理多個(gè)信道,。

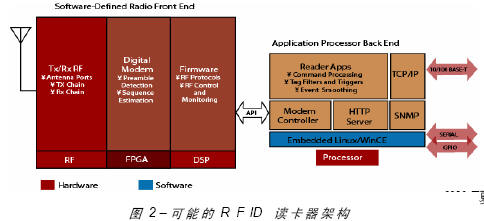

圖2顯示了一個(gè)射頻讀卡器的架構(gòu)。其他基帶處理任務(wù)包括:

·?? 先導(dǎo)字段檢測

·?? 排序估計(jì)

·?? 調(diào)制和解調(diào)(ASK,、頻移鍵控和相移鍵控)

·?? 信號(hào)產(chǎn)生

·?? 相關(guān)器處理

·?? 峰值檢測和閾值設(shè)定

·?? CRC糾錯(cuò)和校驗(yàn)和

·?? 編碼和解碼(NRZ,、Manchester、單極性,、差分雙極性和Miller)

·?? 幀檢測

·?? ID去擾

·?? 安全加密引擎

所收到的RFID標(biāo)簽數(shù)據(jù)可通過串口或網(wǎng)絡(luò)接口被傳送至企業(yè)系統(tǒng)服務(wù)器,。

這種傳統(tǒng)的架構(gòu)正逐步演變?yōu)橐粋€(gè)高級分布式 TCP/IP 網(wǎng)絡(luò)的一個(gè)部分,。在該網(wǎng)絡(luò)中,射頻讀卡器將負(fù)責(zé)管理臨近的標(biāo)簽,。在這種情況下,,射頻讀卡器就象是電子標(biāo)簽和連接至企業(yè)軟件系統(tǒng)的智化分布式數(shù)據(jù)庫之間的網(wǎng)關(guān)。

取決于硬件/軟件功能分區(qū)情況,,這些基帶任務(wù)即可在FPGA上完成,,也可在DSP上完成,或者由二者聯(lián)合執(zhí)行,。Xilinx公司推出了一個(gè)IP內(nèi)核套件,,其中包括FIR、CIC,、DDS,、DUC、DDC,、比特相關(guān)器,、正弦/余弦LUT等。這些邏輯電路非常適合執(zhí)行加密引擎任務(wù)(加密引擎采用移位寄存器和XOR),。針對Xilinx® VirtexTM-4系列的DSP48引擎十分適合執(zhí)行其他信號(hào)處理任務(wù),。

一個(gè)基帶處理器負(fù)責(zé)控制各種基帶處理任務(wù)的功能性和調(diào)度,還負(fù)責(zé)鏈路層協(xié)議,。這些基帶處理任務(wù)包括跳頻,、發(fā)送前偵聽、防沖突算法處理等,?;鶐幚砥鬟€提供了以太網(wǎng)、USB,、固件等接口,。

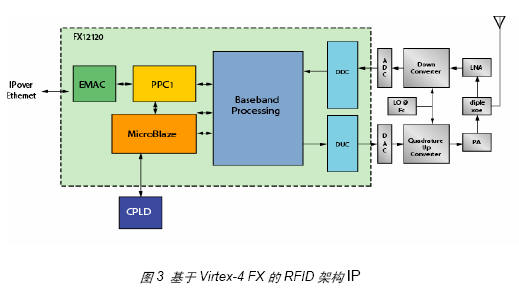

基帶任務(wù)和數(shù)字化射頻信道化處理,可提高全FPGA解決方案的吸引力和集成度,。FGPA功能,、DSP功能,以及基帶處理功能,,都可被整合于一個(gè)帶有嵌入式處理器的FPGA,。

圖 3 顯示了一個(gè)基于 FPGA 的 RFID 處理器的架構(gòu)。嵌入式處理器可以是一個(gè)硬核(譬如,,Virtex-4 FX產(chǎn)品家族采用的PowerPCTM),,還可以是一個(gè)軟核 (譬如SpartanTM設(shè)備中采用的MicroBlazeTM),甚至是PowerPC和MicroBlaze的結(jié)合體。用戶可以將內(nèi)置硬以太網(wǎng)MAC(EMAC)連接至外部以太網(wǎng)物理層,,進(jìn)而連接至以太網(wǎng),。另外,用戶還可使用面向10/100-BaseT的Lite Ethernet MAC IP,。

PowerPC/MicroBlaze 嵌入式處理器執(zhí)行以下任務(wù):

·?? EPC數(shù)據(jù)處理

·?? 協(xié)議處理

·?? 詢問調(diào)度

· TCP/IP 網(wǎng)絡(luò)接口

· 控制和監(jiān)視

· 調(diào)制解調(diào)器控制

·?? 升級代理

·?? HTTP服務(wù)器

· SNMP/MIB 處理

Xilinx千兆以太網(wǎng)系統(tǒng)參考設(shè)計(jì)(GSRD)是一個(gè)基于 EDK 的參考系統(tǒng),,能夠在基于TCP/IP的協(xié)議接口和用戶數(shù)據(jù)接口之間搭起一座高性能的橋梁。GSRD的組件具備滿足TCP/IP系統(tǒng)每比特和每包開銷要求的功能,。

Xilinx還針對Monta Vista Linux和 Treck堆棧提供了發(fā)射性能基準(zhǔn),。采用 Xilinx Platform Studio (XPS)微處理器庫定義的Nucleus PLUS RTOS,為采用MicroBlaze和PowerPC處理器的系統(tǒng)帶來了新的優(yōu)勢,。Nucleus PLUS RTOS尺寸很小,,這意味著它能夠利用片上現(xiàn)有的存儲(chǔ)器,從而最大限度降低功耗,,提高性能,。此外,廣泛的中間件使得Nucleus PLUS RTOS成為RFID后端網(wǎng)絡(luò)的理想選擇,。

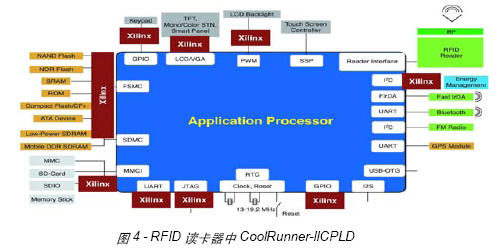

利用XilinxCoolRunnerTM-II型CPLD,,手持式射頻讀卡器可連接至硬盤驅(qū)動(dòng)器、QWERTY鍵盤,、可移動(dòng)硬盤接口、各種顯示設(shè)備和其他計(jì)算機(jī)外設(shè)(如圖4所示),。這些CPLD還能幫助應(yīng)用處理器,,并且滿足低功耗、高性能和更小芯片封裝等要求,。

結(jié)論

將來,,射頻讀卡器很可能具備前端 DSP功能,譬如射頻協(xié)議處理等,。如今,,這些功能在獨(dú)立式DSP中進(jìn)行處理,將來,,它們很有可能被集成于FPGA,。嵌入式軟處理內(nèi)核已可顯著提升DMIPS/MHz性能,不久以后,,高版

本的處理內(nèi)核將取代控制讀卡器應(yīng)用程序的后端外部處理器,,從而借助可編程邏輯最大限度地提高射頻讀卡器設(shè)備的靈活性,同時(shí)最大限度降低其成本,。