摘 要: 闡述了一種基于SOPC的步進(jìn)電機(jī)" title="步進(jìn)電機(jī)">步進(jìn)電機(jī)多軸控制器。該控制器應(yīng)用于半自動(dòng)生化分析儀中,以實(shí)現(xiàn)取樣針移位系統(tǒng)的控制功能,同時(shí)它也能夠用于其他類似如多軸聯(lián)動(dòng)的針式打印機(jī)及機(jī)器人等領(lǐng)域的多步進(jìn)電機(jī)工作的場(chǎng)合。

關(guān)鍵詞: 可編程片上系統(tǒng) 多軸控制器 步進(jìn)電機(jī) 生化儀

步進(jìn)電機(jī)是一種完全數(shù)字化的電動(dòng)執(zhí)行機(jī)構(gòu),從原理上說,其角位移與驅(qū)動(dòng)脈沖的個(gè)數(shù)成正比,在正常情況下,步進(jìn)電機(jī)具有使用簡(jiǎn)單、運(yùn)動(dòng)精確、連續(xù)運(yùn)行無累積誤差等特點(diǎn),因而被廣泛應(yīng)用于各種位置控制系統(tǒng)中。當(dāng)前由于儀器內(nèi)部的機(jī)械系統(tǒng)日益復(fù)雜,其運(yùn)動(dòng)往往是多自由度的,因而通常需要利用多個(gè)步進(jìn)電機(jī)的運(yùn)動(dòng)合成來實(shí)現(xiàn)系統(tǒng)的各種動(dòng)作。例如,對(duì)圖1所示的半自動(dòng)生化分析儀的取樣針移位系統(tǒng),該系統(tǒng)的動(dòng)作執(zhí)行就是由兩部分組成的:一是固定基座上的步進(jìn)電機(jī)控制" title="步進(jìn)電機(jī)控制">步進(jìn)電機(jī)控制取樣橫臂進(jìn)行垂直方向上的升降運(yùn)動(dòng);二是滑塊上的步進(jìn)電機(jī)控制取樣橫臂進(jìn)行水平方向上的旋轉(zhuǎn)運(yùn)動(dòng)。這兩個(gè)運(yùn)動(dòng)的合成實(shí)現(xiàn)了取樣橫臂的位置變換。

傳統(tǒng)的步進(jìn)電機(jī)多軸控制器是以微控制器(MCU)/微處理器(MPU)/專用集成電路(ASIC)/數(shù)字信號(hào)處理器(DSP)為核心,再輔以其他外圍分立器件構(gòu)成的。這種結(jié)構(gòu)的步進(jìn)電機(jī)多軸控制器的優(yōu)點(diǎn)在于其硬件結(jié)構(gòu)清晰,易于復(fù)制再現(xiàn),對(duì)于類似的應(yīng)用只需要修改其應(yīng)用軟件即可。然而對(duì)于多數(shù)實(shí)際應(yīng)用來說,單純依靠軟件的修改通常不足以使其達(dá)到其他應(yīng)用場(chǎng)合所需的要求,并且當(dāng)系統(tǒng)升級(jí)時(shí),通常需要對(duì)整個(gè)電路重新進(jìn)行設(shè)計(jì),這樣既延長(zhǎng)了升級(jí)的周期,又增加了升級(jí)成本,因而在實(shí)際應(yīng)用中受到了一定的限制。由于可編程邏輯器件(PLD)技術(shù)的飛速發(fā)展,使得單一FPGA/CPLD" title="FPGA/CPLD">FPGA/CPLD芯片內(nèi)部可以集成多個(gè)分立元件的功能,因此在對(duì)傳統(tǒng)控制器的改進(jìn)中,通常使用一個(gè)FPGA/CPLD芯片將傳統(tǒng)控制器中的數(shù)字電路" title="數(shù)字電路">數(shù)字電路部分集成到一起,從而形成具有處理器-FPGA/CPLD-模擬電路結(jié)構(gòu)形式的控制器。這類控制器比起傳統(tǒng)控制器而言,其硬件結(jié)構(gòu)的可擴(kuò)展性得到了很大的提高。這是因?yàn)镕PGA/CPLD芯片具有在不改變其引腳定義的情況下可對(duì)其內(nèi)部邏輯關(guān)系進(jìn)行重構(gòu)的特性,因而對(duì)于不同的應(yīng)用,可以通過改變FPGA/CPLD芯片的內(nèi)部結(jié)構(gòu)來滿足某些特殊的應(yīng)用需求,從而在一定程度上使得系統(tǒng)的開發(fā)升級(jí)更為簡(jiǎn)便,而且成本也更為低廉。因此,這種改進(jìn)型的多步進(jìn)電機(jī)控制器的應(yīng)用范圍也得到了很大的擴(kuò)展。但是,這種結(jié)構(gòu)的控制器也存在著這樣的問題:在FPGA外部仍然存在一個(gè)處理器。這樣不僅增加了控制器的尺寸,而且在升級(jí)處理器時(shí),硬件電路需要重新設(shè)計(jì),使升級(jí)成本仍然相對(duì)較高。

近年來,由于IP資源復(fù)用理念得到了普遍的認(rèn)同并成為主要設(shè)計(jì)方式,MCU、DSP、MPU等嵌入式處理器IP成為了FPGA應(yīng)用的核心。隨著處理器內(nèi)核以IP的形式嵌入到FPGA中,未來的電路板上可能只有兩部分電路:模擬部分(包括電源)以及FPGA芯片和一些大容量存儲(chǔ)器。這一切都表明可編程片上系統(tǒng)(SOPC)正在成為FPGA最重要的發(fā)展方向。與傳統(tǒng)多軸控制器相比,這種基于SOPC的步進(jìn)電機(jī)多軸控制器具有體積小、集成度高、硬件結(jié)構(gòu)穩(wěn)定、易于開發(fā)升級(jí)且成本低廉等特點(diǎn),尤其適用于儀器儀表內(nèi)部控制系統(tǒng)的設(shè)計(jì)。本文所論述的步進(jìn)電機(jī)多軸控制器就是基于SOPC方式的步進(jìn)電機(jī)多軸控制器。

1 基于SOPC的步進(jìn)電機(jī)多軸控制器的硬件結(jié)構(gòu)

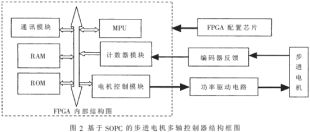

基于SOPC的步進(jìn)電機(jī)多軸控制器的結(jié)構(gòu)框圖如圖2所示。其外部電路的構(gòu)成包含模擬電路和數(shù)字電路兩部分。模擬電路包括供電電源及功率驅(qū)動(dòng)。數(shù)字電路主要為FPGA芯片及其相關(guān)電路。

如圖2,基于SOPC的步進(jìn)電機(jī)多軸控制器包含兩部分:FPGA芯片及其配置芯片的數(shù)字部分和電機(jī)控制及位置反饋部分。其中,虛線框內(nèi)部表示FPGA芯片的內(nèi)部結(jié)構(gòu),空心箭頭表示FPGA芯片內(nèi)部的數(shù)據(jù)連線,實(shí)心箭頭表示外部連線。FPGA芯片內(nèi)部由MPU模塊、通訊模塊、RAM模塊、ROM模塊、計(jì)數(shù)器模塊、電機(jī)控制模塊" title="控制模塊">控制模塊等構(gòu)成。當(dāng)控制器失電時(shí),這些模塊信息存儲(chǔ)在配置芯片中,等到系統(tǒng)重新上電時(shí),F(xiàn)PGA芯片再?gòu)呐渲眯酒凶x取其配置信息,重構(gòu)內(nèi)部模塊結(jié)構(gòu)。MPU模塊是整個(gè)控制器的核心,它的功能等同于事實(shí)的微處理器。它通過通訊模塊與外部主機(jī)進(jìn)行數(shù)據(jù)的交換,并將數(shù)據(jù)存儲(chǔ)在RAM模塊中。RAM模塊同時(shí)還用于暫存MPU模塊執(zhí)行ROM模塊所存儲(chǔ)的程序段時(shí)的某些中間過程值,而MPU則根據(jù)ROM模塊中程序執(zhí)行的結(jié)果輸出相應(yīng)的控制信號(hào)給電機(jī)控制模塊。電機(jī)控制模塊的輸出連接到實(shí)際的芯片引腳上,以驅(qū)動(dòng)相應(yīng)的功率驅(qū)動(dòng)電路工作,從而實(shí)現(xiàn)步進(jìn)電機(jī)的運(yùn)轉(zhuǎn)。在閉環(huán)控制時(shí),步進(jìn)電機(jī)軸端的編碼器模塊輸出編碼信號(hào)。該信號(hào)經(jīng)編碼器反饋電路進(jìn)行隔離等處理之后,由FPGA芯片內(nèi)部的計(jì)數(shù)器模塊進(jìn)行計(jì)數(shù),并將結(jié)果傳輸給MPU模塊進(jìn)行處理,從而形成位置/速度的閉環(huán)控制。圖2只表示了單個(gè)步進(jìn)電機(jī)閉環(huán)控制的結(jié)構(gòu)框圖,對(duì)于多軸步進(jìn)電機(jī)而言,F(xiàn)PGA芯片只需要增加相應(yīng)的功率驅(qū)動(dòng)電路及編碼器反饋電路即可。電機(jī)控制模塊和計(jì)數(shù)器模塊都在FPGA內(nèi)部集成,因而硬件電路的結(jié)構(gòu)較為穩(wěn)定。

由于IP技術(shù)的飛速發(fā)展,在圖2中的FPGA芯片內(nèi)部模塊中,MPU、ROM、RAM、計(jì)數(shù)模塊等的IP核都可以很方便地獲得,而電機(jī)控制模塊由于與具體的功率放大電路實(shí)際相關(guān),因而通常需要用戶自行設(shè)計(jì)。下面介紹這一模塊的設(shè)計(jì)。

2 二相步進(jìn)電機(jī)控制模塊結(jié)構(gòu)

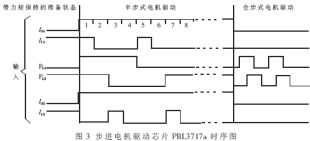

以小慣量的二相步進(jìn)電機(jī)為例闡述步進(jìn)電機(jī)控制模塊的結(jié)構(gòu)。該步進(jìn)電機(jī)由兩片PBL3717a芯片所驅(qū)動(dòng),其驅(qū)動(dòng)時(shí)序及其控制模塊如圖3、圖4所示。

?

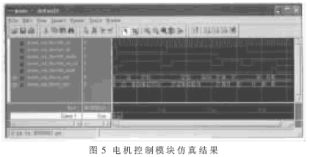

在控制模塊中,mtr_cp為步進(jìn)電機(jī)的脈沖輸入端,每個(gè)脈沖驅(qū)動(dòng)步進(jìn)電機(jī)前進(jìn)/后退一步,脈沖頻率即為步進(jìn)電機(jī)運(yùn)行的速度,因此這個(gè)脈沖信號(hào)由MPU模塊根據(jù)ROM內(nèi)部程序的執(zhí)行結(jié)果輸出。mtr_dir為步進(jìn)電機(jī)的正/反轉(zhuǎn)切換信號(hào),mtr_mode為步進(jìn)電機(jī)全/半步運(yùn)行方式選擇,mtr_on_off是電機(jī)的啟停位,該位置1時(shí),mtr_cp能夠驅(qū)動(dòng)步進(jìn)電機(jī)工作;為0時(shí),mtr_cp脈沖被封鎖。設(shè)置該位的目的是為了在多個(gè)步進(jìn)電機(jī)工作時(shí)分別控制各個(gè)電機(jī)的啟停而不影響到其他電機(jī)的運(yùn)行狀態(tài)。mtr_reset是控制模塊復(fù)位信號(hào),A_out為圖3中下標(biāo)為A的驅(qū)動(dòng)芯片控制信號(hào),B_out為圖3中下標(biāo)為B的驅(qū)動(dòng)芯片的控制信號(hào)。步進(jìn)電機(jī)的控制模塊的仿真波形圖如圖5所示。從圖5可以看出,仿真波形完全符合圖2中步進(jìn)電機(jī)的驅(qū)動(dòng)時(shí)序,即控制模塊的設(shè)計(jì)滿足預(yù)定的設(shè)計(jì)需求。

?

由上分析,利用上述多個(gè)步進(jìn)電機(jī)控制模塊以圖6所示的方式進(jìn)行適當(dāng)?shù)倪B接,就能夠構(gòu)成本文所論述的基于SOPC的步進(jìn)電機(jī)多軸控制器。由于MPU、ROM、RAM、電機(jī)控制模塊等都是以功能模塊的形式集成在FPGA芯片內(nèi)部,因此大大縮小了基于SOPC的步進(jìn)電機(jī)多軸控制器的尺寸。這些功能模塊可以根據(jù)實(shí)際的應(yīng)用進(jìn)行添加或刪除(即對(duì)FPGA芯片的內(nèi)部邏輯結(jié)構(gòu)進(jìn)行重構(gòu)),因此極大地增強(qiáng)了系統(tǒng)設(shè)計(jì)的靈活性,能更好地滿足不同應(yīng)用領(lǐng)域的需求。

IP技術(shù)的飛速發(fā)展使得開發(fā)人員很容易獲得多數(shù)通用模塊的可復(fù)用IP核,從而減輕了開發(fā)人員的負(fù)擔(dān),縮短了開發(fā)周期。當(dāng)系統(tǒng)需要升級(jí)時(shí),也不需要對(duì)硬件電路重新設(shè)計(jì),只需通過修改FPGA中相應(yīng)模塊的配置文件,因此節(jié)約了控制器的升級(jí)成本。同時(shí),由于MPU模塊的功能與實(shí)際的微處理器相同,因而在微處理器上可運(yùn)行的控制程序也可以很容易移植到MPU模塊中運(yùn)行。為了便于闡述基于SOPC的步進(jìn)電機(jī)多軸控制器,本文側(cè)重于闡述多個(gè)步進(jìn)電機(jī)同速恒速運(yùn)行的情況。對(duì)于變速運(yùn)行的情況,可通過在MPU的脈沖輸出端和各電機(jī)控制模塊的脈沖輸入端之間插入MPU可控的分頻模塊來獲得,同時(shí)增加插補(bǔ)模塊以實(shí)現(xiàn)不同電機(jī)之間的聯(lián)動(dòng)功能。

本文所述的基于SOPC的步進(jìn)電機(jī)多軸控制器應(yīng)用于半自動(dòng)生化分析儀的取樣針移位系統(tǒng)中,能夠?qū)崿F(xiàn)傳統(tǒng)步進(jìn)電機(jī)多軸控制器的所有控制功能,控制器的尺寸小于傳統(tǒng)控制器;當(dāng)控制器的數(shù)字電路部分需要修改時(shí),無需更換控制器的實(shí)際硬件電路,大大方便了控制器的研究設(shè)計(jì)工作并節(jié)約了相應(yīng)的開發(fā)成本。

參考文獻(xiàn)

1 任艷穎,王 彬. IC設(shè)計(jì)基礎(chǔ).西安:西安電子科技大學(xué)出版社,2003

2 Armstrong J R, Gray F G著,李宗伯,王蓉暉等譯.VHDL設(shè)計(jì) 表示和綜合.北京:機(jī)械工業(yè)出版社,2002

3 徐 欣,于紅旗.基于FPGA的嵌入式系統(tǒng)設(shè)計(jì)(Xilinx Edition).北京:機(jī)械工業(yè)出版社,2005

4 譚建成.電機(jī)控制專用集成電路.北京:機(jī)械工業(yè)出版社,2004