對(duì)于200Mbps以上速率的信號(hào),如果忽略寄生阻抗和阻抗不連續(xù)性的問(wèn)題,將會(huì)在傳輸線上產(chǎn)生增加性噪音,并出現(xiàn)資料位元誤碼。本文將以基礎(chǔ)型高畫(huà)質(zhì)數(shù)字視頻路由器的處理方式為例,詳細(xì)解說(shuō)上述問(wèn)題。

當(dāng)資料傳輸速率位于400Mbps至1.5Gbps之間時(shí),信號(hào)路徑(signal path)就會(huì)形成傳輸線(transmission line)。在這個(gè)傳輸速度范圍內(nèi),信號(hào)路徑模型必須包括電纜或底板中的電抗性寄生分量。高速資料傳輸帶來(lái)的問(wèn)題不僅僅是資料傳輸速率本身的問(wèn)題,快速的信號(hào)邊緣變換率包含甚至更高的頻率分量,這些高頻分量在分布式阻抗環(huán)境中的傳輸性能更差。對(duì)于200Mbps以上速率的信號(hào),如果忽略寄生阻抗和阻抗不連續(xù)性的問(wèn)題,將會(huì)在傳輸線上產(chǎn)生增加性噪音,并出現(xiàn)資料位元誤碼。

高速信號(hào)傳輸實(shí)例分析

面對(duì)上述的問(wèn)題,我們以基礎(chǔ)型高畫(huà)質(zhì)(High-Definition,HD)數(shù)字視頻路由器的處理方式為例進(jìn)行解說(shuō)。HD視頻路由器可管理來(lái)自于廣播、工作室或者節(jié)目制作設(shè)備之間的多項(xiàng)HD節(jié)目來(lái)源資料串流。HD視頻管道是在270Mbps到高達(dá)1.485Gbps的速率范圍內(nèi)運(yùn)作,它需要被仔細(xì)地設(shè)計(jì)并採(cǎi)用一致的設(shè)計(jì)方法,以確保交換路由器系統(tǒng)不會(huì)降低視頻資料的完整性。

圖1︰高畫(huà)質(zhì)視頻路由器圖解。

在圖1的這個(gè)系統(tǒng)中,可適應(yīng)均衡器(EQ)直接由BNC連接器接收HD信號(hào)。一個(gè)公共底板將信號(hào)從輸入卡連接到開(kāi)關(guān)卡,以輸出到目標(biāo)信號(hào)管道。信號(hào)從EQ經(jīng)過(guò)近8英寸的PCB,點(diǎn)對(duì)點(diǎn)傳輸?shù)降装暹B接器,然后透過(guò)3到15英寸的底板(長(zhǎng)度取決于所使用的插槽類型)傳輸?shù)降诙€(gè)連接器,之后再經(jīng)過(guò)8英寸的PCB到交叉點(diǎn)開(kāi)關(guān)元件的輸入。一個(gè)重組時(shí)脈(re-clocker)/線纜驅(qū)動(dòng)器直接連接到交叉點(diǎn)開(kāi)關(guān)的輸出以驅(qū)動(dòng)信號(hào)在電纜上的傳輸。這些HD視頻路由器系統(tǒng)已模組化,可能具有8個(gè)到1000個(gè)輸入/輸出信號(hào)管道。也因?yàn)槿绱耍盘?hào)密度可能非常高。

圖2︰信號(hào)路徑上阻抗TDR圖實(shí)例。

一般的FR4電路板材料是屬于阻抗一致的環(huán)境,但是分散式寄生阻抗對(duì)訊號(hào)質(zhì)量會(huì)產(chǎn)生負(fù)面的影響。影響最大的部份,是因大量工作在高于基本的資料速率的頻率分量產(chǎn)生的快速上下邊緣變換率,所引起的信號(hào)損耗和緩慢轉(zhuǎn)換時(shí)間。除此之外,在元件間(例如BNC連接器、積體電路、電路板不同層之間的過(guò)道孔,或者板子之間的連接器)的互相聯(lián)結(jié)可能導(dǎo)致與特征阻抗(Z0)的阻抗誤配,這也會(huì)影響到信號(hào)品質(zhì)(如圖2)。密集的底板連接器會(huì)為訊號(hào)路徑增加感性負(fù)載,而PCB的過(guò)道孔增加了信號(hào)路徑的容性負(fù)載。

在信號(hào)傳輸路徑上,任何存在阻抗改變的地方都可能出現(xiàn)信號(hào)反射。這些反射和寄生阻抗將導(dǎo)致信號(hào)幅度的損耗、環(huán)狀波、上升時(shí)間變長(zhǎng)和EMI等問(wèn)題。在本文的范例系統(tǒng)中,從EQ輸出到交叉點(diǎn)開(kāi)關(guān)的輸入之間FR4電路板長(zhǎng)度預(yù)計(jì)長(zhǎng)達(dá)31英寸,在這個(gè)路徑上H會(huì)出現(xiàn)幾個(gè)阻抗不連續(xù)的情況。如果沿著這個(gè)路徑的入射邊緣(incident edge)速度為175到200 ps/英寸,資料速率為1.485Gbps(半波長(zhǎng) = 343 ps),那么在任何所給予的時(shí)間都存在多達(dá)18個(gè)傳換邊緣。阻抗不匹配的入射邊緣產(chǎn)生的反射,將影響到信號(hào)路徑上出現(xiàn)的所有信號(hào)變換邊緣。從信號(hào)邊緣1到信號(hào)邊緣17的反射在到達(dá)信號(hào)路徑終端時(shí),將使第18個(gè)信號(hào)邊緣嚴(yán)重地失真。結(jié)果得到的眼形圖(圖3)顯示了幅度損耗、額外的抖動(dòng)以及上升/下降時(shí)間變化。

圖3︰經(jīng)過(guò)長(zhǎng)達(dá)31英吋的FR4電路板傳輸后,交叉點(diǎn)開(kāi)關(guān)輸入處的眼形圖。

提升信號(hào)傳輸品質(zhì)的方法

對(duì)于這種挑戰(zhàn)的一個(gè)解決方案是在子卡和底板之間使用高品質(zhì)的連接器,這將使連接器的不連續(xù)性最小。更好的過(guò)道孔設(shè)計(jì)將進(jìn)一步使TDR測(cè)量圖扁平化,如此一來(lái),將使得這個(gè)長(zhǎng)度的信號(hào)路徑的實(shí)際阻抗將與Z0非常接近。

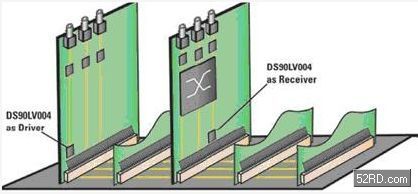

另外一種更具成本效益的解決方案,是使用一個(gè)簡(jiǎn)單的LVDS緩沖器來(lái)驅(qū)動(dòng)和接收底板上傳來(lái)的信號(hào)。它會(huì)將信號(hào)傳輸路徑再細(xì)分為很短的區(qū)段,以遮蔽阻抗誤配的問(wèn)題,并減少信號(hào)衰減。

在子卡的邊緣放置一個(gè)緩沖器以驅(qū)動(dòng)連接器和底板,再透過(guò)交換子卡上的另外一個(gè)緩沖器用來(lái)接收信號(hào)(圖4),并重新驅(qū)動(dòng)這些信號(hào)到交叉點(diǎn)開(kāi)關(guān)的輸入,以有效地隱藏兩個(gè)緩沖器之間的阻抗不連續(xù)(圖5)。正確的阻抗終結(jié)也能確保接收器吸收線路中的所有能量,使這些信號(hào)不會(huì)反射回來(lái)源端。

圖4︰利用緩沖器來(lái)克服阻抗的不連續(xù)問(wèn)題。

圖5︰采用緩沖器隔離底板連接后在交叉點(diǎn)輸入的信號(hào)眼形圖。

除此之外,緩沖器通常還能增強(qiáng)信號(hào)品質(zhì),改善原始信號(hào)。舉例而言,具有輸入均衡的緩沖器將在底板上傳輸信號(hào)之前消除媒質(zhì)損耗帶來(lái)的定量性抖動(dòng)(deterministic jitter)。輸出已預(yù)先加強(qiáng)信號(hào)的功能可增大信號(hào)幅度,使得在交叉點(diǎn)輸入或接收器處的眼形圖更為開(kāi)闊。在緩沖器I/O上,較高的ESD極限可保護(hù)子卡上的其他元件免受底板上其他位置發(fā)生的ESD意外事件而損壞。

LVDS緩沖器的功能

下面將以一種四通道1.5 Gbps LVDS的緩沖器/中繼器為例進(jìn)行說(shuō)明。該元件的高速資料路徑和直通管腳使元件內(nèi)部產(chǎn)生抖動(dòng)最小,并簡(jiǎn)化電路板設(shè)計(jì)。其可配置的預(yù)先加強(qiáng)信號(hào)功能,可以克服底板和電纜損耗帶來(lái)的ISI抖動(dòng)效應(yīng)。位差輸入和輸出在內(nèi)部用100Ω的電阻終結(jié)以改善性能,并減小電路板尺寸。增強(qiáng)信號(hào)強(qiáng)度的中繼器功能對(duì)于在高損耗的電纜和底板上長(zhǎng)距離傳輸信號(hào)來(lái)說(shuō),特別有用。

圖6︰四通道1.5 Gbps LVDS的緩沖器/中繼器典型應(yīng)用。

LVDS緩沖器具有帶電插接保護(hù)及15kV靜電釋放保護(hù)功能,可以加強(qiáng)底板及電纜的抗干擾能力,能保證現(xiàn)場(chǎng)可編程式陣列(FPGA)及專用積體電路(ASIC)傳送的信號(hào)的完整性。其應(yīng)用范圍包括電信、資料通信、工業(yè)系統(tǒng)、醫(yī)療設(shè)備、汽車電子系統(tǒng)及辦公室圖像系統(tǒng)等,典型應(yīng)用如圖6所示。LVDS緩沖器可以透過(guò)普通的底板或簡(jiǎn)單的電纜配置驅(qū)動(dòng)4個(gè)LVDS時(shí)鐘及/或資料通道。由于這款晶片的位差輸入電壓范圍較寬,因此很易接受LVDS、低電壓正射極耦合邏輯(LVPECL)或電流模式邏輯的輸入電平,而且輸出電平完全符合LVDS的規(guī)格要求。

做為范例的LVDS緩沖器晶片的資料傳輸率高達(dá)1.5Gbps,而且系統(tǒng)設(shè)計(jì)工程師更可利用這款晶片的可配置輸出預(yù)增強(qiáng)功能將輸出加以“加強(qiáng)驅(qū)動(dòng)力”,以便為容易出現(xiàn)信號(hào)損耗的互連線路提供補(bǔ)償。此外,對(duì)于必須盡量節(jié)省用電的應(yīng)用(如冗余應(yīng)用),若晶片的4條通道都暫停操作,系統(tǒng)可以透過(guò)低功耗模式將功耗降至最低。

總結(jié)

跨底板的高速介面需要在整個(gè)信號(hào)路徑上控制阻抗。采用簡(jiǎn)單型LVDS緩沖器來(lái)隔離阻抗不連續(xù)或者縮短互聯(lián)長(zhǎng)度可以降低系統(tǒng)成本;并且也因?yàn)椴恍枋褂酶叱杀镜母哳l連接器,進(jìn)一步提升介面的運(yùn)作效能。