在模擬集成電路中基準電壓源是一個非常重要的模塊,一個有效的基準電壓源應(yīng)在一定的范圍內(nèi)基本上與電源電壓變化、工藝參數(shù)變化及溫度無關(guān)。在高精度高速的數(shù)模轉(zhuǎn)換器中,一個精確的高電源抑制與溫度抑制的基準電壓的設(shè)計是至關(guān)重要的,其基準電壓源的精度直接影響到模數(shù)轉(zhuǎn)換器的精度。本文設(shè)計了一個小面積、高精度、高電源抑制與溫度抑制的基準電壓源以滿足10位40MSPS的模數(shù)轉(zhuǎn)換器的要求(根據(jù)10位ADC的要求,基準電壓源的溫度誤差應(yīng)小于1/210=1/1024=976×10-6)。

所設(shè)計的基準電壓源的工作電壓為5V,在本芯片中,采用了高精度的帶隙基準電壓源作為基本電壓源,另外根據(jù)FLASHAD的工作原理,設(shè)計了由同一個帶隙電壓源的基礎(chǔ)上產(chǎn)生兩組基準電壓,即RET(3.5V)和REB(1.5V),在ADC中使用時則利用了其差值作為其比較電壓,進一步確保了基準電壓源的精度。在芯片中,基準電壓源電路主要由兩部分構(gòu)成:一部分為帶隙基準電壓源產(chǎn)生電路;另一部分為由帶隙基準電壓源產(chǎn)生兩組基準電壓。

1 帶隙基準電壓源電路設(shè)計

帶隙基準電壓源(band-gap)是基準電壓模塊的核心部分,

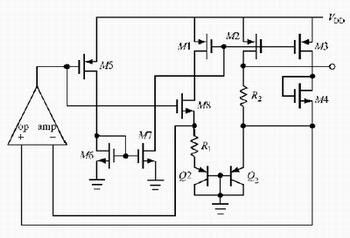

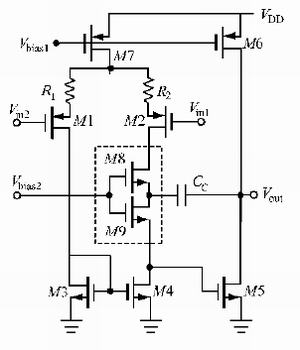

為了以最小面積、最低成本實現(xiàn)高性能的帶隙基準電壓源,所設(shè)計的電路如圖1所示。該電路按功能可分為帶隙電壓產(chǎn)生電路、啟動電路以及PTAT電路。

圖1 帶隙基準電壓源

啟動電路:啟動電路由M5、M6、M7以及運算放大器的偏置電路構(gòu)成(如圖1所示),當(dāng)電路加上電壓時,M5的柵電位為0V,則M5導(dǎo)通,通過電流鏡M6與M7給M1、M3、M5提供電流,電路開始工作。在電路正常工作后,運算放大器的輸出,提高了M5的柵電位,從而使M5截止,啟動電路停止工作,并且M5設(shè)計成一個倒比管以減小啟動電流。

帶隙電壓產(chǎn)生電路:主要由Q1、Q2、R1、R2、opamp及恒流源(M1、M2、)構(gòu)成,根據(jù)理想運算放大器的特性及pn結(jié)的I/V特性有

VBE1+I1R1=VBE2 (1)

VTln(I1/IS1)+I1R1=VTln[(I2+I4)/IS2] (2)

且因I2=n1I1,I4=n2I1;Q1、Q2的面積比設(shè)為n3,IS1/IS2=n3;故式(1)與(2)可簡化為

I1=VTln[(n1+n2)n3]/R1 (3)

VREF=I2R2+VBE2=n1VTln[(n1+n2)n3]R2/R1+VBE2 (4)

適當(dāng)選擇n1、n2、n3、R1、R2可設(shè)計出一個1.25V電壓的高精度基準電壓源。

PTAT電路:主要由M1、M2、M3、M4構(gòu)成的恒流源組成(如圖1所示),它們的電流I1、I2、I4與絕對溫度成正比,即為PTAT電流;通過利用PTAT電流與負溫度系數(shù)VBE構(gòu)成為其在某一溫度下其溫度系數(shù)為零的基準電壓源。

由以上分析可知:帶隙電壓源是利用理想運算放大器的兩輸入端虛短設(shè)計的,故運算放大器的設(shè)計要求很高,最重要的指標是運算放大器的增益,增益越高則運算放大器越接近理想、誤差越小。本文設(shè)計了一個面積小、增益高、輸入范圍大的新型CMOS運算放大器。

2 band-gap中運算放大器的設(shè)計

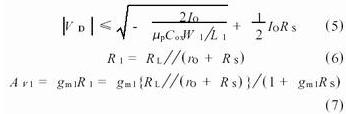

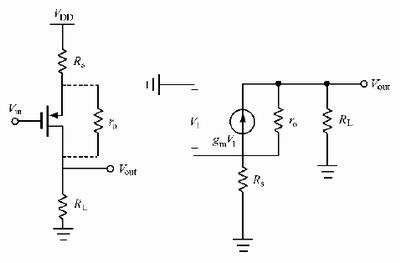

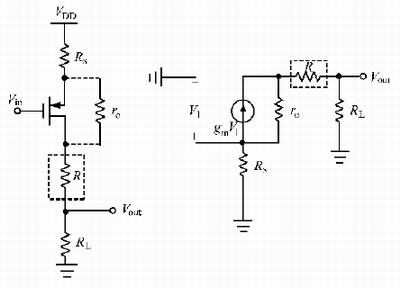

傳統(tǒng)的串聯(lián)反饋CMOS運算放大器的結(jié)構(gòu)如圖2所示。輸入級可利用圖3推導(dǎo)出

通過式(5)、式(7)可以看出其輸入范圍比傳統(tǒng)的不帶反饋的二級放大器大,而增益卻減小了。

即這種運算放大器的特點為大輸入范圍,但增益較小。

圖2 串聯(lián)反饋電阻運算放大器

圖3 串聯(lián)反饋電阻運算放大器等效電路圖

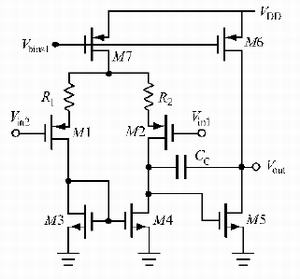

通過式(7)可知提高增益的一個有效辦法就是增大輸出電阻,但若直接串聯(lián)上電阻,由于電阻工藝誤差和寄生電容都比較大,會造成難以控制因素增多,而MOS管的工藝一致性比較好,為此提出了一種運算放大器的結(jié)構(gòu)(如圖4):主要是通過增加M8、M9來提高增益,從而以較小面積實現(xiàn)高增益運算放大器,即在第一級的輸出端增加了兩個MOS管M8、M9,這兩個MOS管的柵電壓相同,第一級的右半部分M2輸出通過M8的漏極輸入,M9的源極輸出,這兩個MOS管等效為一個電阻;同時M9起頻率補償作用,其近似等效電路如圖5所示,由此可得到

R1=RL//(rO+R+RS)AV1=gm1[RL//(rO+R+RS)]/(1+gm1RS) (8)

上式中,R為M8與M9的等效電阻,顯然式(8)中的輸出阻抗[RL//(rO+R+RS)]大于式(7)中的輸出阻抗RL//(rO+RS),即串聯(lián)M8、M9就相當(dāng)于提高了輸出電阻,進而提高了運算放大器的增益。

圖4 新型CMOS運算放大器

圖5 新型CMOS運算放大器等效電路

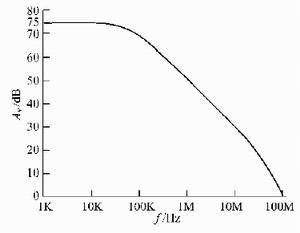

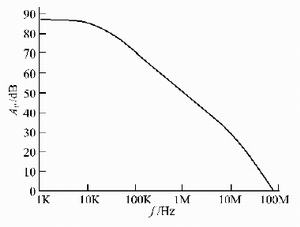

采用Chartered CMOS 0.35μm5V工藝庫對以上兩種運算放大器進行Hspice仿真,其仿真結(jié)果分別如圖6與圖7所示,由圖7可以看出串聯(lián)了M8、M9的新型CMOS運算放大器的增益約為88dB;而串聯(lián)反饋電阻運算放大器增益大約為75dB(如圖6所示)。

圖6 串聯(lián)反饋電阻運算放大器增益

圖7 新型CMOS運算放大器增益

3 基準電壓源RET、REB的設(shè)計

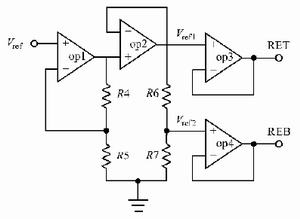

在帶隙基準電壓源產(chǎn)生的基礎(chǔ)上,為了進一步減小基準電壓源對ADC性能的影響,在ADC芯片中還設(shè)計了基于同一帶隙基準電壓源的兩組基準電壓源RET與REB(如圖8所示),利用其差值作為ADC的比較基準電壓,進一步減小帶隙電壓源絕對誤差的影響。

圖8 基準電壓源RET、REB產(chǎn)生電路原理框圖

該部分電路是運用運算放大器及其反饋的原理設(shè)計的,當(dāng)Vref(

帶隙電壓源產(chǎn)生的電壓)為1.25V時,調(diào)節(jié)R4與R5之比使運算放大器op1的輸出電壓為3.5V,通過運算放大器op2的跟隨作用,得到Vref1的電壓為3.5V,再通過調(diào)節(jié)電阻R6與R7的比值使Vref2的電壓為1.5V。為了提高它們的驅(qū)動能力,設(shè)計了運算放大器op3與op4構(gòu)成的跟隨器電路,得到了具有較高驅(qū)動能力的電壓分別為3.5V與1.5V的兩組基準電壓源RET與REB。

4 基準電壓源的仿真

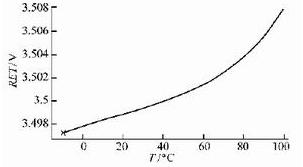

對所設(shè)計的帶隙電壓源進行Hspice仿真(采用Charted CMOS 0.35μm5V工藝),結(jié)果表明:采用新型的CMOS運算放大器后此帶隙電壓源的平均溫度系數(shù)小于10-4/°C,仿真結(jié)果如圖9所示(本芯片的溫度范圍為-10~150°C,由圖9可知:在此溫度范圍內(nèi)基準電壓變化小于110mV,即平均溫度系數(shù)為:110mV/110°C=10-4/°C);基準電壓源隨電源電壓變化的最大偏差為5mV,仿真波形如圖10所示(本芯片的電壓工作范圍:4.75~5.25V)。

圖9 基準電壓對溫度的抑制

圖10 基準電壓的電源抑制

5 測試

對所設(shè)計的ADC芯片進行了流片,圖11為用于測試的芯片及其接口,其中間部分就是所設(shè)計的芯片。

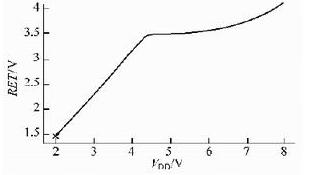

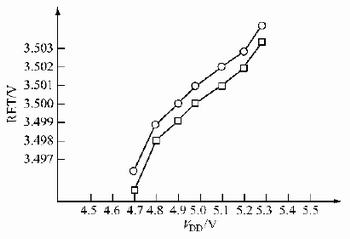

對芯片進行了測試:改變工作電壓,對基準電壓的輸出端RET進行測試,其結(jié)果如圖12所示,結(jié)果表明:在工作電壓范圍內(nèi),基準電壓源的最大偏差為5mV。同樣測得REB的值,計算同一VDD時RET-REB的值,可得其值恒定為2.0V,因此所設(shè)計的片上基準電壓源的電源抑制比高,而且RET-REB的差值恒定,為ADC中的比較器提供了穩(wěn)定的比較電壓,能很好地滿足10位40MSPS的要求。

圖11 所設(shè)計芯處片及接口

圖12 RET隨VDD變化的測試結(jié)果

6 結(jié)論

由于采用了新型的高增益CMOS運算放大器作為帶隙基準電壓源的運算放大器,從而大大提高了帶隙電壓源的精度,并且采用基準電壓的差值作為ADC中比較器的比較電壓,更進一步減小了誤差,經(jīng)測試所設(shè)計的基準電壓源能很好滿足ADC的要求。所設(shè)計的基準電壓源具有面積小、低溫度系數(shù)以及隨電源電壓變化的偏差小等特點。