數(shù)據(jù)采集" title="數(shù)據(jù)采集">數(shù)據(jù)采集在工業(yè)測試系統(tǒng)中是一個很重要的環(huán)節(jié),其精確性和可靠性是至關重要的。本文闡述的數(shù)據(jù)采集系統(tǒng)精度高達16位,能夠對8個外部模擬通道進行A/D采樣,最大模擬輸入信號范圍達到-15~+15V。該系統(tǒng)具有限幅保護功能,程序編寫簡便,能夠實現(xiàn)對遠端數(shù)據(jù)的采集和傳輸。

1 系統(tǒng)硬件設計

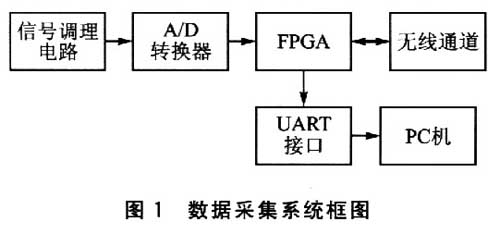

數(shù)據(jù)采集系統(tǒng)框圖如圖1所示。

圖中,A/D轉換器采用了TI公司的16位逐次逼近型ADS8344" title="ADS8344">ADS8344;FPGA" title="FPGA">FPGA主要用于控制ADC" title="ADC">ADC的啟動、停止和查詢ADC狀態(tài)等,同時對數(shù)據(jù)進行高速數(shù)據(jù)緩沖、異步數(shù)據(jù)編解碼、無線信道編解碼等數(shù)據(jù)處理。

1.1 主要芯片ADS8344

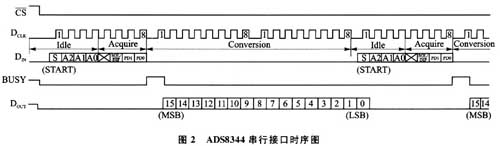

ADS8344是一款高性能、低功耗的ADC,采用2.7~5V單電源供電,最大采樣頻率為100 kHz,信噪比達84dB,自帶采樣/保持電路,包含8個單端模擬輸入通道(CH0~CH7),也可合成為4個差分輸入。參考電壓VRFF的范圍為500mV~VCC,相應的每個模擬通道的輸入為0V~VREF,DS8344是通過三線SPI接口與FPGA相互通信的,數(shù)據(jù)從DIN引腳輸入到8位只寫控制寄存器。當FPGA讀取完ADC上次轉換結果時,下一個轉換通道的控制字節(jié)就寫到了DIN引腳。一個完整的控制字節(jié)需要8個DCLK時鐘。寫完控制字節(jié)的同時,模/數(shù)轉換結束,模/數(shù)轉換狀態(tài)輸出引腳BUSY產(chǎn)生一下降沿,數(shù)據(jù)輸出有效,F(xiàn)PGA開始接收由DCUT輸出的轉換結果。16位串行數(shù)據(jù)需要16個DCLK時鐘,在接收串行數(shù)據(jù)的LSB位時,下一個通道的控制字開始輸入到A/D芯片。ADS8344完成一次完整的數(shù)據(jù)采樣保持、轉換和輸出共需要25個DCLK時鐘。ADS8344串行接口時序如圖2所示。

1.2 信號調理電路

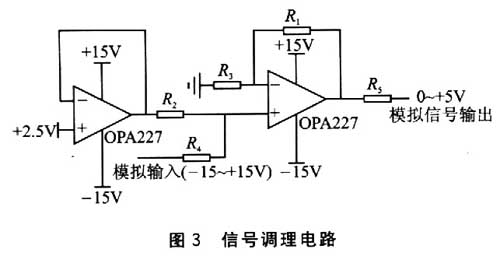

數(shù)據(jù)采集前端的調理電路如圖3所示。2個運放選用的是TI公司的精密儀表放大器OPA277。由于輸入模擬電壓信號為雙極性,范圍為一15~+5 V,而ADX8344模擬輸入通道為O V~VREF(本系統(tǒng)是+5 V),所以必須對輸入信號進行單極性轉換。

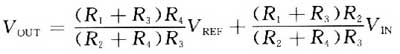

其傳遞函數(shù)為:

式中:VOUT為轉換后的單極性電壓信號;VREF由電壓基準源提供,在圖中是+2.5V;VIN為輸入的一15~+15 V電壓信號。當R3=6R1、R4=6R2時,傳遞函數(shù)可化簡為:

可見,傳遞函數(shù)是線性函數(shù)。只要正確選擇精確的電阻值,一15~+15 V電壓信號可線性轉換為O~+5V,從而保證了系統(tǒng)的精度。

1.3 無線通道

本系統(tǒng)是按用戶的要求設計開發(fā)的,其中,無線通道是由用戶提供的。本系統(tǒng)采用的無線通道是點對點傳輸,傳輸距離最遠達40 km,傳輸速率最高達11 Mbps,對標準異步串口數(shù)據(jù)是透明傳輸。A/D電路輸出的數(shù)據(jù)經(jīng)FPGA高速數(shù)據(jù)緩沖、異步數(shù)據(jù)編碼、無線信道編碼等數(shù)據(jù)處理后,送到無線通道進行無線傳輸。遠端的無線接收機接收到數(shù)據(jù)后送到FPGA進行無線信道解碼、異步數(shù)據(jù)解碼等處理,恢復A/D采樣數(shù)據(jù),然后或者送到D/A電路進行模擬量輸出,或者重新進行異步數(shù)據(jù)編碼送到PC機,由PC機對數(shù)據(jù)做進一步的分析處理。

2 軟件設計

本系統(tǒng)的軟件設計包括了FPGA硬件描述語言編程和PC機應用程序。

2.1 FPGA編程

FPGA編程使用VHDL語言,主要包括對ADS8344的數(shù)據(jù)讀寫、異步數(shù)據(jù)編解碼等。使用FPGA很容易實現(xiàn)SPI接口間的通信,對ADS8344的數(shù)據(jù)讀寫僅用兩個進程就可以實現(xiàn)。部分程序如下:

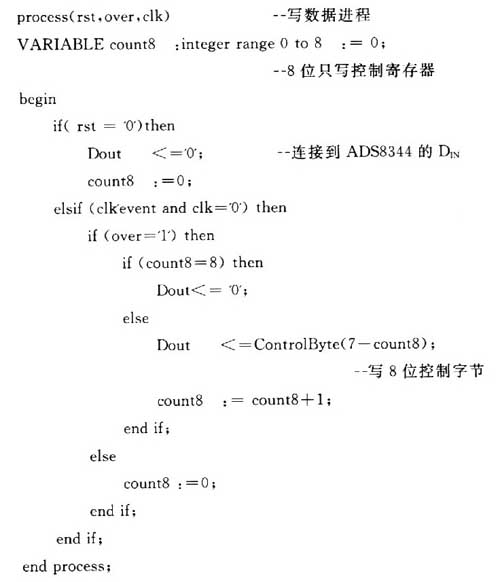

(1)寫數(shù)據(jù)進程

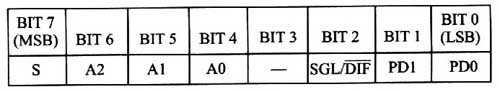

程序中的8位控制字節(jié)是在另一進程中根據(jù)用戶要求進行配置的。控制寄存器格式如下:

控制寄存器各位的功能說明如下:

- S——控制字節(jié)開始位。為高時,才表示輸入的字節(jié)有效。

- A2~AO——模擬輸入通道選擇位。

- SGL/DIF——模擬通道輸入方式選擇位。為高時,為單端輸入i為低時,為雙端差分輸入。

- PDl~DO——功率管理選擇位。

(2)讀數(shù)據(jù)進程

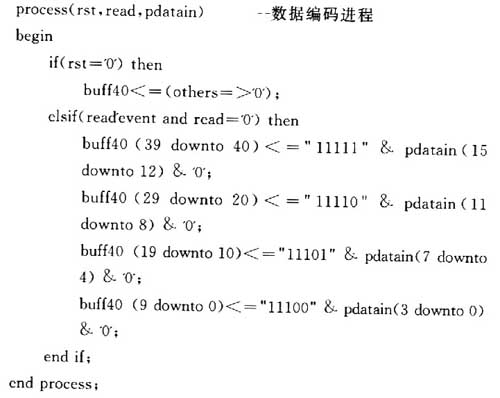

ADS8344是多通道A/D轉換芯片,所以數(shù)據(jù)要添加通道地址碼。FPGA讀取了16位數(shù)據(jù)后,進行高速數(shù)據(jù)緩沖處理,使用速率與低速異步串口速率匹配。由于讀取的數(shù)據(jù)是16位,而異步數(shù)據(jù)是10位(1位起始位,8位數(shù)據(jù)位,l位停止位),因此要對數(shù)據(jù)重新編碼。用FPGA實現(xiàn)異步數(shù)據(jù)格式非常簡單。下面是異步數(shù)據(jù)編碼的部分程序:

在數(shù)據(jù)編碼進程中,pdatam(15 downto 0)是A/D轉換出來的16位數(shù)據(jù),分為4個異步數(shù)據(jù)幀。每幀的低4位是數(shù)據(jù)位,高4位是編碼位,數(shù)據(jù)編碼格式如表l所列。

上位PC機以指定速率接收到如表l格式的4個異步數(shù)據(jù)幀后,去掉起始位、停止位,地址位和空閑位,按地址位順序重新排列數(shù)據(jù),就得到D15~D0的16位A/D量化數(shù)據(jù),PC機對數(shù)據(jù)可做進一步的處理。

2.2 PC機編程

PC機端的應用程序是在NI公司的LabView" title="LabView">LabView環(huán)境下開發(fā)的,主要用于對采集到的數(shù)據(jù)進行解封裝,顯示,控制整個數(shù)據(jù)采集系統(tǒng)的進行、停止,設置一些相應的參數(shù),以及進行最后的數(shù)據(jù)分析處理。

3 結論

該系統(tǒng)綜合運用了FPGA硬件描述語言改變電路結構、算法技術和無線點對點傳輸技術,將兩者相結合應用在遠程數(shù)據(jù)采集中。該系統(tǒng)用戶界面友好,操作簡便,精度、速度以及系統(tǒng)可靠性完全滿足要求。該系統(tǒng)應用于某研究所試驗中的飛艇與地面間的數(shù)據(jù)采集傳輸。實踐表明,該系統(tǒng)適合用在要求采集通道多、精度高,但速率要求不高的數(shù)據(jù)采集中。