ADC12C/DSxxx和ADC14C/DSxxx系列模數(shù)轉(zhuǎn)換器內(nèi)置高性能的采樣及保持放大器和高精度帶隙電壓參考電路,輸入帶寬高達1GHz,因此可以支持中頻采樣工作。此外,這系列芯片輸入方面有單及雙通道,而輸出方面有并行CMOS及串行LVDS可供選擇,更容易將FPGA或ASIC與模擬/數(shù)字轉(zhuǎn)換器連接一起。這系列芯片的各型號產(chǎn)品都引腳兼容,確保系統(tǒng)可以輕易由12位升級至14位,部分芯片更可在攝氏-40至+85℃的廣闊工業(yè)溫度范圍內(nèi)工作。單通道的型號采用32引腳的LLP封裝,尺寸5mm×5mm,而雙通道的型號則采用60引腳的LLP封裝,尺寸9mm×9mm。

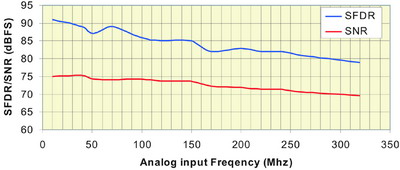

這系列模數(shù)轉(zhuǎn)換器若以1GHz以上的滿功率帶寬工作,則具有優(yōu)良的動態(tài)性能及線性度,功耗較低。這系列芯片若以高達300MHz的輸入頻率工作,其無雜散信號動態(tài)范圍(SFDR)可高達80dB。若采用3.0V的供電電壓,其功耗更低至320mW。即使輸入頻率超過300MHz,信噪比仍然高達70dB以上,讓系統(tǒng)設(shè)計工程師可以充分利用這個低噪聲的優(yōu)點,改善移動電話基站的接收能力。由于這系列芯片具有高帶寬及高采樣率的優(yōu)點,因此可以支持高中頻采樣。換言之,系統(tǒng)無需加設(shè)下變頻級,為系統(tǒng)節(jié)省可觀的成本,而且低功耗的特點也令系統(tǒng)更穩(wěn)定可靠。最后要強調(diào)的一點是,這系列芯片的帶寬很高,因此驅(qū)動器放大器不會受太多的限制,讓工程師可以精簡信號路徑的濾波系統(tǒng)。

若模擬輸入頻率較低,則以80MSPS的采樣率工作,其信噪比可達75dBFS, SFDR可達90dB,有效位數(shù)(ENOB)12位。若采樣率為105MSPS,信噪比可達74.5dBFS,SFDR可達90dB,ENOB可達11.9位。至于直流電方面的表現(xiàn),這系列模數(shù)轉(zhuǎn)換器的輸入偏移誤差±1mV,增益誤差±0.5%FS,微分非線性(DNL)誤差±0.5LSB,而積分非線性(INL)誤差±1.5LSB。由于這系列芯片采用先進電路設(shè)計,因此功耗可降至最低,實際功耗則取決于工作頻率。由于時鐘輸出引腳的上升邊緣位于輸出信號眼圖的中央位置,因此系統(tǒng)設(shè)計工程師可以利用時鐘輸出引腳捕捉并行的CMOS輸出數(shù)據(jù)。

高速傳輸?shù)慕鉀Q方案

ADC14C105雙通道模數(shù)轉(zhuǎn)換器可將兩條通道的不同參數(shù)互相對準,在對準過程中,芯片先將所取得的CMOS時鐘輸入傳送到芯片的核心,然后由一條緩沖通道再將時鐘輸入傳送到雙通道的時鐘輸入端,整個過程只需4個CMOS柵極。此外,芯片內(nèi)部區(qū)段分隔及供電路徑極為匹配,使通道間的孔徑抖動失配不超過30fs,而通道間的孔徑延遲失配則不超過50ps。此外,這款雙通道模數(shù)轉(zhuǎn)換器的通道間增益誤差失配不超過±0.2%FS,偏移失配不超過±1mV,而通道間的串音干擾則達到-95dB以上。

圖1 ADC14C105以105MSPS采樣率工作時,信噪比及無雜散信號動態(tài)范圍的頻率變化

LVDS是個電磁干擾極低的接口解決方案,最適用于高速的數(shù)據(jù)轉(zhuǎn)換器,已成為高速數(shù)據(jù)傳輸?shù)臉藴式涌凇4蠰VDS輸出模數(shù)轉(zhuǎn)換器設(shè)有單線及雙線兩種不同的數(shù)據(jù)傳輸模式,這種設(shè)計的目的是要降低LVDS數(shù)據(jù)傳輸率一半。單線模式適用于25MSPS至65MSPS的范圍,這個范圍內(nèi)的采樣率相當于350Mbps至910Mbps的數(shù)據(jù)傳輸率。雙線模式的數(shù)據(jù)傳輸率剛好是上述傳輸率的一半,因為LVDS輸出引腳的數(shù)目增加了一倍,因此,LVDS模數(shù)轉(zhuǎn)換器若采用雙線模式工作,轉(zhuǎn)換率便可提高到50MSPS至105MSPS的范圍內(nèi)。

LVDS接口設(shè)有偏移模式和字對準模式兩種不同的數(shù)據(jù)捕捉方式,以便解串器更易捕捉數(shù)據(jù),用戶則可按照個別應用的需要,選用適合的數(shù)據(jù)捕捉方式。正如圖2的數(shù)據(jù)所顯示,SD0/SD1兩條通道采用字對準的模式作為預設(shè)模式。若采用偏移模式,SD0通道的數(shù)據(jù)比SD1通道的數(shù)據(jù)延遲半個字。換言之,加設(shè)雙線模式這一選項可以精簡高速數(shù)據(jù)傳輸系統(tǒng)的設(shè)計流程,使工程師的設(shè)計工作變得更為容易。

圖2 雙線模式的定時時序圖

為了確保LVDS接口的調(diào)試功能,芯片可以支持不同的測試模式,包括預設(shè)測試模式和用戶自選測試模式。此外,這款雙通道芯片的許多功能都可加以設(shè)定,例如,可以將個別控制引腳連接電源或地線,然后進行設(shè)定,也可利用串行外圍設(shè)備接口(SPI)設(shè)定有關(guān)功能。

圖3顯示一幅典型的眼圖,圖中清楚顯示串行LVDS接口如何傳送數(shù)據(jù)。圖中的信號以80MSPS或1.12Gbps的速度傳送,信號抖動,例如隨機抖動、確定性抖動以及不同數(shù)據(jù)的不同抖動,都清楚顯示出來。以上抖動所產(chǎn)生的任何影響都必須計算在內(nèi),以便取得數(shù)據(jù)捕捉窗口。這款模數(shù)轉(zhuǎn)換器為數(shù)據(jù)捕捉提供90%的窗口容限。

圖3 ADC14DS105 芯片以1.12Gbps速度工作時的眼圖

IDCW=80MS/s×14bit=1.12Gbps=1bit/892.9 ps

ADCW=100×(1 - Tj/IDCW)=100×(1-85ps/892.9ps)=90.5%

公式中的IDCW是理想數(shù)據(jù)捕捉窗口,而ADCW是真實數(shù)據(jù)捕捉窗口。