引言

比較器廣泛應(yīng)用于從模擬信號到數(shù)字信號的轉(zhuǎn)換過程當(dāng)中。在模一數(shù)轉(zhuǎn)換過程中,經(jīng)過采樣的信號經(jīng)過比較器以決定模擬信號輸出的數(shù)字值。比較器可以比較一個(gè)模擬信號和另外一個(gè)模擬信號或參考信號的大小。比較器大都采用開環(huán)模式,這種開環(huán)結(jié)構(gòu)不必對比較器進(jìn)行補(bǔ)償,同時(shí),未進(jìn)行補(bǔ)償?shù)谋容^器可以獲得較大的帶寬和較高的頻率響應(yīng)。然而由于MOS器件的失配誤差,以及放大器的增益和速度之間的相互制約,使得在一定工藝條件下同時(shí)實(shí)現(xiàn)比較器的高速和高精度非常困難。

本文提出一種帶時(shí)鐘控制的可再生比較器,適用于在時(shí)間上離散的信號。此設(shè)計(jì)在傳統(tǒng)的前置預(yù)放和鎖存器級聯(lián)的理論基礎(chǔ)上,通過引入交叉耦合負(fù)載、復(fù)位和鉗位技術(shù),與文獻(xiàn)[3]相比,實(shí)現(xiàn)了更高的速度和相對較高的精度。

比較器結(jié)構(gòu)與設(shè)計(jì)

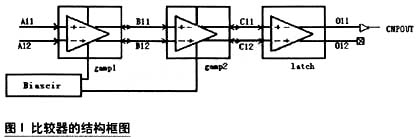

該比較器的結(jié)構(gòu)簡化如圖1所示。

它由兩級結(jié)構(gòu)相同的前置放大器和一級帶有復(fù)位再生的高速鎖存器組成,每一級中都帶有一個(gè)內(nèi)置正反饋的設(shè)計(jì)。前置放大器使輸入的變化足夠大,并且將其加載到鎖存器的輸入端,這樣獲得電路的最佳特性。

前置放大器的設(shè)計(jì)及優(yōu)化

傳統(tǒng)的前置放大器結(jié)構(gòu)如圖2所示,這種內(nèi)置正反饋比較器由一個(gè)差分輸入對,一個(gè)偽電流源和一對交叉耦臺負(fù)載組成,負(fù)載連接成差分的模式。M1和M2組成差分輸入對,M3、M33、M4、M44組成帶有正反饋的負(fù)載,以提高電路的增益,這個(gè)正反饋單元電路可以通過調(diào)整M3、M4和M33、M44管的寬長比(W/L)來形成弱正反饋或強(qiáng)正反饋。

前置放大器電路中的正反饋分析

正反饋是通過連接到M3和M4的源一漏極的并聯(lián)電壓反饋。其比較的工作過程為:差分輸入信號加到NMOS對管M1和M2的柵極,假設(shè)一端加正電壓信號,另一端則為負(fù)電壓信號;NMOS管M1中流過的電流Ids1開始增大,M2中電流Ids2開始減小,M3和M33柵極電位下降,M4和M44柵極電位上升,M3管中電流Ids3增大,M4管中電流Ids4減小;從而使M4和M44的柵極電位更高,M3和M33柵極電位更低,這個(gè)正反饋重復(fù)進(jìn)行直到Ids33隨其柵電壓減小而增大的速度與Ids4減小的速度相等,以及Ids44隨其柵電壓增大而減小的速度與Ids3增大的速度相等。

如果忽略M3與M4兩個(gè)交叉耦合的PMOS管負(fù)載的溝道長度調(diào)制效應(yīng)的影響,則交叉耦合負(fù)載的作用相當(dāng)于一個(gè)負(fù)電阻RX=-2/gm3(其中g(shù)m3=gm4)

考慮到M3、M4的溝道長度調(diào)制效應(yīng)的影響,則

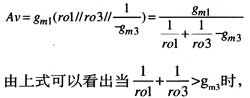

交叉耦合的正反饋負(fù)載的負(fù)電阻特性補(bǔ)償了一部分正的輸出阻抗,在一定程度上提高了差分輸出阻抗,提高了比較器的增益。所以,第一級前置正反饋放大器的增益為:

化簡得到直流電壓增益為:

在C1相同時(shí),時(shí)間常數(shù)越大,比較器的信號傳輸時(shí)間越長,其轉(zhuǎn)換速度就越低。但同時(shí),比較器的增益卻越大,因此導(dǎo)致高增益與高速度的矛盾。

設(shè)計(jì)優(yōu)化

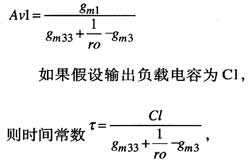

優(yōu)化后的前置內(nèi)置正反饋放大器電路結(jié)構(gòu)如圖3所示:

RS與![]() 兩個(gè)相反的時(shí)鐘信號用來控制比較器的復(fù)位,當(dāng)RS為高時(shí),比較器處于復(fù)位狀態(tài);RS為低時(shí),比較器開始進(jìn)行比較。這樣通過每次比較前的復(fù)位,可以進(jìn)一步提高比較器的翻轉(zhuǎn)速度。

兩個(gè)相反的時(shí)鐘信號用來控制比較器的復(fù)位,當(dāng)RS為高時(shí),比較器處于復(fù)位狀態(tài);RS為低時(shí),比較器開始進(jìn)行比較。這樣通過每次比較前的復(fù)位,可以進(jìn)一步提高比較器的翻轉(zhuǎn)速度。

為了獲得更高的工作速度,在兩個(gè)輸出端之間還有兩個(gè)鉗位二極管,用來控制兩個(gè)差分輸出端的電壓差。如果輸出電壓差值過大,則當(dāng)本級比較器的輸入發(fā)生翻轉(zhuǎn)時(shí),兩個(gè)輸出端會由于電壓差過大而造成輸出端翻轉(zhuǎn)的速度較慢,從而影響輸出結(jié)果和比較器的性能。所以這兩個(gè)MOS管可以起到鉗位的作用,即限制Vo1和Vo2電壓的擺幅,提高比較器的速度。在平衡狀態(tài)時(shí),通常∣Vo1-Vo2∣

第三級鎖存比較器設(shè)計(jì)

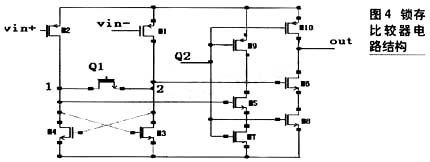

因前置放大器的增益與輸入電壓的乘積不足以達(dá)到輸出VOH的要求,所以把放大后的電壓再加到鎖存器上即可以得到所要求的電壓。第三級比較器的結(jié)構(gòu)采用可再生比較器,它也是使用正反饋來實(shí)現(xiàn)兩個(gè)信號的比較。可再生比較器又稱為鎖存比較器。比較器中兩相非交疊時(shí)鐘控制,確定不同的工作模式,從而實(shí)現(xiàn)比較器的復(fù)位與輸出。其電路的拓?fù)浣Y(jié)構(gòu)如圖4所示。其中兩相非交疊時(shí)鐘Q1和Q2的波形如圖5所示。

當(dāng)時(shí)鐘Q1為高電平時(shí),比較器處于復(fù)位狀態(tài)。這時(shí)節(jié)點(diǎn)1和2被置成等電位。接下來是再生階段,當(dāng)APX和APV都為低電平時(shí),通過交叉耦合的NMOS管M3和M4的正反饋進(jìn)行電壓再生,使節(jié)點(diǎn)1和2的電壓一個(gè)變高而另一個(gè)變低。最后是當(dāng)Q1為低、Q2為高時(shí),比較的結(jié)果通過M5、M6、M7、M8、M9的作用輸出,并保存此輸出至下一個(gè)復(fù)位狀態(tài)。

如圖4所示,本設(shè)計(jì)中的鎖存器使用的是NMOS管鎖存器。確定鎖存器工作時(shí)從開始狀態(tài)到最終狀態(tài)所需要的時(shí)間是很重要的。

當(dāng)M3和M4管相同時(shí):gm3=gm4=gm,C3=C4=C,R3=R4=R。

比較器要在規(guī)定的時(shí)間內(nèi)分辨出兩輸入信號之間微小的差值,先通過前置預(yù)放在T1時(shí)間把輸入電壓放大到Vin,將Vin加到鎖存器的輸入端,再經(jīng)過Tp時(shí)間達(dá)到要求的輸出電壓,所以總的響應(yīng)時(shí)間T1+Tp必須足夠小。而T1與前置放大器的3dB帶寬有關(guān),帶寬越高則放大信號的時(shí)延越小。此設(shè)計(jì)中兩級前置放大器的-3dB帶寬約為50MHz,所以T1較小;Tp與鎖存器的輸入有關(guān),想使Tp越短,其輸入Vin就應(yīng)該越大。前面的兩級前置放大器剛好解決這個(gè)問題,可以快速建立鎖存器的輸入,從而提高電路的工作速度。

另外,鎖存器較大的輸入失調(diào)電壓和輸入管寄生電容的KT/C噪聲也會直接影響到比較器的性能,因?yàn)檫@將會限制鎖存器的精度。同樣通過前兩級前置放大器的作用,鎖存器的輸入失調(diào)電壓等效到前置放大器的輸入端就會變得很小,因此可以較大程度上減小鎖存器的輸入失調(diào)電壓和輸入MOS管寄生電容的KT/C噪聲對比較器性能的影響。

設(shè)計(jì)結(jié)果分析與版圖

為了提高增益和工作速度,輸入對管的寬長比取值要稍大些。在設(shè)計(jì)中第一級和第二級前置放大器的偏置電流取值為52μA,其增益分別為14.75和11.8,帶寬為40MHz。前置放大器的大帶寬有利于減小其響應(yīng)時(shí)間,經(jīng)過兩級放大后,第三級鎖存器的輸入電壓的最小值為Vin_min×14.75×11.8,鎖存器較大的輸入相應(yīng)地減小了鎖存器的時(shí)間常數(shù),使鎖存器的輸出達(dá)到VOH-VOL的時(shí)間減小,實(shí)現(xiàn)了鎖存器的快速鎖存。經(jīng)過仿真,其性能參數(shù)如下:電源電壓3.3V,輸出VOH-VOL=3.3V,最小分辨率0.8mV,功耗<0.6mW,輸出動(dòng)態(tài)范圍3.3V。

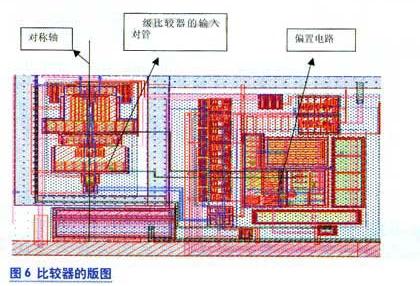

芯片采用了0.18μm的1P6MCMOS設(shè)計(jì)工藝,在實(shí)現(xiàn)高分辨率的同時(shí)也能獲得較高的速度,模擬結(jié)果表明,分辨率可以達(dá)到12bit。在版圖設(shè)計(jì)中,為了增強(qiáng)差分管的匹配性,管子和連線都采用全對稱的設(shè)計(jì)結(jié)構(gòu),版圖如圖6所示,面積為120μm×130μm。

結(jié)語

本設(shè)計(jì)介紹了一種ADC中常用的比較器,采用了兩級前置放大器和一級鎖存器組成的三級結(jié)構(gòu),而且每一級結(jié)構(gòu)內(nèi)部都帶有內(nèi)置正反饋。本設(shè)計(jì)采用了簡單的結(jié)構(gòu),以較小的芯片面積,實(shí)現(xiàn)了較高的速度和12bit的高精度,可以廣泛應(yīng)用于高速和高精度的ADC中。