1. 內(nèi)部框圖

AD公司新近推出的這種帶輔助DAC的雙路Σ-Δ模數(shù)轉(zhuǎn)換器,是一個(gè)完整的15位CMOS模數(shù)轉(zhuǎn)換器件。它采樣速率高,功耗低,且輸入端兼有信號(hào)處理功能,接收通道上的兩個(gè)帶數(shù)字濾波器的Σ-Δ型ADC合用一個(gè)能隙參考基準(zhǔn)。控制DAC可執(zhí)行AFC的功能,其它輔助功能可以從輔助串行端口獲得,以滿足器件多方面的性能要求。

圖1所示為AD7729的內(nèi)部框圖。AD7729主要有兩大部分組成:模數(shù)轉(zhuǎn)換器和輔助數(shù)模轉(zhuǎn)換器。模數(shù)轉(zhuǎn)換器由Σ-Δ型ADC、數(shù)字濾波器、偏移調(diào)整和主串行通訊接口組成;數(shù)模轉(zhuǎn)換器由10位輔助DAC、輸出緩沖器和輔助串行接口組成。

1.1 模數(shù)轉(zhuǎn)換器

模數(shù)轉(zhuǎn)換器部分有I和Q兩個(gè)通道,分別由一個(gè)開關(guān)電容濾波器和一個(gè)15位的ADC組成。片內(nèi)的數(shù)字濾波器對(duì)系統(tǒng)的性能起著關(guān)鍵作用,它們的幅頻和相頻響應(yīng)特性保證了相鄰?fù)ǖ篱g的相互干擾有極好的抑制性。

a. Σ-Δ型ADC

開關(guān)電容濾波器以13MHz的速率對(duì)接收的模擬量進(jìn)行采樣,其頻率響應(yīng)如2(a)所示。接收通道上的另一個(gè)數(shù)字濾波器的時(shí)鐘頻率為6.5MHz,其頻率響應(yīng)特性如圖2(b)所示。兩濾波器對(duì)應(yīng)的綜合頻率響應(yīng)如圖2(c)所示。AD7729的接收通道采用了Σ-Δ轉(zhuǎn)換技術(shù),在片內(nèi)實(shí)現(xiàn)系統(tǒng)濾波,從而保證了I和Q 端15位的高精度輸出。具體工作過程是用一個(gè)充電平衡的調(diào)制器以6.5MHz的速度對(duì)開關(guān)電容濾波器的輸出進(jìn)行采樣,并將其轉(zhuǎn)化成數(shù)字脈沖串。過高的過采樣速率能分散0?.25MHz的量化噪音,并使它在所關(guān)心的頻帶中減小。然后用一高階的調(diào)制器對(duì)噪音頻譜整形。再利用數(shù)字濾波器對(duì)帶外噪音進(jìn)行處理,并同時(shí)把數(shù)字脈沖轉(zhuǎn)化成并行的15位二進(jìn)制數(shù)據(jù)。

b. 數(shù)字濾波器

它有288個(gè)抽頭,建立時(shí)間為44.7μs。我們已介紹了它的兩個(gè)重要功能:系統(tǒng)的濾波功能和消除帶外量化噪音功能。由此可以看出,它有兩點(diǎn)優(yōu)于模擬濾波器:首先,由于它位于ADC之后,消除A/D轉(zhuǎn)化過程中產(chǎn)生的噪音;其次,它不僅消除了低通的振鈴,同時(shí)還保證了線性相位響應(yīng)。雖然這些功能都是模擬濾波器很難達(dá)到的,但模擬濾波器卻消除了A/D轉(zhuǎn)化前信號(hào)中所帶的噪音。由于噪音的波峰有使模擬調(diào)制解調(diào)器達(dá)到飽和的危險(xiǎn),AD7729專門為調(diào)制器和濾波器設(shè)置了一個(gè)超范圍裕度,允許有100mV的超范圍漂移。

1.2 數(shù)模轉(zhuǎn)換器

a.輔助控制功能

該功能是由輔助DAC來(lái)實(shí)現(xiàn)的。它由幾個(gè)高阻抗電流源組成,后接很輕的負(fù)載以保證它的直流精度。輔助DAC帶有輸出放大器,可以允許10kΩ的負(fù)載電阻。DAC的模擬輸出為2VREFCAP/32+(2VREFCAP-2VREFCAP/32)×DAC/1023 。其中:VREFCAP是參考電壓。DAC是所要輸出的數(shù)字信號(hào)。

b.參考電壓和串行端口

REFCAP是一個(gè)能隙參考基準(zhǔn),不僅噪音低,還可為ADC和輔助DAC提供溫度補(bǔ)償。參考電壓VREFCAP=1.3V。主串行接口(BSPORT)和輔助串行接口(ASPORT)都是DSP(數(shù)字信號(hào)處理器)兼容的串行端口。用戶可自由選擇寄存器與端口的連接方式,還可通過調(diào)整SCLK的頻率來(lái)減小功耗。

c. 讀/寫操作

經(jīng)串行口對(duì)寄存器進(jìn)行的讀和寫操作就是對(duì)16位字長(zhǎng)的數(shù)據(jù)即10個(gè)數(shù)據(jù)位和6個(gè)地址位(Rx例外)進(jìn)行轉(zhuǎn)換。必須對(duì)只讀寄存器給出一定的地址才能從中讀出對(duì)應(yīng)的的內(nèi)容,寫入和讀出的時(shí)間間隔大約為4個(gè)主時(shí)鐘周期。

2. 引腳

AD7729采用28引腳TSSOP和28腳SOIC兩種封裝形式。其引腳說明見表1所列。

3. 電路的調(diào)整

3.1 校準(zhǔn)

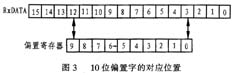

數(shù)字濾波器本身就是一種校準(zhǔn)方式。一般來(lái)說,數(shù)字低通濾波器的每個(gè)通道上都有一個(gè)偏置寄存器。模擬電路中直流偏置的值便存在里面。一般情況下,在數(shù)據(jù)進(jìn)入串行輸出引腳之前,濾波器就已將寄存器的偏置信息清除。因此可選用自校準(zhǔn)或用戶校準(zhǔn)來(lái)除去I和Q通道中的偏差。所不同的是自校準(zhǔn)只能消除內(nèi)部偏差,而用戶校準(zhǔn)則可以通過寫入偏置寄存器的信息來(lái)對(duì)外部偏差進(jìn)行校準(zhǔn)。偏置寄存器最多能容納162.5mV的直流偏置,超范圍的輸入將會(huì)導(dǎo)致錯(cuò)誤的輸出。然而,當(dāng)帶有超過100mV偏置的信號(hào)進(jìn)入時(shí),Σ-Δ調(diào)置器會(huì)自動(dòng)換檔。偏置寄存器中補(bǔ)碼的值與Rx的對(duì)應(yīng)關(guān)系如圖3所示。

AD7729有一個(gè)完整的自校準(zhǔn)程序:當(dāng)Rx被置位時(shí),模擬電路和數(shù)字電路的穩(wěn)定需要時(shí)間TSETTLE。只有當(dāng)主控制寄存器A(BCRA)的RxAUTOCAL位處于高電平時(shí),才開始進(jìn)行校準(zhǔn)。在內(nèi)部自校準(zhǔn)模式下,AD7729用短路差動(dòng)輸入來(lái)測(cè)量ADC中的偏移值;在外部自校準(zhǔn)模式下,AD7729維持輸入的正常連接允許系統(tǒng)偏置的存在。RxDELAY1和RxDDELAY2分別為兩個(gè)定時(shí)器的定時(shí)時(shí)間,當(dāng)RxDELAY2到時(shí)后,將會(huì)輸出15位的無(wú)效數(shù)據(jù)。

3.2 Rx的接收過程

當(dāng)Rx置位時(shí),串行端口的SDO腳將以270k字的速率輸出Rx的數(shù)據(jù)。AD7729的輸出結(jié)果為16位,即以二進(jìn)制補(bǔ)碼形式存在的數(shù)據(jù)位和一個(gè)志位(LSB),LSB用以區(qū)別I和Q。當(dāng)LSB=0時(shí),輸出為I,否則為Q。只要RxON處于高電平,串行時(shí)鐘的頻率就保持為13MHz,而與時(shí)鐘速率寄存器中的值無(wú)關(guān)。在SDO引腳自動(dòng)輸出Rx數(shù)據(jù)時(shí),會(huì)同時(shí)產(chǎn)生幀同步信號(hào),間隔為48個(gè)主時(shí)鐘周期。輔助串行端口ASPORT和主串行端口BSPORT均能輸出數(shù)據(jù),但用戶只能根據(jù)需要選擇其一,并且不能同時(shí)在兩個(gè)端口間進(jìn)行數(shù)據(jù)交換。

3.3 斷電

AD7729的每個(gè)部分都能被斷電。Rx模數(shù)轉(zhuǎn)換器和輔助數(shù)模轉(zhuǎn)換器可分別通過設(shè)定控制寄存器上的適當(dāng)位來(lái)斷電。當(dāng)AD7729的每個(gè)部分都上電時(shí),模擬電路和數(shù)字電路需要一個(gè)建立時(shí)間,同時(shí)參考電壓VREFCAP也需要一個(gè)上電時(shí)間。為減少上電所需時(shí)間,可將LP置1而使ADC和DAC處于斷電模式,而REFCAP引腳將保持上電模式,不需要上電和建立時(shí)間,從而使上電穩(wěn)定工作所需的時(shí)間減小。ADC和DAC可通過適當(dāng)?shù)目刂萍拇嫫鞣謩e斷電,當(dāng)包括參考基準(zhǔn)在內(nèi)的所有元件都處于斷電狀態(tài)時(shí),延遲64個(gè)時(shí)鐘周期后,主時(shí)鐘也停止工作。

3.4 復(fù)位

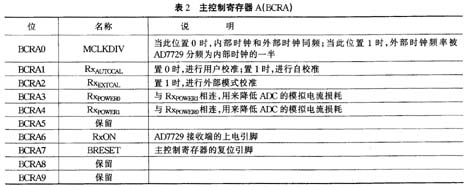

引腳RESETB能復(fù)位所有的控制寄存器, ASCLKRATE和BSCLKRATE的復(fù)位值為4,以保證ASCLK和BSCLK信號(hào)的頻率為MCLK的八分之一,其余控制寄存器則被復(fù)位為0。同時(shí)這些寄存器也能用主寄存器和輔助寄存器上的RESET位復(fù)位。所有的輔助寄存器通過給控制寄存器ACRB上的ARETSET位置高電平復(fù)位,而主寄存器則通給控制寄存器BCRB上的BRETSET位置高電平來(lái)復(fù)位,所需時(shí)間為4個(gè)主時(shí)鐘周期。復(fù)位后,ARESET和BRESET的復(fù)位值為0。寄存器 ARDADDR,BRDADDR,ASCLKRATE,BSCLKRATE只能用復(fù)位引腳RESETB復(fù)位,所需時(shí)間為8個(gè)主時(shí)鐘周期。控制寄存器的功能見表2所列。

4.接口舉例

AD7729還為用戶提供了與DSP兼容的標(biāo)準(zhǔn)串行端口,由ADC的串行時(shí)鐘控制串行數(shù)據(jù)和I/O DSP信息。

圖4為AD7729與ADI公司的ADSP-21xx的接口原理圖。對(duì)于ADSP-21xx,串行端口的控制寄存器必須設(shè)置為TFSR=RFSR=1 (保證每個(gè)轉(zhuǎn)換器的幀同步),SLEN=15(16位字長(zhǎng)),TFSW=RFSW=0(正常幀同步),INVIFS=INVRFS=0(高有效的幀同步信號(hào)),IRFS=0(外部RFS),ITFS=1(內(nèi)部TFS)和ISCLK=0(外部串行時(shí)鐘)。

AD7729是一種帶輔助DAC的雙路Σ-Δ模數(shù)轉(zhuǎn)換器,它不僅具有噪音低,精度高,工作速度快等優(yōu)點(diǎn),并且可與多種DSP接口,通用性很強(qiáng)。所以該器件是新一代理想的數(shù)據(jù)采集和模數(shù)轉(zhuǎn)換器件,可廣泛應(yīng)用于通訊、多媒體和高性能儀器中。