摘要: 采用TI公司的TMS320DM642型數(shù)字媒體數(shù)字信號處理器(DSP)設計多路音/視頻采集處理系統(tǒng),實現(xiàn)實時處理4路模擬視頻和音頻輸入、1路模擬/數(shù)字視頻和l路模擬音頻信號輸出的功能,該系統(tǒng)可適應PAL/NTSC標準復合視頻CVBS或分量視頻Y/C格式的模擬信號和標準麥克風或立體聲音頻模擬輸入,具有PAL/NTSC標準S端子或數(shù)字RCB模擬/數(shù)字信號輸出和標準立體聲音頻模擬輸出。并給出軟/硬件設計原理和電路。

關鍵詞:TMS320DM642;圖像采集處理;PAL/NTSC制式;數(shù)字信號處理器

l 引言

當前,在數(shù)字圖像處理中,由于數(shù)據(jù)量大、算法難度高,因此實時性成為技術難點之一。如果采用專用電路實現(xiàn),雖然實時性得到保證,但系統(tǒng)的靈活度大大降低。因此,尋求一種高速通用數(shù)字信號處理系統(tǒng)成為當務之急。

II公司推出的TMS320DM642(以下簡稱DM642)型數(shù)字信號處理器可實時處理4路模擬視頻和音頻輸入、l路模擬/數(shù)字視頻和1路模擬音頻信號輸出,適應PAL/NTSC標準復合視頻CVBS或分量視頻Y/C格式的模擬信號輸入,可適應PAL/NTSC標準S端子或數(shù)字RGB模擬/數(shù)字信號輸出,可適應標準麥克風或立體聲音頻模擬輸入及標準立體聲音頻模擬輸出,具有對多路采集數(shù)據(jù)進行實時處理和分析的功能,可實現(xiàn)數(shù)據(jù)和圖像疊加顯示。

2 DM642簡介

DM642型數(shù)字信號處理器可采用500 MHz或600 MHz的工作頻率,每秒最多可完成4.8 G次操作,具備在線編程功能,帶有的豐富外圍接口可以與多種存儲器相連,可以直接與網(wǎng)絡連接,是高速圖像處理的優(yōu)選器件。

DM642的CPU采用第二代VelociTI.2內核結構,含有雙數(shù)據(jù)通路、8個運算單元,每周期可執(zhí)行8條32-bit指令,支持4個16-bit和8個8-bit連乘加MAC指令,有64個寄存器,取數(shù)/存數(shù)的數(shù)據(jù)通道為64-bit。

DM642采用帶2級存儲器的完全存儲器分層體系結構,2級存儲器中的Cache控制器可以自動完成分層存儲器體系結構的管理和調度,外部存儲器訪問和片上外設的訪問通過EDMA完成。

DM642有3個視頻輸入輸出口和多路音頻信號的輸入輸出串口。外部存儲器接口EMIF提供了64-bit寬度的外總線數(shù)據(jù)接口,支持與各種器件的無膠合接口。DM642還具有主機并行接口、外圍設備互聯(lián)口、多通道緩存串口和通用I/O端口。

3 系統(tǒng)功能與硬件電路設計

3.1 系統(tǒng)總體結構

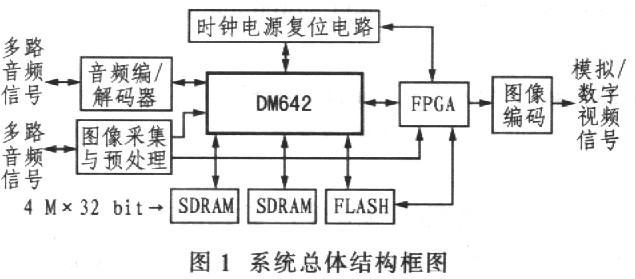

系統(tǒng)總體結構如圖1所示,圖像采集和預處理單元主要完成圖像信號的輸入,具有多路信號復用功能,對輸入的模擬視頻信號進行數(shù)字化及格式的轉變。FPGA控制系統(tǒng)的邏輯和圖像數(shù)據(jù)的流向,并且可對DM642輸出的圖像數(shù)據(jù)進行加工,進而輸出到圖像編碼單元。圖像處理單元采用DM642進行高速數(shù)據(jù)處理和分析。圖像編碼單元對圖像數(shù)據(jù)進行編碼,形成標準的模擬視頻信號,可以直接輸出到顯示設備上。

對于4路視頻和4路音頻信號,CPU在1個時刻只能處理1路數(shù)據(jù),DM642片外位于EMIF的CEO地址空間擴展了2個4 Mx32 bit的SDRAM,可分別存放圖像采集數(shù)據(jù)和圖像處理數(shù)據(jù),以提高數(shù)據(jù)采集和存儲速度。

3.2 視頻口接口設計

DM642有3個視頻口,每個都可以配置為上下2個通道,但2個通道必須同時為視頻輸入口或輸出口。結合實際應用,DM642帶了4路模擬視頻輸入(cif格式,分辨率為352×288)和1路模擬視頻輸出。

VPO A通道配置為8-bit BT.656視頻輸入或輸出口,接第一通道視頻輸入或視頻輸出。VPl A通道配置為8-bit BT.656視頻輸入口,接第二通道視頻輸入。VP2 A和B通道配置為2個8-bit BT.656視頻輸入口,接第三和第四通道視頻輸入。VP0和VPI的B通道配置為MCASP,接4個音頻Codec。

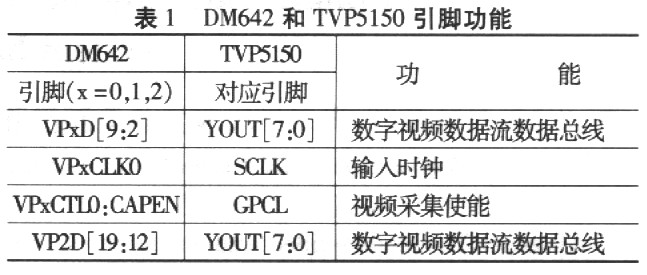

TVP5150型視頻編碼器支持PAL/NTSC、CVBS或Y/C模擬視頻輸入,8-bit BT.656數(shù)字視頻數(shù)據(jù)流輸出。SAA7105型視頻解碼器支持8-bit BT.656數(shù)字視頻數(shù)據(jù)流輸入,PAL/NTSC CVBS或Y/C模擬視頻輸出。通過DM642的I2C總線對視頻編/解碼器的內部寄存器進行編程,實現(xiàn)不同的輸入輸出。DM642和TVP5150的對應引腳功能見表1。

視頻編解碼器的參數(shù)通過I2C總線配置,由于TVP5150的I2C從地址只有2種選擇,因此需要用CBT3257型2選l轉換開關來切換。

作為視頻輸入口時,視頻數(shù)據(jù)的行/場同步又包含BT.656數(shù)字視頻數(shù)據(jù)流中的EAV和SAV時基信號控制,視頻口只需視頻采樣時鐘和采樣使能信號(控制采樣起始),TVP5150用系統(tǒng)時鐘SCLK提供采樣時鐘,用可編程引腳GPCL提供采樣使能。作為視頻輸出口時,視頻口要為SAA7105提供時鐘和行/場同步信號。

在視頻輸出電路中,J1、J2、J3可配置成RGB輸出信號,J2、J3可連接S端子,J1、J2、J3、J4、J5可直接輸出到電腦的顯示器上。具體接口電路如圖2和圖3所示。DM642與SAA7105的對應引腳功能見表2所列。

3.3 多通道音頻串口的接口設計

筆者采用了4路模擬音頻輸入和1路模擬音頻輸出,采用TLV320AIC23B型音頻編/解碼器,它支持麥克風/立體聲模擬輸入/輸出和數(shù)字音頻數(shù)據(jù)流輸出/輸入。

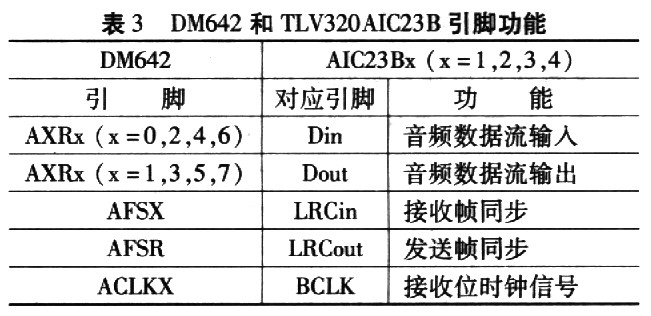

PLLl708型可編程視頻/音頻同步數(shù)字鎖相環(huán)給McASP和TLV320AIC23B提供時鐘信號,SCK02端口接McASP的AHCLKX,SCK03端口接TLV320AIC23B的主時鐘MCLK。PLLl708的時鐘輸入為27 MHz。DM642與TLV320AIC23B的對應引腳功能見表3。

AIC23B數(shù)據(jù)口配置為從,McASP的8個收/發(fā)引腳配置為4收/4發(fā),分別接4個編解碼器的Dout/Din。McASP的接收幀同步配置為輸出,同時給4個編解碼器的LRCout。McASP的發(fā)送幀同步配置為輸出,同時給4個編解碼器的LRCin。McASP的發(fā)送位時鐘ACLKX配置為輸出(由AHCLKX分頻),同時給4個編解碼器的BCLK。AIC23B的控制口配置為I2C,由CBT3257型2選1開關來切換。具體電路如圖4所示。

另外,給DM642供電時應注意CPU的上電次序:CHU內核應先于I/O上電,后于I/O掉電,CPU內核與I/0應盡可能同時供電,二者的時差不能太大(<1 s),否則會影響器件的壽命或損壞器件。用可編程時鐘電路可很好地解決整個電路的時鐘問題。

4 系統(tǒng)軟件設計

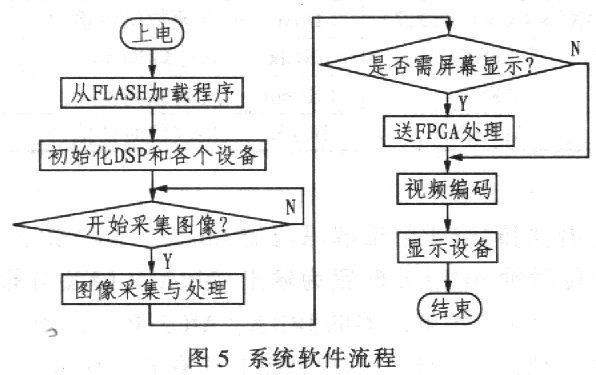

系統(tǒng)軟件包括系統(tǒng)初始化設置、圖像處理算法和屏幕疊加程序,具體軟件流程如圖5所示。

4.1 系統(tǒng)初始化設置程序

對整個硬件系統(tǒng)進行初始化,其中包括DM642的上電初始化、DM642的寄存器和系統(tǒng)配置引腳的設置、利用I2C總線對TVP5150和SAA7105進行寄存器設置。

DM642的引導模式為從EMIFA引導,把引腳AEA[22:21]設置為ll,其他配置引腳的初始化設置為默認值。外圍配置寄存器(PERCFG)用于對控制視頻口、多通道緩沖串口、多通道音頻串口進行配置,初始化為0x0000 0079h。設備狀態(tài)寄存器(DEVS-TAT)用于控制電路各個外圍設備的狀態(tài):EMAC、HPI、PCI、CPU時鐘頻率選擇模式、電路引導模式、EMIFA輸入時鐘的選擇,初始化為0x0000 005Ch。

4.2 圖像處理程序

對采集的圖像數(shù)據(jù)進行處理和分析,對視頻流進行格式轉換,可以是復合視頻或分量視頻,也可以壓縮存儲以便于此后的瀏覽。

4.3 屏幕疊加程序

把FPGA內部FIFO中的數(shù)據(jù)和視頻口輸出的數(shù)據(jù)混和完成屏幕顯示的功能。屏幕疊加有幾種方式,背景為透明的、半透明的、不透明的,疊加的位置也可任意設置,只需修改疊加圖像的起始點坐標,把相應的圖像信息加到對應的視頻圖像隊列中。

4.4 視/音頻信號采集存儲與圖像數(shù)據(jù)讀取程序

對于4路視頻信號和4路音頻信號,CPU在1個時刻只能處理1路數(shù)據(jù),因此在DM642片外擴展了2個4Mx32bit的SDRAM,在系統(tǒng)工作的任一時刻,一個用于圖像的采集,采集部分向該存儲區(qū)寫圖像數(shù)據(jù),另一個用于外部對圖像數(shù)據(jù)的讀取,DSP可以讀取該存儲區(qū)中的圖像數(shù)據(jù)。雙SDRAM結構的重要特點是DSP對存儲區(qū)的數(shù)據(jù)操作是來回切換的。當A/D轉換數(shù)據(jù)寫滿SDRAM-l時,F(xiàn)PGA會向DSP發(fā)出中斷信號,此時,在DSP讀取SDRAM-l中數(shù)據(jù)的同時,A/D轉換數(shù)據(jù)寫入SDRAM-2,當SDRAM-2中的數(shù)據(jù)寫滿時,F(xiàn)PGA向DSP發(fā)出中斷信號,此時DSP讀取SDRAM-2中的數(shù)據(jù),同時,A/D轉換數(shù)據(jù)寫入SDRAM-l,如此交替,實現(xiàn)數(shù)據(jù)的寫入與讀取同時進行。由于DSP讀取SDRAM中數(shù)據(jù)的速度遠遠大于A/D轉換寫入數(shù)據(jù)的速度,因而允許采集與外部訪問同時進行,采用2個存儲區(qū)操作的乒乓式切換滿足數(shù)據(jù)實時交換的要求。

由于DSP對存儲區(qū)的數(shù)據(jù)操作是來回切換的,因此需要采用中斷來實現(xiàn)取數(shù)。具體實現(xiàn)是在DSP內部設置中斷,這里選用INT6作為中斷觸發(fā)引腳。當外部中斷信號到來時,則相應中斷服務程序執(zhí)行中斷響應。

5 結束語

本系統(tǒng)能夠同時處理4路CIF格式的數(shù)字視頻,并且可以動態(tài)切換,總采樣速率可達100幀/秒,每路速率為25幀/秒,可以完全保證圖像實時采集。

對圖像的疊加有多種方法,疊加的位置也可通過修改疊加圖像的起始點坐標來進行任意設置。DM642還具有網(wǎng)絡接口,可以對輸出的視頻信號進行壓縮并由網(wǎng)絡實時傳輸。

基于DM642的圖像采集處理系統(tǒng)能廣泛應用于機頂盒、IP可視電話、網(wǎng)絡視頻會議等領域。