脈寬調(diào)制是一種調(diào)制或改變某個(gè)方波的簡單方法。方波占空比基本形式是隨輸入信號(hào)變化的。占空比是指方波的高電平時(shí)間和低電平時(shí)間之比。一個(gè)50%占空比的波形會(huì)具有50%的高電平時(shí)間和50%的低電平時(shí)間,而一個(gè)10%占空比的波形則具有10%的高電平時(shí)間和90%的低電平時(shí)間。PWM有許多應(yīng)用,其中包括電動(dòng)機(jī)控制、伺服控制、調(diào)光、開關(guān)電源,甚至某些音頻放大器。在諸如MEMS(微機(jī)電系統(tǒng))鏡面?zhèn)鲃?dòng)器控制等應(yīng)用系統(tǒng)中,有一個(gè)反饋系統(tǒng)必須對PWM進(jìn)行調(diào)節(jié)。有個(gè)電路監(jiān)測并控制PWM輸出信號(hào),然后根據(jù)應(yīng)用系統(tǒng)要求改變占空比。輸出頻率對傳動(dòng)器進(jìn)行調(diào)節(jié),而占空比則設(shè)定傳動(dòng)器的速度。反饋回路控制閾值電平。本“設(shè)計(jì)實(shí)例”描述帶反饋控制的高頻率高分辨率PWM。首先,探討一下PWM理論也許是有益的。

DDS電路可與一個(gè)比較器和一個(gè)帶內(nèi)部DAC和ADC的微控制器組合在一起" border="0" hspace="0" src="http://files.chinaaet.com/images/20100811/5fcbe2a4-f72a-46ab-af75-9ba4e94e255e.jpg" style="WIDTH: 450px; HEIGHT: 258px" />

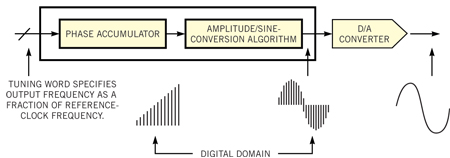

圖1 一個(gè)DDS電路可與一個(gè)比較器和一個(gè)帶內(nèi)部DAC和ADC的微控制器組合在一起,以便產(chǎn)生高分辨率的PWM輸出信號(hào)。

幾種可供選用的體系結(jié)構(gòu)

傳統(tǒng)的PWM用兩個(gè)運(yùn)算放大器來產(chǎn)生鋸齒波形,用一個(gè)電位器來產(chǎn)生直流基準(zhǔn)電壓,再用一個(gè)比較器來產(chǎn)生PWM輸出信號(hào)。這類設(shè)計(jì)的優(yōu)點(diǎn)是切實(shí)可行而又成本低廉。遺憾的是,

如不改變元件值就無法方便地對頻率進(jìn)行編程,而且頻率微調(diào)也非常困難。這種方法的另一個(gè)問題是難以精確控制占空比。你可以使用數(shù)字式電位器來替代機(jī)械式電位器,但這樣做會(huì)加大成本。產(chǎn)生PWM波形的第二種辦法是采用ADμC824 MicroConverter(微轉(zhuǎn)換器)。它除了提供兩個(gè)PWM信號(hào)輸出以外,還集成了幾個(gè)ADC、幾個(gè)DAC、一個(gè)與8052兼容的微控制器以及閃存。你可以配置出分辨率高達(dá)16位的PWM。不過,已編程的頻率會(huì)影響PWM的分辨率。PWM的頻率和分辨率如下:FPWM=16.777 MHz/N,式中N是以位表示的分辨率。

一個(gè)內(nèi)部PLL可根據(jù)32千赫晶振推導(dǎo)出16.77MHz基準(zhǔn)時(shí)鐘。該基準(zhǔn)時(shí)鐘對PWM的輸出信號(hào)進(jìn)行采樣。如前所述,N是PWM的分辨率,即位的多少。要達(dá)到16位的分辨率,PWM的最大頻率是266Hz。頻率為200kHz時(shí),分辨率會(huì)降到大約6位。因此,ADμC832對于低頻高分辨率系統(tǒng)來說是一種理想的低成本方法,但對于高頻高分辨率系統(tǒng)來說并非如此。

DDS的實(shí)現(xiàn)

要求實(shí)時(shí)高分辨率頻率調(diào)節(jié)和脈寬調(diào)制調(diào)節(jié)的系統(tǒng),可以采用直接數(shù)字合成器(DDS)在大帶寬范圍內(nèi)提供具有高頻率分辨率的高精度鋸齒波形。于是,你就可以在開環(huán)或閉環(huán)系統(tǒng)中將該信號(hào)作為比較器的輸入信號(hào)。圖1示出了一種產(chǎn)生具有可編程占空比的可編程方波的簡便方法。AD9833型DDS把一個(gè)可編程三角形波送入AD8611比較器的一個(gè)輸入端,并控制輸出波形的頻率。傳動(dòng)器的反饋回路控制比較器的閾值電平。AD8611是一個(gè)具有鎖存功能和互補(bǔ)輸出的4ns比較器。來自DDS的輸入信號(hào)直接送到比較器的反相輸入端。輸出信號(hào)通過R1和R2反饋到非反相輸入端。R1對R1+R2之比決定滯后窗的寬度,而VDAC設(shè)定滯后窗的中心,即平均開關(guān)電壓。輸出端在輸入電壓大于VHI時(shí)就轉(zhuǎn)變?yōu)榈碗娖剑⑶乙捷斎腚妷旱陀赩LO時(shí)才再次轉(zhuǎn)變?yōu)楦唠娖剑缦率剿荆篤HI=(V+-1.5V-VDAC)(R1/(R1+R2))+VDAC和VLO=VDAC(R2/(R1+R2)),式中 V+ 是加到比較器的正電源電壓,VDAC 是DAC設(shè)定的電平。AD8611能接收峰—峰電平為400mV的100兆赫信號(hào),也能接收幾十毫伏的輸入信號(hào)。AD9833可利用DDS體系結(jié)構(gòu)產(chǎn)生正弦波和三角波輸出信號(hào)。AD9833在一塊芯片內(nèi)含一個(gè)采用28位相位累加器的數(shù)值控制的振蕩器、一個(gè)正弦ROM以及一個(gè)10位數(shù)/模轉(zhuǎn)換器(圖2)。

圖2 一個(gè)DDS電路可在一塊芯片上包含一個(gè)采用28位相位累加器的數(shù)控晶振、一個(gè)正弦ROM以及一個(gè)10位數(shù)模轉(zhuǎn)換器。

你一般根據(jù)其振幅公式來考慮正弦波:a(t)=sin(vt)。但是,這些波形都是非線性的,而且難以產(chǎn)生。另一方面,角信息本質(zhì)上又是線性的。這就是說,相位角在每一時(shí)間單位內(nèi)轉(zhuǎn)過某一固定角度。只要知道一個(gè)正弦波的相位是線性的,又已知基準(zhǔn)間隔(時(shí)鐘周期),你就可以確定該周期內(nèi)的相位旋轉(zhuǎn):

相位=ωdt;

ω=Δ相位/dt;

f=(Δ相位×fMCLK)/2π,

式中dt是主時(shí)鐘頻率fMCLK的倒數(shù)。只要知道相位和主時(shí)鐘頻率,便可以利用這一公式產(chǎn)生輸出頻率。相位累加器提供28位的線性相位。正弦ROM以數(shù)字格式存儲(chǔ)輸出正弦波的振幅系數(shù)。DAC把正弦波轉(zhuǎn)換成模擬域。如果你旁路正弦ROM,則AD9833就會(huì)產(chǎn)生三角波,而不是產(chǎn)生正弦波。你可用寫入頻率寄存器的方法給該器件編程。于是,從該器件輸出的模擬信號(hào)是fOUT=(fMCLK/228)×(頻率-寄存器字)。

DDS輸出信號(hào)具有28位分辨 率,因此有效頻率步長有可能達(dá)到0.1Hz數(shù)量級(jí),而頻率最高可達(dá)大約10MHz。兩個(gè)相位寄存器具有12位相位分辨率。這些寄存器可使信號(hào)移相,移相值為PSHIFT=(2π/4096)×(相位-寄存器字)。一個(gè)25MHz的晶振為DDS提供基準(zhǔn)主時(shí)鐘。DDS的輸出級(jí)是一個(gè)擺幅為0.7VP-P的電壓輸出DAC,其負(fù)載是一只200Ω內(nèi)部電阻器。增加負(fù)載電阻RL會(huì)降低輸出電壓的峰—峰值,從而可以把DDS的峰—峰輸出調(diào)到比較器的輸入范圍內(nèi)。DDS的輸出端通常有一個(gè)濾波級(jí)。濾波級(jí)的用途是濾除基準(zhǔn)時(shí)鐘頻率、像頻和更高頻率的饋通信號(hào),并限制所考慮的信號(hào)的帶寬。

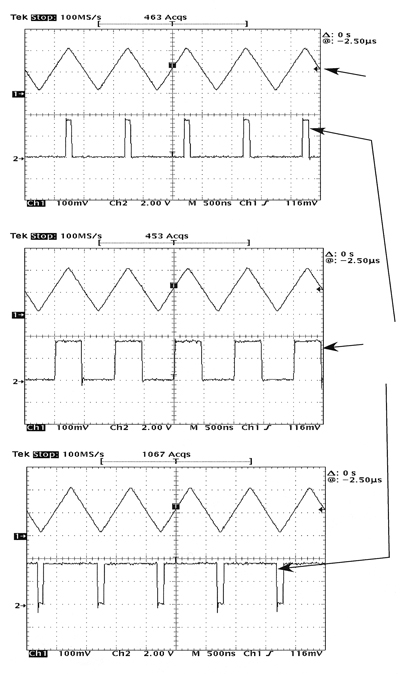

圖3示出了圖1中AD8611比較器的典型輸出曲線圖。DDS的輸入信號(hào)是一個(gè)調(diào)到1MHz的三角波。每個(gè)曲線圖都示出了各種不同閾值電壓的PWM輸出。在圖1的閉環(huán)電路中,你可以把PWM的輸出調(diào)到12位精確度。并可使用許多種脈寬調(diào)制方法;所用方法取決于應(yīng)用系統(tǒng)。對于低分辨率應(yīng)用系統(tǒng)來說,采用運(yùn)算放大器和電位器的傳統(tǒng)方法是可以接受的,也很經(jīng)濟(jì)實(shí)惠。對于低頻高分辨率應(yīng)用系統(tǒng)來說,ADμC832則是一種免費(fèi)增加功能的單芯片方法。對于要求頻率微諧的高分辨率

高頻應(yīng)用系統(tǒng)來說,你可以將一個(gè)DDS和一個(gè)比較器組合在一起,產(chǎn)生精密的高頻PWM波形。