近日,YouTube博主@TechTechPotato在視頻中,深入分享并解讀了IMEC(比利時(shí)微電子研究中心)發(fā)布的半導(dǎo)體工藝路線圖。

眾所周知,作為全球半導(dǎo)體工藝研發(fā)的核心樞紐,IMEC依托頂尖科研團(tuán)隊(duì)、先進(jìn)基礎(chǔ)設(shè)施,以及產(chǎn)學(xué)研協(xié)同創(chuàng)新的獨(dú)特模式,長(zhǎng)期引領(lǐng)行業(yè)技術(shù)發(fā)展,在半導(dǎo)體領(lǐng)域的權(quán)威性與前瞻性備受業(yè)界認(rèn)可。

正因如此,IMEC對(duì)半導(dǎo)體未來(lái)路線圖的預(yù)測(cè),不僅展現(xiàn)了其對(duì)行業(yè)趨勢(shì)的深刻洞察,更為全球半導(dǎo)體企業(yè)與科研機(jī)構(gòu)提供了極具價(jià)值的參考方向。接下來(lái),本文將聚焦這份最新路線圖,深度剖析其對(duì)未來(lái)半導(dǎo)體技術(shù)發(fā)展的預(yù)測(cè)與展望。

解讀IMEC路線圖

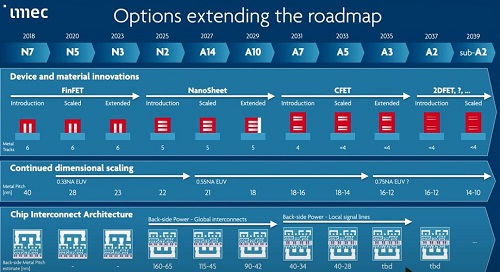

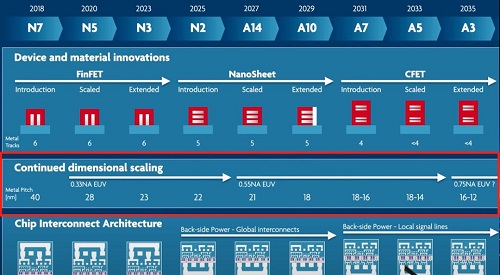

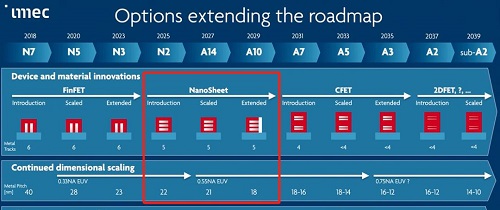

IMEC最近更新了直至2039年的路線圖,這份路線圖預(yù)測(cè)了未來(lái)14年內(nèi)工藝節(jié)點(diǎn)技術(shù)的演進(jìn)過(guò)程,涵蓋了即將出現(xiàn)的新技術(shù)和工藝節(jié)點(diǎn)的演進(jìn)。

IMEC預(yù)測(cè)至2039年的路線圖(圖源:YouTube博主@TechTechPotato)

在其中,IMEC詳細(xì)闡釋了如何對(duì)芯片工藝節(jié)點(diǎn)、晶體管架構(gòu)、芯片互聯(lián)架構(gòu)、背面供電技術(shù)、EUV光刻機(jī)和2D材料等技術(shù)的發(fā)展走勢(shì)和演進(jìn)歷程做出預(yù)測(cè),以及這些技術(shù)從實(shí)驗(yàn)室走向產(chǎn)業(yè)化落地時(shí)的困難與挑戰(zhàn)。

接下來(lái),就讓我們深入探究這一路線圖背后隱藏的半導(dǎo)體行業(yè)未來(lái)發(fā)展的秘密 。

首先,認(rèn)清芯片工藝節(jié)點(diǎn)命名方式

當(dāng)前階段,7納米、5納米、3納米芯片已成為先進(jìn)處理器的主流技術(shù)。但鮮為人知的是,這些數(shù)字早已脫離了物理尺寸的本質(zhì)含義,早已蛻變?yōu)橐环N約定俗成的命名符號(hào)。

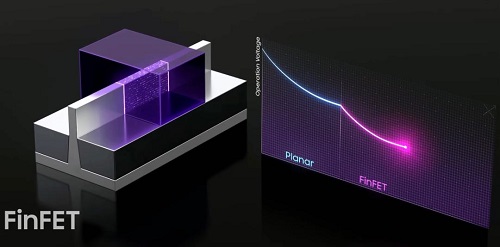

回溯芯片工藝發(fā)展歷程,早期平面晶體管時(shí)代,工藝節(jié)點(diǎn)數(shù)字確實(shí)精準(zhǔn)對(duì)應(yīng)著晶體管柵極間距、線到線間距等物理尺寸,像90納米、65納米等命名,都直接反映了芯片制造中最小特征尺寸。然而隨著半導(dǎo)體技術(shù)逼近物理極限,當(dāng)鰭式場(chǎng)效應(yīng)晶體管(FinFET)取代平面晶體管,將芯片從二維結(jié)構(gòu)推向三維立體架構(gòu)時(shí),這種命名邏輯開始瓦解。

圖源:YouTube博主@TechTechPotato

三維晶體管通過(guò)垂直堆疊結(jié)構(gòu)大幅提升晶體管性能,不再單純依賴尺寸縮小來(lái)實(shí)現(xiàn)性能飛躍。在新的技術(shù)路徑下,芯片性能的提升更多源于架構(gòu)創(chuàng)新與密度優(yōu)化,而非傳統(tǒng)意義上的物理尺寸收縮。

圖源:YouTube博主@TechTechPotato

如今,芯片工藝節(jié)點(diǎn)的命名本質(zhì)上是一種“等效平面晶體管”概念下的延續(xù)性稱謂,是半導(dǎo)體行業(yè)基于歷史命名習(xí)慣和市場(chǎng)認(rèn)知形成的默契。盡管“3納米”“5納米”不再對(duì)應(yīng)實(shí)際柵極間距或最小特征尺寸,但這些數(shù)字依然承載著行業(yè)對(duì)技術(shù)先進(jìn)性的評(píng)判標(biāo)準(zhǔn),成為衡量芯片制造工藝代際演進(jìn)的重要標(biāo)識(shí) 。

FinFET時(shí)代終結(jié)

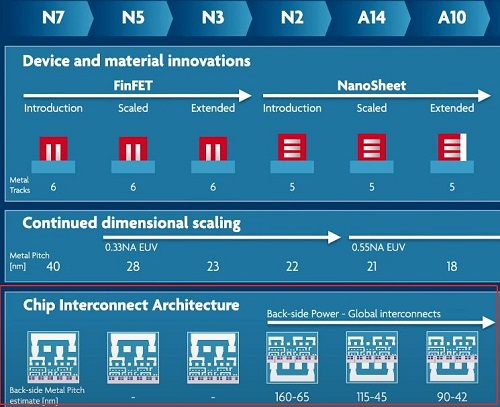

上面的路線圖是IMEC的命名方式,它與臺(tái)積電、三星或Intel對(duì)工藝節(jié)點(diǎn)的命名不太一致。但從IMEC更新的路線圖來(lái)看,2018年到2025年,分別經(jīng)歷了N7、N5、N3和N2工藝節(jié)點(diǎn)的演進(jìn)。

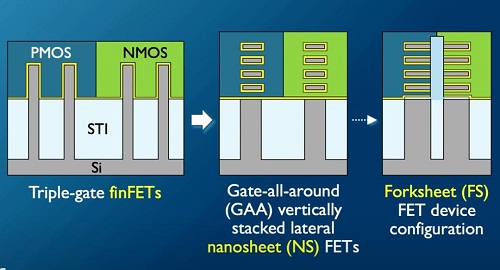

值得關(guān)注的是,隨著N3向N2的演進(jìn),晶體管架構(gòu)也從FinFET(鰭式場(chǎng)效應(yīng)管晶體管)逐漸向NanoSheet(納米片)晶體管架構(gòu)演變。

回顧半導(dǎo)體工藝制程發(fā)展歷程,在過(guò)去的很長(zhǎng)一段時(shí)間里都是平面型晶體管的天下。

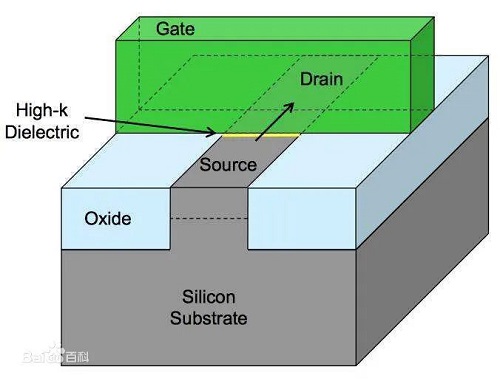

隨著半導(dǎo)體發(fā)展趨勢(shì),使得相同面積下試圖填入更多晶體管的想法逐漸受到重視,因此衍生出微縮整體尺寸的構(gòu)想,柵極尺寸將是微縮重點(diǎn)。

然而平面型晶體管受制于物理結(jié)構(gòu),它只能在柵極(Gate)的一側(cè)控制電流的接通與斷開,而且它的柵極寬度不可能無(wú)限制的縮窄。當(dāng)寬度接近20nm時(shí),柵極對(duì)電流的控制能力將出現(xiàn)斷崖式下降,業(yè)內(nèi)將其稱為“溝道長(zhǎng)度變短導(dǎo)致的所謂短溝道效應(yīng)”,從而出現(xiàn)嚴(yán)重的電流泄露(漏電)現(xiàn)象,最終讓芯片的發(fā)熱和耗電失控。

至此,傳統(tǒng)的平面MOSFET結(jié)構(gòu)走到了盡頭。為了繼續(xù)延續(xù)摩爾定律,胡正明教授于2000年前后提出了FinFET架構(gòu)。

英特爾最早于2011年推出了商業(yè)化的FinFET工藝技術(shù),將FinFET技術(shù)應(yīng)用到了自家的22nm制程工藝上,顯著提高了性能并降低了功耗,之后臺(tái)積電、三星等全球各大廠商陸續(xù)跟進(jìn),采用 FinFET 技術(shù)取得了巨大成功,使得FinFET大放異彩,從16/14nm開始,F(xiàn)inFET成為了半導(dǎo)體器件的主流選擇,成功地推動(dòng)了從22nm到5nm、甚至3nm等數(shù)代半導(dǎo)體工藝的發(fā)展

FinFET最大的特色就是將晶體管的結(jié)構(gòu)從平面變立體,對(duì)柵極形狀進(jìn)行改制,閘門被設(shè)計(jì)成類似魚鰭的叉狀3D架構(gòu),位于電路的兩側(cè)控制電流的接通與斷開,大幅度提升了源極和柵極的接觸面積,減少柵極寬度的同時(shí)降低漏電率,讓晶體管空間利用率大大增加。

FinFET工藝技術(shù)自2011年商業(yè)化以來(lái),體系結(jié)構(gòu)持續(xù)進(jìn)行改進(jìn),以提高性能并減小面積。到了5nm節(jié)點(diǎn)后,雖然使用了EUV光刻技術(shù),但是基于FinFET結(jié)構(gòu)進(jìn)行芯片尺寸的縮小變得愈發(fā)困難。

在先進(jìn)工藝節(jié)點(diǎn)的推進(jìn)過(guò)程中,F(xiàn)inFET芯片工藝節(jié)點(diǎn)正逐漸暴露出局限。當(dāng)制程向更微小尺寸逼近,尤其是在向2nm及以下節(jié)點(diǎn)探索時(shí),量子隧穿效應(yīng)帶來(lái)巨大挑戰(zhàn)。在極薄的柵介電層厚度下,電子的量子特性愈發(fā)凸顯,隧穿電流大幅增加,導(dǎo)致漏電流急劇上升,功耗顯著提高,晶體管性能與可靠性也受到嚴(yán)重影響。

傳統(tǒng)FinFET結(jié)構(gòu)已難以有效應(yīng)對(duì)這一問題,這促使行業(yè)亟需尋找新的解決方案。

NanoSheet時(shí)代,材料、設(shè)備、技術(shù)全新升級(jí)!

在此背景下,NanoSheet(納米片)晶體管架構(gòu)應(yīng)運(yùn)而生。

IMEC的路線圖也指出,隨著N2工藝節(jié)點(diǎn)的到來(lái)將進(jìn)入NanoSheet架構(gòu)時(shí)代。

相較于FinFET,NanoSheet采用了環(huán)繞閘極(GAA)結(jié)構(gòu),導(dǎo)電通道被高介電系數(shù)材料或金屬閘極全方位包圍,即便在通道縮短的情況下,也能極大提升閘極對(duì)通道的控制能力,有效抑制量子隧穿效應(yīng)帶來(lái)的漏電流問題。并且,NanoSheet可通過(guò)垂直堆疊多個(gè)導(dǎo)電通道,在相同尺寸下能提供比FinFET更高的驅(qū)動(dòng)電流,為芯片性能提升與制程微縮提供了新的方向,有望引領(lǐng)半導(dǎo)體行業(yè)突破當(dāng)前困境,繼續(xù)推動(dòng)芯片技術(shù)向更高性能、更低功耗方向發(fā)展。

實(shí)際上,隨著三星、英特爾兩大晶圓代工巨頭幾年前率先轉(zhuǎn)向GAA工藝,就預(yù)示著在更先進(jìn)的節(jié)點(diǎn)上FinFET已走向終結(jié),將逐步被GAA架構(gòu)所取代。

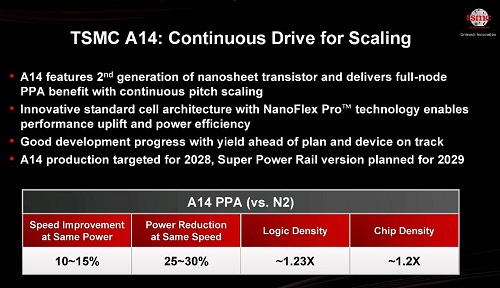

臺(tái)積電也在2025年北美技術(shù)研討會(huì)上披露了其A14(1.4納米級(jí)別)制造技術(shù),承諾該技術(shù)將在性能、功耗和晶體管密度方面顯著優(yōu)于其N2(2納米)工藝。

臺(tái)積電表示,新節(jié)點(diǎn)將依賴第二代環(huán)繞柵極(GAA)納米片晶體管,并通過(guò)NanoFlex Pro技術(shù)提供進(jìn)一步的靈活性。預(yù)計(jì)A14將在2028年進(jìn)入量產(chǎn),但不支持背面供電。支持背面供電的A14版本計(jì)劃于2029年推出。

能看到,將FinFET轉(zhuǎn)移到納米片環(huán)繞柵極技術(shù)(NanoSheet),是通過(guò)使柵極環(huán)繞來(lái)提高晶體管性能的另一種方法。

High NA EUV光刻技術(shù),登臺(tái)

與此同時(shí),從IMEC的路線圖中也能看到,從N2向A14的演講過(guò)程中,實(shí)現(xiàn)這些先進(jìn)工藝芯片所需的光刻機(jī)也在從0.33NA EUV向0.55NA EUV過(guò)渡。

在半導(dǎo)體工藝演進(jìn)歷程中,第一代FinFET晶體管技術(shù)的落地早于EUV光刻技術(shù)的普及。當(dāng)工藝節(jié)點(diǎn)從N5向N3、N2迭代時(shí),標(biāo)準(zhǔn)EUV(0.33 NA EUV)技術(shù)已成為FinFET架構(gòu)的核心支撐,盡管單臺(tái)EUV光刻機(jī)成本高達(dá)1.5-2億美元,但其通過(guò)極紫外光光刻實(shí)現(xiàn)的納米級(jí)圖案轉(zhuǎn)移能力,仍是當(dāng)前先進(jìn)制程提升芯片密度與性能的關(guān)鍵。

隨著工藝向納米片(NanoSheet)架構(gòu)躍遷,半導(dǎo)體行業(yè)正面臨光刻技術(shù)的再次革新——High NA EUV(0.55 NA)技術(shù)將逐步取代標(biāo)準(zhǔn)EUV。

這里的NA(數(shù)值孔徑)本質(zhì)上決定了光刻系統(tǒng)的分辨率極限:標(biāo)準(zhǔn)EUV的0.33 NA技術(shù)通過(guò)13.5nm極紫外光波長(zhǎng),配合多重曝光工藝實(shí)現(xiàn)3nm級(jí)特征尺寸;而High NA EUV將數(shù)值孔徑提升至0.55,結(jié)合更復(fù)雜的光學(xué)系統(tǒng)設(shè)計(jì),可直接實(shí)現(xiàn)2nm以下節(jié)點(diǎn)的單曝光精細(xì)圖案成型,從根本上突破標(biāo)準(zhǔn)EUV在納米片時(shí)代的分辨率瓶頸。

IMEC的路線圖顯示,當(dāng)工藝節(jié)點(diǎn)演進(jìn)至A14(約1.4nm等效平面尺寸)前后,標(biāo)準(zhǔn)EUV的光學(xué)極限將難以支撐納米片架構(gòu)所需的原子級(jí)精度圖案轉(zhuǎn)移。

此時(shí)High NA EUV的登場(chǎng)具有雙重意義:一方面,其通過(guò)更高的光收集效率與更短的焦深控制,解決了標(biāo)準(zhǔn) EUV 在極小節(jié)距下面臨的線寬粗糙度(LWR)與重疊誤差問題;另一方面,納米片架構(gòu)所需的環(huán)繞柵極(GAA)三維結(jié)構(gòu),需要高 NA EUV 提供的垂直維度精度控制,以實(shí)現(xiàn)多層納米片堆疊的均勻性與可靠性。

從技術(shù)邏輯看,EUV光刻技術(shù)的演進(jìn)始終與晶體管架構(gòu)創(chuàng)新深度綁定:FinFET時(shí)代,標(biāo)準(zhǔn)EUV通過(guò)多重曝光滿足了三維鰭片的圖案化需求;而納米片時(shí)代,High NA EUV將以更高的光學(xué)分辨率,支撐起原子層沉積、二維材料集成等下一代制程技術(shù),持續(xù)為AI芯片、量子計(jì)算等前沿領(lǐng)域提供算力密度升級(jí)的基石。這也意味著,當(dāng)A14節(jié)點(diǎn)到來(lái)時(shí),半導(dǎo)體產(chǎn)業(yè)將迎來(lái)光刻技術(shù)與器件架構(gòu)的協(xié)同革命。

背面供電技術(shù),亮相

在傳統(tǒng)晶體管設(shè)計(jì)中,數(shù)據(jù)信號(hào)與電源需通過(guò)平面線路傳輸至復(fù)雜的晶體管陣列,而線路間的串?dāng)_問題始終制約著芯片性能。

為此,從N2工藝節(jié)點(diǎn)開始,半導(dǎo)體行業(yè)迎來(lái)一項(xiàng)關(guān)鍵創(chuàng)新——背面供電技術(shù),并預(yù)計(jì)將在A14至A10等更先進(jìn)節(jié)點(diǎn)中持續(xù)深化,成為突破性能瓶頸的核心方案。

背面供電技術(shù)的核心在于將傳統(tǒng)晶體管正面的電源傳輸路徑轉(zhuǎn)移至芯片背面,通過(guò)三維立體架構(gòu)重構(gòu)電源網(wǎng)絡(luò)。這一變革帶來(lái)雙重優(yōu)勢(shì):

降低串?dāng)_與提升數(shù)據(jù)完整性:電源與數(shù)據(jù)線分離至芯片正反兩面,大幅減少線路間電磁干擾,使高頻數(shù)據(jù)傳輸更穩(wěn)定,尤其適用于AI芯片、數(shù)據(jù)中心處理器等對(duì)信號(hào)完整性要求極高的場(chǎng)景。

優(yōu)化功耗與性能平衡:背面供電可直接為晶體管陣列提供更精準(zhǔn)的電壓控制,配合FinFET、NanoSheet等三維晶體管架構(gòu),實(shí)現(xiàn)“低電壓高驅(qū)動(dòng)”的性能突破,例如在A10節(jié)點(diǎn)中,該技術(shù)可使芯片功耗降低30%的同時(shí)提升20%運(yùn)算速度。

然而,技術(shù)創(chuàng)新伴隨制造復(fù)雜度的飆升,從N2節(jié)點(diǎn)引入背面供電時(shí),需在晶圓背面新增納米級(jí)金屬互連層,同步優(yōu)化全局電源網(wǎng)絡(luò)設(shè)計(jì)。這也是到A14、A10節(jié)點(diǎn),需要結(jié)合High NA EUV光刻技術(shù)的原因所在,通過(guò)0.55NA EUV光刻技術(shù)將供電互連間距縮小至50納米以下,對(duì)薄膜沉積、刻蝕等工藝也提出嚴(yán)苛要求。

IMEC路線圖顯示,背面供電技術(shù)與High NA EUV、2D材料等創(chuàng)新協(xié)同,正推動(dòng)芯片從“尺寸微縮”轉(zhuǎn)向“架構(gòu)革新”的技術(shù)范式升級(jí)。

筆者此前曾在《背面供電技術(shù),越來(lái)越熱!》一文中詳細(xì)介紹過(guò)背面供電技術(shù)的優(yōu)勢(shì)以及晶圓代工三巨頭在背面供電技術(shù)領(lǐng)域的布局和方案,感興趣的朋友可以跳轉(zhuǎn)查閱,在此不做贅述了。

叉片晶體管(Forksheet),1nm的有力候選架構(gòu)

如IMEC路線圖所示,NanoSheet時(shí)代每個(gè)晶體管都有3片納米片。但到A10節(jié)點(diǎn)上,會(huì)看到這個(gè)設(shè)計(jì)有一個(gè)白色的豎條,這就是業(yè)界所說(shuō)的? ForkSheet Transistors(叉片晶體管)?。

該設(shè)計(jì)曾被認(rèn)為是一個(gè)獨(dú)立的本質(zhì)上超越了納米片的晶體管設(shè)計(jì)系列,但如今像IMEC這樣的公司和研究機(jī)構(gòu)以及最終的晶圓代工廠,都將叉片晶體管更多地視為納米片系列。

叉片晶體管(Forksheet)是一種先進(jìn)的晶體管架構(gòu),是納米片晶體管(Nanosheet FET)的延伸和發(fā)展,主要用于實(shí)現(xiàn)更小的晶體管尺寸和更高的集成密度,以滿足未來(lái)半導(dǎo)體工藝中對(duì)微縮的需求。

叉片晶體管的核心特點(diǎn)是其分叉式的柵極結(jié)構(gòu)。在這種結(jié)構(gòu)中,n型晶體管(nFET)和p型晶體管(pFET)被集成在同一結(jié)構(gòu)中,但由絕緣壁(如氧化物或氮化物)隔開。這種設(shè)計(jì)允許nFET和pFET之間的間距進(jìn)一步縮小,從而減少標(biāo)準(zhǔn)單元的面積。

叉片晶體管通常基于納米片堆疊技術(shù),納米片作為晶體管的溝道部分,其厚度和寬度可以精確控制,以實(shí)現(xiàn)更好的靜電控制和更高的驅(qū)動(dòng)電流。叉片晶體管可以實(shí)現(xiàn)垂直堆疊,即多個(gè)晶體管層疊在一起。這種堆疊方式進(jìn)一步提高了晶體管的密度,同時(shí)減少了芯片的橫向面積。

由于叉片晶體管的結(jié)構(gòu)允許更緊密的器件布局,其寄生電容更低,從而提高了器件的性能。相比傳統(tǒng)的FinFET和納米片晶體管,叉片晶體管需要0.55 NA EUV才能做到,將金屬間距(Metal Pitch)縮小到18納米。

叉片晶體管被認(rèn)為是未來(lái)1nm及以下技術(shù)節(jié)點(diǎn)的有力候選架構(gòu)。它能夠?qū)⒓{米片晶體管的可微縮性進(jìn)一步延伸,為半導(dǎo)體工藝的持續(xù)發(fā)展提供了新的方向。

CFET,埃米時(shí)代的主流架構(gòu)

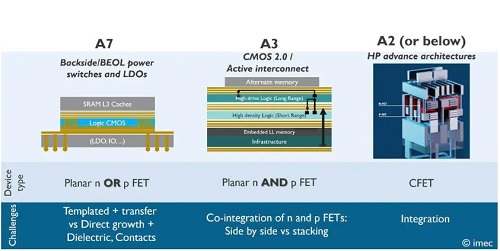

IMEC的邏輯技術(shù)路線圖展示了納米片 (NanoSheet) 時(shí)代從N2延伸到A10節(jié)點(diǎn),并采用叉片晶體管(ForkSheet),之后過(guò)渡到A7及更高節(jié)點(diǎn)的CFET(互補(bǔ)場(chǎng)效應(yīng)晶體管)時(shí)代。

在半導(dǎo)體工藝節(jié)點(diǎn)持續(xù)演進(jìn)的歷程中,從早期平面晶體管到FinFET,再到NanoSheet,每一次變革都推動(dòng)著芯片性能與密度的提升。

從時(shí)間維度來(lái)看,依據(jù)IMEC路線圖,自2031年A7節(jié)點(diǎn)起,CFET技術(shù)將逐步從實(shí)驗(yàn)室走向產(chǎn)業(yè)化前沿,至2035年左右的A3節(jié)點(diǎn)期間將實(shí)現(xiàn)CFET的大規(guī)模應(yīng)用。

據(jù)了解,CFET突破了傳統(tǒng)晶體管架構(gòu),將晶體管從單一平面拓展至立體空間。其不再依賴三個(gè)納米片構(gòu)建,而是通過(guò)n-FET和p-FET納米片相互堆疊,形成高度集成的3D設(shè)計(jì)。

通過(guò)垂直堆疊的巧妙設(shè)計(jì),使得在相同晶體管尺寸下,實(shí)現(xiàn)了晶體管密度的翻倍,從而實(shí)現(xiàn)更強(qiáng)大的功能,并提高功率效率和性能。這種密度提升帶來(lái)的直接效益,便是SRAM存儲(chǔ)容量直接翻番,為對(duì)內(nèi)存需求極為苛刻的高性能計(jì)算、數(shù)據(jù)中心等領(lǐng)域,提供了更為充裕的存儲(chǔ)資源,有力支撐復(fù)雜運(yùn)算與海量數(shù)據(jù)處理。

在CFET節(jié)點(diǎn),為進(jìn)一步挖掘性能潛力,背面供電技術(shù)搭配局部信號(hào)線的創(chuàng)新組合嶄露頭角。傳統(tǒng)芯片中,數(shù)據(jù)信號(hào)與電源線在晶體管平面線路中交織,串?dāng)_問題長(zhǎng)期制約性能。而背面供電技術(shù)將電源路徑轉(zhuǎn)移至晶體管背面,N-MOS和P-MOS協(xié)同配合,有效減少線路間電磁干擾,確保數(shù)據(jù)傳輸?shù)母咄暾裕瑸楦哳l、高速信號(hào)傳輸筑牢根基,大幅提升芯片運(yùn)算的穩(wěn)定性與準(zhǔn)確性。

當(dāng)然CFET面臨的問題還有很多,特別是未來(lái)量產(chǎn)過(guò)程中,CFET的制造將更加困難。一方面CFET架構(gòu)比GAA架構(gòu)的3D結(jié)構(gòu)更高,結(jié)構(gòu)縱橫比的增加將帶來(lái)更大的制造挑戰(zhàn);另一方面,CFET需要非常高的摻雜劑激活,需要非常低的接觸電阻率,需要為CFET提供特殊的高k/金屬柵極,而且這些都必須在非常高的堆疊結(jié)構(gòu)中完成。

還需要注意的是,N MOS和P MOS晶體管制造工藝存在顯著差異,N型與P型晶體管在硅片制造流程中,對(duì)溫度、工藝步驟等條件要求大相徑庭,對(duì)工藝控制精度提出了近乎嚴(yán)苛的挑戰(zhàn)。眾多科研團(tuán)隊(duì),如IEEE會(huì)議上的眾多研究項(xiàng)目,正全力攻堅(jiān)這一難題,力求在保證CFET性能與密度優(yōu)勢(shì)的同時(shí),實(shí)現(xiàn)高效、穩(wěn)定的量產(chǎn)。

臺(tái)積電也曾表示,CFET架構(gòu)的重大挑戰(zhàn)可能會(huì)導(dǎo)致工藝復(fù)雜性和成本增加。為了克服這些挑戰(zhàn),必須仔細(xì)選擇集成方案,以降低工藝復(fù)雜性,并最大限度地減少對(duì)新材料和工藝能力的要求。

Hyper NA EUV(0.75 NA),光刻技術(shù)突破物理極限

上文提到,CFET的制造并非坦途。

CFET技術(shù)通過(guò)垂直堆疊N型和P型晶體管,將芯片密度提升至傳統(tǒng)架構(gòu)的兩倍,但這也對(duì)光刻工藝提出了挑戰(zhàn):

三維結(jié)構(gòu)的層間對(duì)準(zhǔn):CFET的多層堆疊結(jié)構(gòu)要求各層圖案的對(duì)準(zhǔn)精度達(dá)到亞納米級(jí),Hyper NA EUV的高分辨率能力可確保不同層間晶體管的精確互連,減少信號(hào)延遲。

高密度布線的刻蝕需求:CFET節(jié)點(diǎn)的金屬互連層間距已逼近10納米,Hyper NA EUV憑借其卓越的分辨率,可在光刻膠上形成更清晰的電路圖案,配合先進(jìn)刻蝕技術(shù),實(shí)現(xiàn)納米級(jí)布線的精確轉(zhuǎn)移。

屆時(shí),為契合CFET超高精度和密度的制造需求,High NA EUV(0.55 NA)光刻技術(shù)已難以滿足其對(duì)精度的極致追求,Hyper NA EUV(0.75 NA)技術(shù)應(yīng)運(yùn)而生,成為攻克CFET制造難題的關(guān)鍵利器。這一技術(shù)突破不僅將光刻精度推向新的極限,更標(biāo)志著半導(dǎo)體制造工藝進(jìn)入“原子級(jí)操控”時(shí)代。

Hyper NA EUV技術(shù)通過(guò)將數(shù)值孔徑(NA)提升至0.75,使光刻系統(tǒng)能夠?qū)崿F(xiàn)接近10納米的特征尺寸,為CFET的三維堆疊架構(gòu)提供了必要的加工精度。

ASML正研發(fā)0.75NA的Hyper NA EUV系統(tǒng),目標(biāo)是在2035年實(shí)現(xiàn)0.3nm及以下制程。但技術(shù)障礙巨大,例如需要制造具有原子級(jí)精度的米級(jí)反射鏡,以及需要管理復(fù)雜的光學(xué)系統(tǒng)。其反射鏡不僅需維持更高精度,還需通過(guò)精密鉆孔技術(shù)實(shí)現(xiàn)光束的復(fù)雜調(diào)控,這種“在米級(jí)鏡片上鉆原子級(jí)孔”的工藝挑戰(zhàn)堪稱工程學(xué)奇跡。

ASML技術(shù)高級(jí)副總裁Jos Benschop曾指出,盡管高數(shù)值孔徑和超高數(shù)值孔徑技術(shù)可能延續(xù)摩爾定律,但量子隧穿效應(yīng)和原子間距等物理極限,可能在本世紀(jì)中葉前制約技術(shù)進(jìn)步。

根據(jù)IMEC披露的路線圖來(lái)看,利用0.3NA的標(biāo)準(zhǔn)型EUV光刻機(jī)可以支持到2025年N2節(jié)點(diǎn)的量產(chǎn),再往下就需要通過(guò)多重曝光技術(shù)來(lái)實(shí)現(xiàn),但支持到2027年量產(chǎn)的A14將會(huì)是其極限。

0.55NA的High NA EUV光刻機(jī)則可以支持到2033年A5的制程節(jié)點(diǎn)。再往下就可能必須要采用0.75NA的Hyper NA EUV光刻機(jī),或許可以支持到A2(0.2nm)以下的制程節(jié)點(diǎn),這里路線圖上打了一個(gè)問號(hào),所以不確定Hyper NA EUV光刻機(jī)能否支持下去。

2DFET,降維打擊?

即使到了CFET時(shí)代,短溝道效應(yīng)依然會(huì)再度使進(jìn)一步的微縮變得棘手。隨著柵極和溝道長(zhǎng)度不斷縮短,需要將半導(dǎo)體溝道做得越來(lái)越薄,以限制電流流動(dòng)的通道,減少器件關(guān)斷時(shí)載流子泄漏的可能性。若要將CFET器件拓展到A2技術(shù)節(jié)點(diǎn),使導(dǎo)電溝道長(zhǎng)度降至10nm以下,則硅溝道厚度也必須小于10nm。然而如此薄的硅溝道中,載流子遷移率和器件導(dǎo)通電流會(huì)顯著下降。

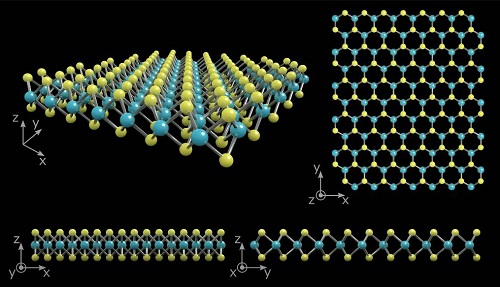

這正是二維半導(dǎo)體(特別是過(guò)渡金屬硫族化合物MX2)所能帶來(lái)的機(jī)遇。

IMEC路線圖顯示,到2037年,當(dāng)工藝節(jié)點(diǎn)演進(jìn)至A2,基于單原子層2D材料的2DFET將取代CFET架構(gòu),搭配0.75 NA EUV光刻技術(shù),推動(dòng)芯片密度與性能實(shí)現(xiàn)指數(shù)級(jí)躍升。

2D材料以其原子級(jí)厚度展現(xiàn)出獨(dú)特優(yōu)勢(shì):

過(guò)渡金屬二元化合物的潛力:二硫化鎢(WS?)、二碲化鎢(WTe?)等材料天然形成單分子層晶體結(jié)構(gòu),其原子級(jí)薄的溝道層可將柵極電容提升至傳統(tǒng)硅材料的10倍以上,同時(shí)抑制漏電流。適用于邏輯器件和高頻應(yīng)用。

石墨烯的局限性:盡管石墨烯擁有優(yōu)異的導(dǎo)電性,但其零帶隙特性導(dǎo)致無(wú)法實(shí)現(xiàn)晶體管的開關(guān)功能,因此2DFET研發(fā)更側(cè)重帶隙可調(diào)的過(guò)渡金屬硫化物/碲化物。

2DFET通過(guò)將溝道層壓縮至單原子層,徹底重構(gòu)晶體管工作原理。相較于CFET的三維堆疊架構(gòu),2DFET則代表著半導(dǎo)體制造的“維度降級(jí)”創(chuàng)新:CFET依賴垂直堆疊提升密度,而2DFET通過(guò)材料維度縮減實(shí)現(xiàn)性能突破,其制造流程可簡(jiǎn)化30%以上(減少沉積/刻蝕步驟)。

二維溝道材料在極度微縮節(jié)點(diǎn)上可帶來(lái)顯著性能提升,這點(diǎn)已引起主要芯片廠商和學(xué)術(shù)界的興趣。他們紛紛加大對(duì)二維材料研發(fā)的投入,以克服將二維材料引入最先進(jìn)節(jié)點(diǎn)所面臨的障礙。

IMEC預(yù)計(jì),到2039年,基于二維材料的第二代2DFET將成為主流。不過(guò),引入二維材料的同時(shí)仍附帶一系列挑戰(zhàn),會(huì)增加向A2節(jié)點(diǎn)導(dǎo)入時(shí)的成本和集成難度。

IMEC也提到了以下多方面的挑戰(zhàn)與問題:

二維材料的沉積:首先,要如何在晶圓上形成2D材料層是一大挑戰(zhàn)。對(duì)于需要高性能器件的應(yīng)用,主要有兩條路線:

(1)直接在目標(biāo)襯底上生長(zhǎng)2D材料。

直接生長(zhǎng)通常需要特定襯底,并且在高溫(約1000℃)下進(jìn)行。如果需要與工業(yè)兼容的工藝和材料,則這種生長(zhǎng)襯底未必理想,不利于高晶化度,從而降低薄膜性能。不過(guò),直接生長(zhǎng)可能具備一致性好、可覆蓋整片晶圓以及與工業(yè)流程相容等優(yōu)點(diǎn)。

(2)在“生長(zhǎng)襯底”上先行生長(zhǎng),然后再將該層轉(zhuǎn)移到目標(biāo)襯底。

第二種方法是在外部“理想”襯底上生長(zhǎng),得到高性能薄膜后,再將其轉(zhuǎn)移到目標(biāo)晶圓。轉(zhuǎn)移本身溫度可低得多(約300℃),與直接生長(zhǎng)相比可避免對(duì)目標(biāo)晶圓過(guò)度加熱。然而,轉(zhuǎn)移增加了流程步驟,也可能影響成本與制程良率。

柵極疊層與介電沉積:第二項(xiàng)挑戰(zhàn)與柵極疊層及介電質(zhì)沉積相關(guān)。有意思的是,促使二維材料能做到超薄的主要原因(即2D原子層之間僅有很弱的范德華力)也使得介電層沉積更加復(fù)雜。這些薄層表面幾乎無(wú)懸掛鍵,使得傳統(tǒng)在硅上使用極為成熟的沉積方法(原子層沉積ALD)變得困難。

低電阻源/漏接觸:第三大挑戰(zhàn)是形成低電阻的源極/漏極接觸。對(duì)硅而言,通過(guò)在源漏區(qū)與金屬相接觸時(shí)生成肖特基勢(shì)壘,并通過(guò)隧穿注入載流子,從而得到低接觸電阻。常用方法包括對(duì)源漏區(qū)進(jìn)行高摻雜,或在其上形成金屬硅化物。然而這些方法在超薄的二維材料層上非常困難。科研人員因此在探索替代方案。

二維材料的摻雜:不僅是為了獲得低電阻接觸,還需要摻雜來(lái)調(diào)節(jié)溝道的閾值電壓(Vth)以及降低寄生電阻。但對(duì)2D材料進(jìn)行傳統(tǒng)離子注入會(huì)嚴(yán)重破壞其晶格,進(jìn)而顯著降低其傳輸特性。因?yàn)樵谌绱藰O薄的結(jié)構(gòu)中,即使替換一個(gè)晶格原子也會(huì)產(chǎn)生遠(yuǎn)比三維材料更嚴(yán)重的影響。目前仍在探索其他摻雜方式(如靜電摻雜或表面摻雜),但尚無(wú)公認(rèn)的明確解決方案。

p型FET與n型FET:在CMOS技術(shù)中,n型和p型FET皆不可或缺。對(duì)傳統(tǒng)CMOS來(lái)說(shuō),硅既可做n型,又能做p型;但尚無(wú)發(fā)現(xiàn)任何單一2D材料可同時(shí)滿足n型與p型器件的最佳性能:例如莫S?(MoS2)適合做n型,而WSe2最具p型潛力。

制造集成及對(duì)可靠性與一致性的更高需求:迄今,大部分研究主要在實(shí)驗(yàn)室進(jìn)行,可在厘米級(jí)樣品上做hero devices。但要走向與300mm晶圓兼容的工業(yè)規(guī)模生產(chǎn),需要大量研發(fā)投入。與此同時(shí),器件的可靠性與一致性也必須得到大幅提升。

寫在最后

IMEC的半導(dǎo)體工藝路線圖,不僅是技術(shù)演進(jìn)的指南,更揭示了半導(dǎo)體行業(yè)從“尺寸微縮”到“架構(gòu)革新”的范式轉(zhuǎn)變。

從FinFET到NanoSheet,從CFET到2DFET,每一次晶體管架構(gòu)的革新,都伴隨著EUV光刻、背面供電等技術(shù)的突破,推動(dòng)芯片密度與性能不斷躍升。

然而,技術(shù)前行之路從非坦途。量子隧穿效應(yīng)、2D材料制備難題、超精密光刻挑戰(zhàn)等,無(wú)不考驗(yàn)著行業(yè)智慧,需全行業(yè)在設(shè)備、材料與工藝上持續(xù)突破。正如IMEC路線圖所展現(xiàn)的,在產(chǎn)學(xué)研協(xié)同創(chuàng)新的驅(qū)動(dòng)下,半導(dǎo)體行業(yè)正以驚人的創(chuàng)造力,將一個(gè)個(gè)“不可能”變?yōu)椤翱赡堋薄?/p>