6 月 22 日消息,英特爾在 2025 年超大規(guī)模集成電路技術(shù)與電路研討會(Symposium on VLSI Technology and Circuits)上披露下一代 Intel 18A 工藝節(jié)點技術(shù)細(xì)節(jié)。

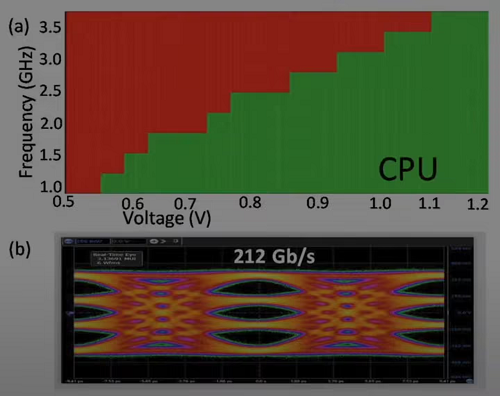

該節(jié)點將取代現(xiàn)有 Intel 3 節(jié)點,優(yōu)化頻率與電壓調(diào)節(jié)能力,后續(xù)將應(yīng)用于消費級處理器“Panther Lake”以及服務(wù)器處理器 Clearwater Forest(純 E 核 Xeon)等產(chǎn)品。

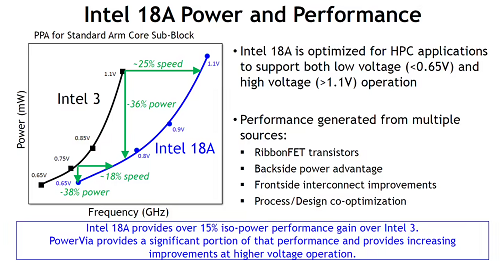

據(jù)英特爾工程師介紹,采用 RibbonFET(全環(huán)繞柵極 GAA)與 PowerVia(背側(cè)供電)技術(shù)的 Intel 18A 制程相較 Intel 3 實現(xiàn)了 30% 以上密度提升與“全節(jié)點性能進步”,同時提供高性能(HP)、高密度(HD)庫,兼具完整設(shè)計能力與易用性。

得益于 RibbonFET 技術(shù),Intel 18A 相較于使用 FinFET 的 Intel 3 實現(xiàn)大幅跨越。RibbonFET 主要優(yōu)勢在于:

優(yōu)化柵極靜電特性,單位面積有效寬度更大、寄生電容更低,設(shè)計靈活性進一步提升;

為 180H / 160H 庫引入多種 Ribbon 寬度,通過 DTCO(設(shè)計工藝協(xié)同優(yōu)化)平衡邏輯功耗 / 漏電與性能,為 SRAM 定制 Bitcell 優(yōu)化的 Ribbon 寬度 —— 全面增強 18A 節(jié)點芯片性能與設(shè)計潛力。

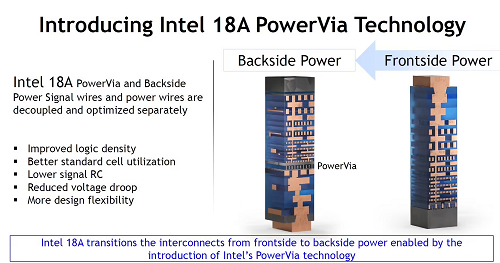

另外,18A 采用了 PowerVia 技術(shù),以背側(cè)供電走線替代前側(cè)走線,實現(xiàn)供電網(wǎng)絡(luò)解耦與獨立優(yōu)化,從而實現(xiàn)多重增益:

邏輯密度提升

標(biāo)準(zhǔn)單元利用率改善

信號 RC 值降低

電壓降(droop)收縮

設(shè)計靈活性進一步實現(xiàn)拓展

通過這些改進,Intel 18A 相比 Intel 3 實現(xiàn)了超過 15% 的單位功耗性能提升:

性能能效:1.1V 電壓下,18A 同頻性能較 Intel 3 提升約 25%;且支持 0.65V 以下低電壓運行,同頻功耗最多降 38%。

密度提升:18A 較 Intel 3 最高實現(xiàn) 39%(平均 30%)密度提升,背側(cè)供電使單元利用率提 8-10%,單元利用率提高 8-10%,并將極端 IR 電壓降收縮至原來的 10%。

參數(shù)對比:HP 庫高度從 Intel 3 的 240nm 降至 180nm,HD 庫從 210nm 降至 160nm;M0 / M2 金屬層間距從 30/42nm 優(yōu)化為 32/32nm。

SRAM 縮放:18A 的高電流單元(HCC)密度較 Intel 3 提升 30%,HCC、HDC SRAM 面積分別達 0.0230μm2、0.0210μm2。

英特爾表示,18A 工藝將持續(xù)迭代:2026-2028 年將推出 18A-P 和 18A-PT 衍生版本(IT之家注:已于 2025 年 Direct Connect 大會公布),并開放客戶基于這些節(jié)點實現(xiàn)芯片量產(chǎn)。