為什么非常穩(wěn)定的開關(guān)模式電源仍可能由于負(fù)電阻而產(chǎn)生振蕩

2023-06-06

作者:Thomas Ginell,現(xiàn)場應(yīng)用工程師

來源:ADI

問題:

為什么穩(wěn)定的開關(guān)模式電源仍會產(chǎn)生振蕩?

答案:

非常穩(wěn)定的開關(guān)模式電源(SMPS)仍可能由于其在輸出端的負(fù)電阻而產(chǎn)生振蕩。在輸入端,可以將SMPS看作一個小信號負(fù)電阻。其與輸入電感和輸入端電容一起可形成一個無阻尼振蕩電路。本文將就這一問題的分析和解決方案進(jìn)行探討。將LTspice?用于仿真。

簡介

開關(guān)模式調(diào)節(jié)器的功能是,以最有效的方式將輸入電壓轉(zhuǎn)換為經(jīng)調(diào)整的恒定輸出電壓。

這個過程會有些損耗,且效率的衡量公式如下

我們假設(shè)調(diào)節(jié)器可使VOUT保持恒定,且負(fù)載電流IOUT可以看作是一個恒定值,不會隨VIN而變化。圖1顯示了IIN隨VIN而變化的圖。

圖1.輸入電流隨輸入電壓的變化。

如圖2所示,我們在工作點12 V處畫了一條切線。切線的斜率將等于隨工作點電壓而變化的小信號電流變化。

圖2.在12 V處添加了一條切線。

切線的斜率可視為轉(zhuǎn)換器的輸入電阻RIN或輸入阻抗RIN = ZIN (f = 0)。頻率f > 0時輸入阻抗會發(fā)生什么,該點我們將在本文后續(xù)部分進(jìn)行討論。現(xiàn)在,我們假設(shè)在ZIN (f) = ZIN (f = 0)頻率范圍內(nèi)該阻抗為常數(shù)。可以觀察到有一點十分有趣:由于斜率為負(fù),這個小信號輸入電阻也為負(fù)。如果輸入電壓增加,電流就會減少,反之亦然。

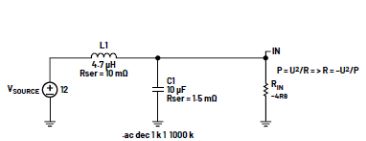

首先,我們可以看看圖3中的電路,在該電路中,SMPS與其饋電中的輸入電容和輸入電感一起形成了一個由負(fù)電阻衰減的高Q值LC電路。如果負(fù)電阻在電路中占主導(dǎo),則其會變成在接近諧振頻率時產(chǎn)生無阻尼振蕩的振蕩器。在實踐中,大信號振蕩中的非線性度會對振蕩頻率及其波形產(chǎn)生影響。

該電路中的電感可以是輸入濾波器的電感,也可以是線纜的電感。為使電路穩(wěn)定,您需要使用正電阻來支配負(fù)電阻,以使電路衰減。而這樣會出現(xiàn)問題,因為您不希望電感的串聯(lián)電阻過高,否則就會增加散熱,并降低效率。您也不希望電容的串聯(lián)電阻過高,否則電壓紋波將增加。

圖3.SMPS的小信號模型及其輸入網(wǎng)絡(luò)。

分析問題

設(shè)計電源系統(tǒng)時,可能會遇到以下問題:

▲我的設(shè)計中是否存在此類問題?

▲我如何分析該問題?

▲如果存在問題,如何解決?

如果我們假設(shè)在輸入電路中只有一個有源元件作為負(fù)電阻,那么我們可以通過直接觀察SMPS的輸入來分析阻抗。

如果在頻率范圍內(nèi)阻抗的實部大于0,則電路穩(wěn)定,前提是假設(shè)SMPS控制回路本身穩(wěn)定。我們可以通過解析或仿真來進(jìn)行分析。即使輸入電路有許多元件,也可以輕松進(jìn)行仿真,而解析設(shè)計則更為困難。我們將從使用LTspice的仿真開始。

首先,通過公式推導(dǎo)計算負(fù)電阻的一階近似值。

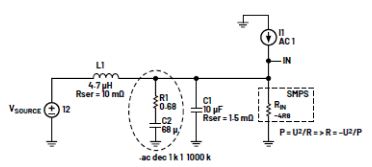

如果轉(zhuǎn)換器的輸入功率為30 W,則當(dāng)電壓為12 V時,可通過計算得到電阻為–122/30 Ω = –4.8 Ω。輸入濾波器由LC濾波器組成。假設(shè)輸入由低電阻電源饋入,則可以簡化等效電路,并將其歸結(jié)為圖4所示的示例原理圖,其中理想情況下電源為0 Ω。

圖4.SMPS及其輸入網(wǎng)絡(luò)示例。

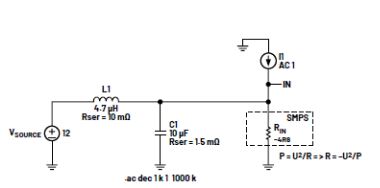

如果我們在仿真中增加了一個電流源,則可以按V(IN)/I(I1)計算輸入端的小信號電阻。在LTspice中可輕松對該過程進(jìn)行仿真。

圖5.在網(wǎng)絡(luò)中添加電流源激勵(I1)。

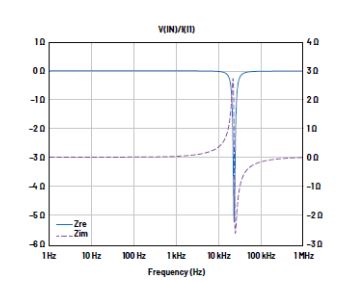

圖6.在注入點的電阻仿真結(jié)果。

從阻抗圖中可以看出,諧振峰值約為23 kHz。在LC電路的諧振頻率附近,阻抗的相位在90°至270°范圍內(nèi),這意味著阻抗的實部為負(fù)。我們也可以在笛卡爾坐標(biāo)中繪制阻抗圖,并直接查看其實部。此外值得注意的是,由于高Q,實部在諧振頻率下變得非常大(–3 Ω)。

圖7.笛卡爾坐標(biāo)中與圖6所示相同的阻抗。

圖8顯示的是一個時域仿真,在1 ms時注入干擾瞬態(tài)電壓,結(jié)果表明干擾瞬態(tài)電壓會導(dǎo)致不穩(wěn)定性。

圖8.在1 ms時注入瞬態(tài)電壓的仿真。

如之前所述,顯然我們不希望在設(shè)計中為無功部件增加串聯(lián)電阻。在不會對設(shè)計產(chǎn)生不利影響(除尺寸)的情況下,我們可以做的一件事情就是增加一個阻尼電容,且該電容的電容量與適用于在相關(guān)頻率下控制阻抗的串聯(lián)電阻相同或更大。為獲得合理的阻尼效果,電容尺寸應(yīng)至少比已存在輸入電容大一個小因數(shù)。串聯(lián)電阻應(yīng)顯著低于SMPS的負(fù)電阻,但在相關(guān)頻率下應(yīng)等于或大于所增加電容的電抗。如果增加了一個非陶瓷bulk電容,同時假設(shè)元件變化存在裕量,則其寄生ESR本身可能就足夠了。

如何選擇阻尼電容及其串聯(lián)電阻

在LTspice中反復(fù)試錯,或如果電路比較簡單,則使用以下分析方法檢索值。

首先,計算輸入電容和輸入電感的諧振頻率,如果與輸入濾波器相比,電感另一端的電源可視為低電阻,則輸入電容和輸入電感可視為并聯(lián)在SMPS輸入與AC接地之間。

C = 總濾波器電容

L = 總濾波器電感

在諧振頻率下,電容和電感的電抗絕對值相等。

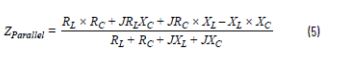

諧振頻率下的總并聯(lián)阻抗定義為以下復(fù)雜公式:

XL = 電感的電抗

XC = 電容的電抗

RL = 電感的串聯(lián)電阻

RC = 電容的串聯(lián)電阻

由于XL = –XC,且RL和RC通常遠(yuǎn)小于電抗,因此可以近似計算并簡化該公式。

最后,輸入XL = √L/C和XC = –√L/C的值。

此為諧振頻率下輸入濾波器的等效并聯(lián)電阻。

如果該電阻低于SMPS負(fù)電阻的絕對值,則正電阻處于主導(dǎo),且輸入濾波器網(wǎng)絡(luò)將保持穩(wěn)定。

如果高于絕對值,或存在一點裕量,則必須增加阻尼。

可以通過之前所述的額外電容與用于實現(xiàn)最佳阻尼的串聯(lián)電阻來增加阻尼。參見圖9中的R1和C2。

圖9.在輸入端添加了阻尼網(wǎng)絡(luò)R1和C2。

額外電容的值必須等于或大于濾波器電容。在輸入濾波器的諧振頻率下,電容的電抗必須顯著低于SMPS負(fù)電阻的絕對值,如果滿足第一個條件,則通常為這種情況。

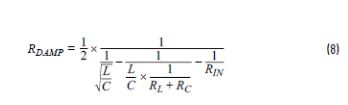

選擇額外電容的尺寸是一個折中的方法。我們的一個設(shè)計目標(biāo)是接近輸入濾波器的臨界阻尼。可以通過計算達(dá)到臨界阻尼的并聯(lián)電阻來實現(xiàn)這一目標(biāo),當(dāng)并聯(lián)電阻為電抗值的一半(Q = 1/2)時就會出現(xiàn)臨界阻尼。這意味著輸入濾波器的并聯(lián)電阻應(yīng)等于諧振頻率下輸入濾波器C和L的電抗的一半,而該輸入濾波器與SMPS負(fù)電阻并聯(lián),SMPS負(fù)電阻則與所述(負(fù))阻尼電阻RDAMP并聯(lián)。

如果L/C × 1/(RL + RC)的值和|RIN|的值遠(yuǎn)大于√L/C的值,則公式可簡化為:

相對于阻尼電阻,應(yīng)選擇合理尺寸的阻尼電容。建議選擇XDAMP = 1/3 × RDAMP,這意味著,如果上述L/C × 1/(RL + RC)和|RIN|遠(yuǎn)大于√L/C的假設(shè)仍有效,則CDAMP = 6 × C。

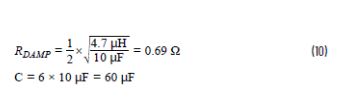

輸入將不會達(dá)到但會接近臨界阻尼。如果可以容許更多的振鈴,且設(shè)計裕度穩(wěn)定,則可以使用較小的C。在本例中,

我們按照圖10所示使用0.68 Ω和68 μF。圖11和圖12顯示了干擾的時域響應(yīng)和AC阻抗。

圖10.使用建議元件值的阻尼網(wǎng)絡(luò)。

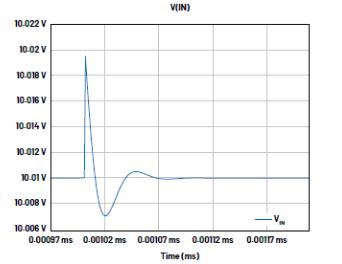

圖11.時域瞬態(tài)響應(yīng)。

圖12.阻抗與頻率的關(guān)系。

負(fù)電阻的頻率特性

我們可以假設(shè)電源單元(PSU)將在控制回路的回路帶寬范圍外停止發(fā)揮負(fù)電阻的作用,但這通常是錯誤的假設(shè)。如果PSU處于電流模式下,則為保持調(diào)節(jié)器所需的電流峰值,針對正輸入電壓變化的即時響應(yīng)為占空比變化。這意味著,當(dāng)電壓增加時,輸入電流將暫時減小,反之亦然。

因此,在開關(guān)頻率范圍內(nèi)可保持負(fù)電阻。如果PSU采用電壓模式控制,則通常會有一個從輸入電壓到占空比的前饋功能,該功能將使轉(zhuǎn)換器立即響應(yīng)輸入電壓變化,從而使輸出電壓保持恒定不變。這也是由于在開關(guān)頻率范圍內(nèi)可保持負(fù)電阻造成的。問題在于,減少控制回路帶寬通常無法解決這個問題。此外,如果調(diào)節(jié)下游轉(zhuǎn)換器,仍可將未經(jīng)調(diào)節(jié)的總線轉(zhuǎn)換器看作負(fù)電阻。

結(jié)論

由于輸入網(wǎng)絡(luò)匹配較差造成的電源振蕩可能會被誤認(rèn)為是控制回路不穩(wěn)定。但如果知曉這是輸入網(wǎng)絡(luò)和負(fù)電阻相關(guān)的振蕩,則可以在LTspice中輕松分析和優(yōu)化該特性。LTspice是一款免費的高性能SPICE仿真器軟件,包括原理圖捕獲圖形界面。可探測原理圖以產(chǎn)生仿真結(jié)果,通過LTspice內(nèi)置波形查看器輕松探索。與其他SPICE解決方案相比,LTspice的增強(qiáng)功能和模型可改善模擬電路仿真。

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應(yīng)用-AET<<