雖然臺積電3nm芯片已經(jīng)量產(chǎn),但截止昨天,我們都沒有看到芯片公司發(fā)布相關(guān)產(chǎn)品。到了今天,這個局面終于被打破了。

美國芯片公司Marvell表示,公司基于臺積電 3 納米 (3nm) 工藝打造的數(shù)據(jù)中心芯片正式發(fā)布。據(jù)Marvell介紹,公司在該節(jié)點中的業(yè)界首創(chuàng)硅構(gòu)建模塊包括 112G XSR SerDes(串行器/解串行器)、Long Reach SerDes、PCIe Gen 6 / CXL 3.0 SerDes 和 240 Tbps 并行芯片到芯片互連。

按照Marvell所說,SerDes 和并行互連在芯片中充當高速通道,用于在chiplet內(nèi)部的芯片或硅組件之間交換數(shù)據(jù)。與 2.5D 和 3D 封裝一起,這些技術(shù)將消除系統(tǒng)級瓶頸,以推進最復(fù)雜的半導(dǎo)體設(shè)計。SerDes 還有助于減少引腳、走線和電路板空間,從而降低成本。超大規(guī)模數(shù)據(jù)中心的機架可能包含數(shù)以萬計的 SerDes 鏈路。

根據(jù)他們提供的數(shù)據(jù),新的并行芯片到芯片互連可實現(xiàn)高達 240 Tbps 的聚合數(shù)據(jù)傳輸,比多芯片封裝應(yīng)用的可用替代方案快 45%。換句話說,互連傳輸速率相當于每秒下載 10,000 部高清電影,盡管距離只有幾毫米或更短。

Marvell 將其 SerDes 和互連技術(shù)整合到其旗艦硅解決方案中,包括Teralynx開關(guān)_,PAM4和相干DSP,Alaska 以太網(wǎng)物理層 (PHY)設(shè)備,OCTEON處理器_,Bravera存儲控制器,Brightlane汽車以太網(wǎng)芯片組和定制 ASIC。而轉(zhuǎn)向 3nm 工藝使工程師能夠降低芯片和計算系統(tǒng)的成本和功耗,同時保持信號完整性和性能。

3nm,臺積電的新里程碑

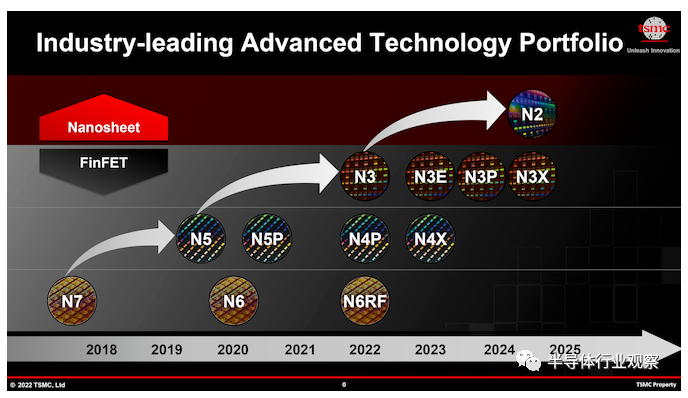

據(jù)臺積電介紹,公司的3奈米(N3)制程技術(shù)將是5奈米(N5)制程技術(shù)之后的另一個全世代制程,在N3制程技術(shù)推出時將會是業(yè)界最先進的制程技術(shù),具備最佳的PPA及電晶體技術(shù)。相較于N5制程技術(shù),N3制程技術(shù)的邏輯密度將增加約70%,在相同功耗下速度提升10-15%,或者在相同速度下功耗降低25-30%。

不過,N3 的工藝窗口(產(chǎn)生定義結(jié)果的參數(shù)范圍)相對較窄,就產(chǎn)量而言可能并不適合所有應(yīng)用。而且,隨著制造工藝變得越來越復(fù)雜,它們的尋路、研究和開發(fā)時間也越來越長,所以我們不再看到臺積電和其他代工廠每兩年出現(xiàn)一個全新的節(jié)點。對于 N3,臺積電的新節(jié)點導(dǎo)入周期將延長至 2.5 年左右。這意味著臺積電將需要提供 N3 的增強版本,以滿足其客戶的需求,這些客戶仍在尋求每瓦性能的改進以及每年左右晶體管密度的提升。

在2022 年技術(shù)研討會上,臺積電也討論了四種 N3 衍生制造工藝(總共五個 3 納米級節(jié)點)——N3E、N3P、N3S 和 N3X——這都將在未來幾年推出。這些 N3 變體旨在為超高性能應(yīng)用提供改進的工藝窗口、更高的性能、更高的晶體管密度和增強的電壓。

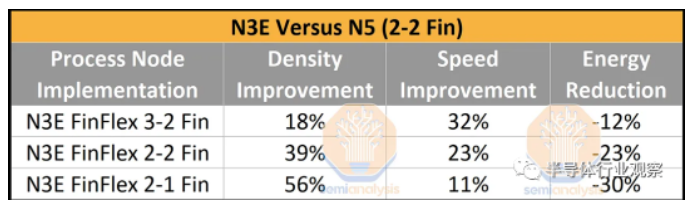

其中N3E 提高了性能,降低了功耗,并增加了工藝窗口,從而提高了亮了。但代價是該節(jié)點的邏輯密度略有降低。與 N5 相比,N3E 的功耗將降低 34%(在相同的速度和復(fù)雜度下)或 18% 的性能提升(在相同的功率和復(fù)雜度下),并將邏輯晶體管密度提高 1.6 倍。

根據(jù)報道,臺積電將在 2024 年左右的某個時候推出 N3P(其制造工藝的性能增強版本)以及 N3S(該節(jié)點的密度增強版本)。但臺積電目前并未透露這些變體的更多信息。對于那些無論功耗和成本都需要超高性能的客戶,臺積電將提供N3X,本質(zhì)上是N4X的思想繼承者。同樣,臺積電沒有透露有關(guān)該節(jié)點的詳細信息,只是說它將支持高驅(qū)動電流和電壓。

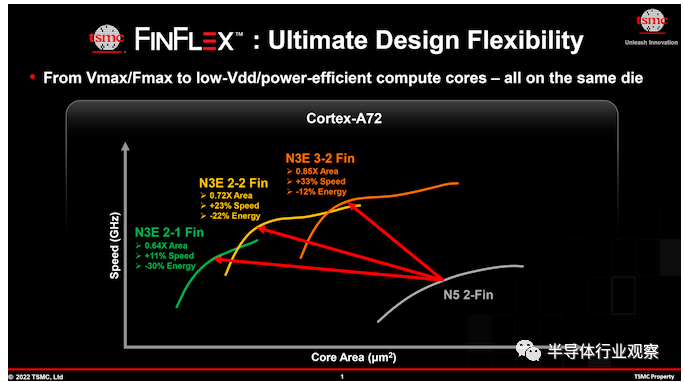

值得一提的是,臺積電所有這些技術(shù)都將支持 FinFlex,這是臺積電的一項“秘方”功能,可大大提高設(shè)計靈活性,并允許芯片設(shè)計人員精確優(yōu)化性能、功耗和成本。簡而言之,F(xiàn)inFlex 允許芯片設(shè)計人員精確定制他們的構(gòu)建模塊,以實現(xiàn)更高的性能、更高的密度和更低的功耗。

在實際應(yīng)用中,臺積電的 FinFlex 技術(shù)將允許芯片設(shè)計人員在一個塊內(nèi)混合和匹配不同類型的標準單元,以精確定制性能、功耗和面積。對于像 CPU 核心這樣的復(fù)雜結(jié)構(gòu),這種優(yōu)化提供了很多機會來提高核心性能,同時仍然優(yōu)化芯片尺寸。

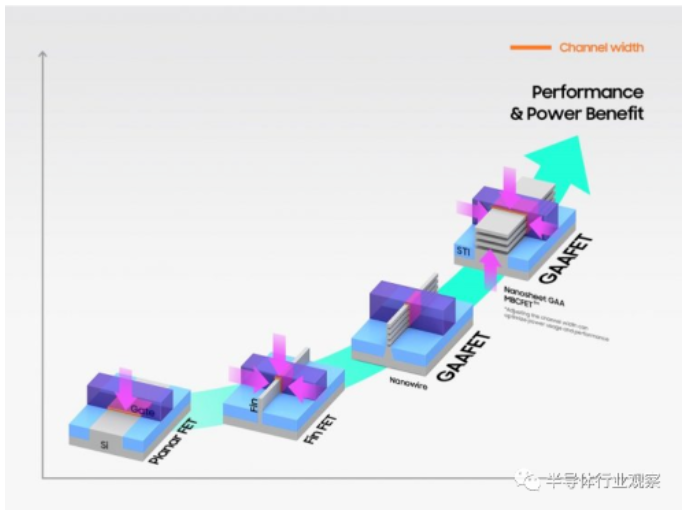

但是,我們必須強調(diào)的是,F(xiàn)inFlex 不能替代節(jié)點專業(yè)化(性能、密度、電壓),因為工藝技術(shù)比單一工藝技術(shù)中的庫或晶體管結(jié)構(gòu)有更大的差異,但 FinFlex 看起來是優(yōu)化性能、功率和成本的好方法臺積電的N3節(jié)點。最終,這項技術(shù)將使基于 FinFET 的節(jié)點的靈活性更接近于基于納米片/GAAFET 的節(jié)點,這些節(jié)點將提供可調(diào)節(jié)的通道寬度以獲得更高的性能或降低功耗。

三星3nm,起了個大早

其實早在臺積電公布3nm量產(chǎn)之前,三星早就宣布已經(jīng)實現(xiàn)了3nm工藝的量產(chǎn)。

2022年六月,三星宣布已開始了采用環(huán)柵 (GAA) 晶體管架構(gòu)的 3 納米 (nm) 工藝節(jié)點的初始生產(chǎn)。其中用到的多橋通道 FET (MBCFET ) 是三星首次采用的 GAA 技術(shù),該工藝突破了 FinFET 的性能限制,通過降低電源電壓水平提高功率效率,同時還通過增加驅(qū)動電流能力提高性能。該公司也正在開始將納米片晶體管與半導(dǎo)體芯片一起用于高性能、低功耗計算應(yīng)用,并計劃擴展到移動處理器。

三星表示,借助公司專有技術(shù)利用具有更寬通道的納米片,與使用具有更窄通道的納米線的 GAA 技術(shù)相比,可實現(xiàn)更高的性能和更高的能效。利用 3nm GAA 技術(shù),三星將能夠調(diào)整納米片的通道寬度,以優(yōu)化功耗和性能,以滿足各種客戶需求。

此外,GAA 的設(shè)計靈活性非常有利于設(shè)計技術(shù)協(xié)同優(yōu)化 (DTCO),這有助于提高功率、性能、面積 (PPA) 優(yōu)勢。與5nm工藝相比,第一代3nm工藝相比5nm功耗最高可降低45%,性能提升23%,面積減少16%,而第二代3nm工藝則功耗最高可降低50%,性能提高 30%,面積減少 35%。

如上所述,和臺積電的工藝不一樣,三星3nm采用了GAA晶體管,這開啟了一個新時代。

自 2019 年他們最初宣布該技術(shù)以來,三星一直致力于 3nm/GAAFET 技術(shù)的研發(fā)。三星特有的 GAA 晶體管技術(shù)是多橋通道 FET (MBCFET),這是一種基于納米片的實現(xiàn)。基于納米片的 FET 高度可定制,納米片的寬度是定義功率和性能特征的關(guān)鍵指標:寬度越大,性能越好(在更高功率下)。因此,專注于低功耗的晶體管設(shè)計可以使用更小的納米片,而需要更高性能的邏輯可以使用更寬的納米片。

在三星3nm被發(fā)布早期,業(yè)內(nèi)人士一直在詬病其良率,但據(jù)業(yè)內(nèi)人士在今年一月透露,三星電子公司周一大幅提高了其為無晶圓廠客戶生產(chǎn)的業(yè)界最先進的 3 納米芯片的良率。知情人士表示,三星的第一代 3 納米工藝節(jié)點的生產(chǎn)良率達到了“完美水平”,但他沒有進一步詳細說明。

而在此前,臺灣媒體報道稱,臺積電的3納米工藝生產(chǎn)良率高達85%,高于三星。但韓國業(yè)內(nèi)消息人士淡化了這份報告,稱這個數(shù)字似乎被夸大了。他們表示,考慮到臺積電向蘋果提供業(yè)界最小芯片的量產(chǎn)和交付時間表,其生產(chǎn)良率最多為50%。

按照媒體所說,因為在第一代3nm上折戟,三星正在大力投入到第二代工藝的研發(fā)中。

報告披露,三星第二代3nm GAA 工藝將會在2024年量產(chǎn),工藝將加入MBCFET 架構(gòu),性能也將提升不少。雖然三星并沒有分享4nm 節(jié)點的統(tǒng)計差異,但與該公司5nm 工藝相比,第二代3nm GAA 仍有望降低多達50% 的功耗、提升30% 性能、以及減少35% 的晶片面積占用。

巨頭會師2納米,決戰(zhàn)

雖然三星和臺積電都在3nm上花了不少心思,但從過去的新聞和廠商的公告可以看到,似乎大家都對第一代的3nm工藝不感興趣。例如市場上一度傳言,蘋果會成為臺積電第一代3nm工藝的唯一客戶。不過,這家美國巨頭迄今都沒有公布其3nm產(chǎn)品。

由此可見,第一代3nm不被看好是業(yè)界共識了。但市場對工藝的追逐從目前看來,尚未停止。除了這兩家晶圓代工廠以外,據(jù)報道,英特爾也將在2023年年底推出其 3nm 工藝節(jié)點。而他們似乎也把目光定在了2nm。

屆時,英特爾的Intel 20A(2nm)將迎來Angstrom時代,利用GAA(RibbonFET)晶體管和PowerVia技術(shù)提高功率保持能力。英特爾的競爭對手臺積電將在 2025 年采用其2nm 節(jié)點的 GAA ,在芯片制造商遇到小型化極限時讓前者領(lǐng)先一步。再加上將于2025 年實現(xiàn) 2 納米原型線的日本新創(chuàng)企業(yè)Rapidus 和三星。

對芯片公司而言,如何面對芯片設(shè)計挑戰(zhàn)和成本挑戰(zhàn),會是未來他們未來多年的頭等大事。

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應(yīng)用-AET<<